本シリーズの第1部と第2部では、アナログ/デジタル・コンバータ(ADC)のノイズ特性を、その特徴や原因から測定方法や規定方法まで、詳しく説明しました。本シリーズの第3部では、第1部と第2部で得られた理論的な理解を現実の設計例に当てはめていきます。最終的に、「自分の設計に本当に必要なノイズ特性は何か?」という問いの答えに必要な知識を読者につけてもらい、次のアプリケーションでは自信を持ってADCを選択できるようになることが目標です。

システム仕様

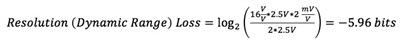

まず初めの例では、アプリケーションのシステム仕様を定義し、この仕様を目標となるノイズ特性パラメータに変換し、この情報を使って候補となるADCを比較します。図1に示すような4線式抵抗性ブリッジを使用する重量計アプリケーションを一例として分析しましょう。

図1:標準的な4線式抵抗性ブリッジ

システム仕様について、感度が2mV/Vで励起電圧が2.5Vのブリッジを想定し、5サンプル/秒(SPS)でサンプリングするとします。これにより5mVの最大出力電圧を供給し、これは最大適用重量1kgに相当します。また、最小適用重量50mgを分解できるように想定します。表1は、パラメータの概要です。

|

パラメータ |

システム仕様 |

|

ブリッジ感度 |

2mV/V |

|

励起/基準電圧 |

2.5V |

|

出力データレート |

5SPS |

|

最大適用重量 |

1kg |

|

最小適用重量 |

50mg |

表1:設計システム仕様の例

システム仕様が設定できたので、これを活用して、ADCを選択できるように一般のノイズ・パラメータに変換しましょう。

システム・ノイズ・パラメータの定義

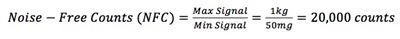

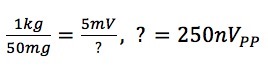

本シリーズの第2部では、システム・ノイズ・パラメータの定義とADCの選択には、入力換算ノイズを使用することを推奨しましたが、今回は、ノイズフリー・カウントとノイズフリー分解能を使用する、より一般的な方法から始めましょう。そうすれば、この方法と入力換算ノイズを直接使用する方法を比較できます。式1と式2では、初期ノイズ・パラメータを計算します。

必要なノイズフリー分解能が14.3ビットの場合、16ビットADCで十分だと、直ぐに�����してしまうかもしれません。しかし、第2部で述べた���うに、高分解能デルタ-シグマADCのノイズフリー分解能は、実際にはADCのフルスケール範囲のパーセンテージ使用率に左右されます。この例では、システムは2.5Vの基準電圧を使用し、最大入力信号は、励起電圧(2.5V)とブリッジ感度(2mV/V)の積です。式3に、第2部の式2を使用した予想分解能損失を示します。

これは驚くべき結果です。利用可能なフルスケール範囲の0.1%しか使用していないため、分解能をほとんど10ビットも失うことになります。このレベルでは、システム要件を満たすには24ビットADCでも不十分です。この問題を解決するには、システム仕様を変更するか入力信号を増幅するかして、パーセンテージ使用率を上げる��要があります。システム要件にはほとんどタッチできないと仮定すると、残された方法は入力ゲインを上げることです。それによって信号チェーンのノイズ特性が決定的に変化します。

幸いにも、増幅器のノイズがシステム性能にどのように影響するかを詳しく理解しなくても、分析を続けることができます。代わりに、これまでの知識を活用し、システム要件を満たすかどうかを判断するために、プログラマブル・ゲイン・アンプ(PGA)を内蔵したADCのデータシートのノイズ表を分析できます。

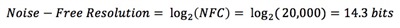

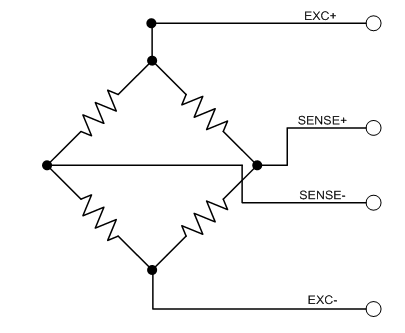

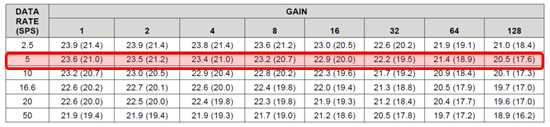

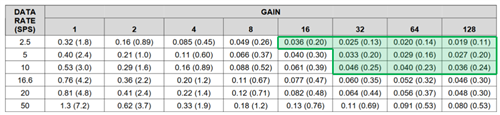

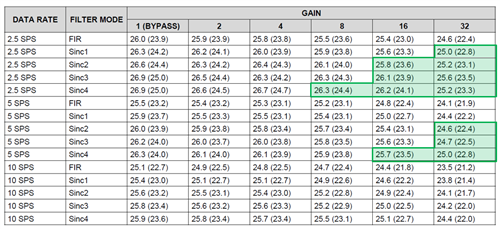

例えば、図2は、24ビットの『ADS124S08』の最大50SPSまでの有効分解能とノイズフリー分解能の表です。目標データレートは強調表示されています。 『ADS124S08』のゲインは1V/Vから最大128V/Vです。

図2:『ADS124S08』の有効分解能(ノイズフリー分解能)– AVDD = 3.3V、AVSS = 0V、PGA有効、グローバル・チョッピング無効、内部基準電圧2.5VでのSinc3フィルタ

このADCがシステム要件を満たすかどうかを判断するには、パーセンテージ使用率がゲインごとに異なることから、各ゲイン設定で別個に予想分解能損失を再計算する必要があります。そして、この結果を図2の対応するそれぞれのノイズフリー分解能値に加算し、システム仕様を満たすかどうかを確認する必要があります。表2に、『ADS124S08』を5SPSデータレートで使用したときの、算出されたシステム・ノイズフリー分解能(ビット単位)の一覧をまとめます。

|

Data rate |

Gain |

|||||||

|

1 |

2 |

4 |

8 |

16 |

32 |

64 |

128 |

|

|

5SPS |

11.03 |

12.23 |

13.03 |

13.73 |

14.03 |

14.53 |

14.93 |

14.63 |

表2:『ADS124S08』を使用した予想ノイズフリー分解能(ビット)

表2から、5SPSで32、64または128V/Vのゲインを使用した場合にのみ、必要なシステム・ノイズフリー分解能である14.3ビットを達成できることがわかります。図3は、これらの値を強調表示したデータシートのノイズ表です。

図3:『ADS124S08』を5SPSデータレートで使用したときのシステム要件を満たすゲイン設定

図3からわかる1つの重要なポイントは、計算をいくつも行わずにデータシートの値とシステム・ノイズ・パラメータを結びつける単純な方法はないということです。今は、結果が出ているので、このことはそれほど問題ないかもしれませんが、システム仕様が突然変更されたらどうなるでしょうか。

励起(基準)電圧を2.5Vから5Vに上げることにしたと仮定してください。ブリッジ感度も20mV/Vに増やすとします(これは、最大ゲイン設定はADCの範囲を超えてしまうので使えないことを意味します)。また、5SPSではなく、20SPSでのサンプリングも検討しています。このような変更は、ADCノイズ分析にどのように影響するでしょうか。

この答えを出すには、新しいデータレートと基準電圧でのそれぞれのゲイン設定に対して分解能損失を計算し直さなくてはならないでしょう。さらに、5Vの基準電圧に基づいて図2の表を作り直さなければなりません。なぜなら、この表の計算には2.5Vの基準電圧が使われているからです。最後に、算出した分解能損失を、5Vの基準電圧を使って作成されたノイズフリー分解能の表から減算して、表2を作り直さなければなりません。

確かにこれは大変な作業です。その理由は、ノイズフリー分解能が相対パラメータだからです。ここで、第2部で推奨したように絶対ノイズ・パラメータの使用に切り替えて、分析の仕方がどう変わるか見てみましょう。

入力換算ノイズの使用

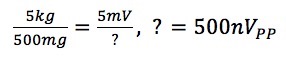

ノイズフリー分解能と同様に、ブリッジに必要な入力換算ノイズを判断するためには、システム仕様についていくつかのことがわかっていれば十分です。その最大出力信号がわかっていなければなりませんが、これは5mVです。また、最大信号に相当する重量もわかっていなければなりませんが、これは1kgです。最後に必要なのは最小適用重量ですが、これは50mgです。このようなわずかな情報があれば、式4を使用して、ADCが250nVのピーク・ツー・ピーク信号を分解できる必要があることがわかります。

入力換算ノイズを使用するメリットの1つは、分解能損失の計算を気にしなくてもいいことです。その代わりに、計算値をADCの入力換算ノイズ表と直接比較し、設定のどの組み合わせが求めるノイズ特性以下になるかを判断できます。

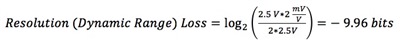

図4は、簡略版の『ADS124S08』の入力換算ノイズ表です。250nVPP以下の入力換算ノイズになるゲインとデータレートの設定の組み合わせが強調表示されています。

図4:『ADS124S08』を使用した250nVPP以下になるデータレートとゲインの組み合わせ(注:表の値は2.5Vの基準電圧を使用した“ノイズµVRMS(µVPP)”を示す)

図4の結果と図3のノイズフリー分解能を使用した分析とを比較すると、図4ではシステム要件を満たす『ADS124S08』設定の範囲がすべて得られることがわかるでしょう。図3では決まったデータレートでの値しか得られず、データレートが変われば計算し直す必要があるため、システム仕様の変更に簡単には適応できません。

システム変更の影響

式5に示すように、最大適用重量を5kg、最小適用重量を500mgに増やし、ブリッジの最大出力信号は5mVのままにするとします。

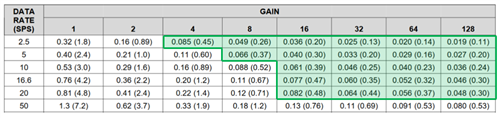

簡単な計算で、システム・ノイズ要件が500nVPPに緩和されたことがわかります。これにより、利用可能なデータレートとゲインの組み合わせが増えます。図5は、これらの緩和されたシステム仕様により、前提条件のノイズ特性を達成しながら、サンプリングの速度を上げるか(最大20SPS)ゲインを下げる(最小4V/V)ことが可能になることを示しています。

図5:『ADS124S08』を使用した500nVPP以下になるデータレートとゲインの組み合わせ(注:表の値は2.5Vの基準電圧を使用した“ノイズµVRMS(µVPP)”を示す)

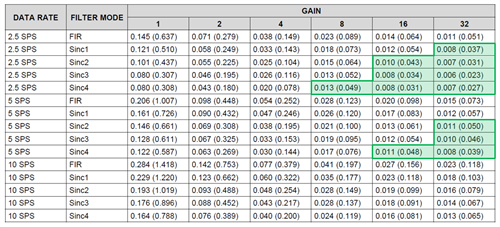

代わりに、重量計システムにさらに分解能が必要になったらどうなるでしょうか。例えば、5kgの最大適用重量の要件はそのままで、最小適用重量を最初の例の50mgに戻すとします。最大ブリッジ出力は同じまま(5mV)にしますが、50nVPPの入力換算ノイズが要求されることになります。これは非常に低い値です。図4と図5を見ると明らかですが、このレベルの性能を得られる『ADS124S08』のデータレートとゲイン設定の組み合わせはありません。しかし、どのADCにでも簡単にこの同じ分析を行えるため、単にノイズ特性がより高い製品を選択すればよいだけです。

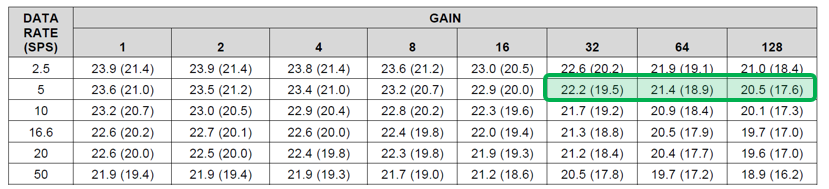

図6は32ビットADCである『ADS1262』のノイズ表です。このADCは機能的に『ADS124S08』と似ていますが、より高いノイズ特性を持っています。緑で塗りつぶした部分は、50nVPP以下の入力換算ノイズが得られるデータレートとノイズの組み合わせを示しており、ADS1262がシステム変更後の分解能要件を満たすことを裏付けます。

図6:『ADS1262』を使用した50nVPP以下になるデータレートとゲインの組み合わせ(注:表の値は2.5Vの基準電圧を使用した“ノイズµVRMS(µVPP)”を示す)

入力換算ノイズの結果を相対パラメータと比べてみましょう。図7で強調表示した部分は、図6と同じデータレートとゲインの組み合わせでの『ADS1262』のノイズフリー分解能性能です。

図7:5Vの基準電圧で『ADS1262』を使用した、50nVPP以下に対応する有効(ノイズフリー)分解能

第2部で、多くのエンジニアが無駄にノイズフリー分解能(ダイナミック・レンジ)を最大化しようと考えていると指摘しました。システムで必要な5SPSデータレートのときに、強調表示された最大値からシステムのノイズフリー分解能を計算して、このポイントを検討してみましょう。図7では、この値は23.5ビットであり、Sinc4フィルタを使用してゲインが16V/Vのときに得られます。

図7の表題に、システム仕様の2.5Vではなく5Vの基準電圧を表の計算に使用すると書かれていることを思い出してください。この差を埋めるには、図6の分解能の値それぞれを1ビットずつ減らさなければなりません。つまり、ある特定の条件で最大で22.5ビットのノイズフリー分解能しか期待できないということです。ここで、これらの設定のときの『ADS1262』の予想分解能損失を計算できます。

式6の結果を使用すると、システムのノイズフリー分解能は32ビットADC使用時に16.5ビットしかありません。

多くの人にとって、これはがっかりするような結果です。実際には得られないADCの性能にお金を払っているのではないかという懸念が当たっているように思えます。しかし、図6で同じ設定を見ると、実際には特定の条件のときに48nVPPノイズをうまく活用していることに気づくでしょう。これは、16ビットADCはもちろん、ほとんどの24ビットADCでも得られない非常に小さい値です。

最終的に、これが私の主張したいポイントです。システムで超低ノイズ特性が必要とされるため、16.5ビットのノイズフリー分解能(ダイナミック・レンジ)を達成するには、このような高分解能ADCが必要です。このようなことから、システム性能を定義し、ADCの選択に入力換算ノイズを使用することが理に適っているのです。

「信号の分解」シリーズの次の回では、有効ノイズ帯域幅を詳しく説明し、システムに入るノイズの量を確認する方法やノイズ帯域幅を制限する方法などのトピックを掘り下げる予定です。

著者紹介

ブライアン・リゾン(Bryan Lizon)

テキサス・インスツルメンツ 高精度ADC製品プロダクト・マーケティング・エンジニア