電磁干渉(EMI)は、車載用電源の最終製品における恒常的な課題です。マイルド・ハイブリッド電気自動車(MHEV)ソリューションが台頭するにつれ、システム内の多くの電子回路でバッテリ電圧が12Vから48Vへと移行していることから、EMIは以前にも増して難しい課題となっています。

車載用回路を設計しているエンジニアの大部分は、フィルタ設計、レイアウト・ガイドライン、およびスペクトラム拡散やフリップチップ・パッケージなどを始めとする多数の管理機能を通じて、EMIを低減させる方法を知っています。しかし、あまり知られていない情報として、降圧コンバータ(およびその他のトポロジ)におけるEMIを、基板を設計し直すことなく大幅に向上させるのに役立つヒントがいくつかあります。それらのヒントが、10分でEMIテストに合格するか、それとも基板を一から設計し直す必要があるかの分岐点となるかもしれません。

以下のEMIに関する3つの単純なヒントを参考にして、不要なプリント基板(PCB)リビジョンを回避しましょう

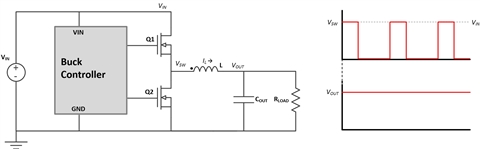

図1:降圧回路の概略回路図(左)と波形(右側)

ヒント1:パワー・インダクタを回転させる

降圧コンバータでは、スイッチング波形(スイッチ・ノード:VSW)をDC波形(出力電圧:VOUT)に変換するために、インダクタ-コンデンサ・フィルタが使用されています。図1は、降圧回路の概略回路図です。

図1に示す通り、インダクタ端子のうち1つがVSWに接続されており、それによってEMIノイズが発生します。このノードの電圧は早いエッジを持つ矩形波で、0Vからバッテリ電圧までスイングしています。一部のMHEV設計では、これが最大で48Vに達することがあります。もう一方の端子はVOUTに接続され、EMIに関しては電気的に静かな、DCに近い状態となっています。適切なPCBレイアウト手法では、グランド・プレーンへの容量性結合を低減するためにスイッチ・ノード表面積を最小限に抑えることが必要です。そうしないと、大きな同相ノイズが発生し、EMI性能の低下につながります。これと同じ容量性結合の低減策をインダクタに適用することができます。EMI性能は、インダクタの構造と向きに応じて変化します。

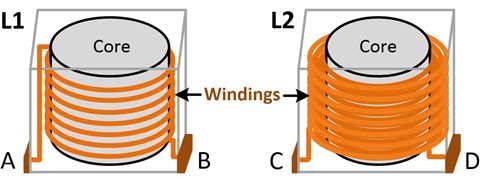

パワー・インダクタは、図2に示すように、基本的にはコア材料にワイヤを巻き付けただけのものです。単層で上から下まで巻き付けることも、複数層にわたって巻線を重ねることもできますが、この分析で重要なのは、インダクタの2つの端子が完全に対称になることは絶対にないという点です。インダクタを単純に180度回転させると、高ノイズのスイッチ・ノードに接続されるインダクタ端子が入れ替わります。これにより、EMIの結果も異なるものになります。

図2:インダクタ構造の概略 - 単層(左)と複数層(右)

単層インダクタの容量性結合は、ノイズの多いスイッチ・ノードを下から巻き付けが開始されている端子(図2、L1の端子B)に接続することによって低減できます。巻線の下部は基板に対して物理的に近い位置にあるので、巻線の上部に接続されている端子に比べて、基板上のGNDプレーンによるシールド効果がより多く得られます。複数層インダクタの容量性結合を低減するには、ノイズの多いスイッチ・ノードを内側の層から巻き付けが開始されている端子(図2、L2の端子D)に接続します。そのようにすれば、コイルの高ノイズ部分が、巻線の外側にあるコイルの低ノイズVOUT部分によって効果的にシールドされます。

回路図(図1、L)上に点で示された端子は、一般にコイル内側の巻線の開始位置を表しています。これが、EMI低減のためにスイッチ・ノードに接続すべき端子です。このように点で示す方法がすべてのベンダー、すべてのインダクタで採用されているわけではありませんが、結果が改善するかどうかは、単純にインダク��を180度回転させてみれば確認できます。

結果:テキサス・インスツルメンツの『LMR33630-Q1』を使用した13.5VIN、5VOUT、3AOUT、400kHzの2層基板上でインダクタを回転させた結果、FM帯域で8dBµVの改善が見られました。平均値検波の結果は、108MHzで15dBµV(国際無線障害特別委員会[CISPR] 25 Class 5制限を3dBµV下回る値)から7dBµV(CISPR 25 Class 5制限を11dBµV下回る値)へと改善しています。

ヒント2:EMIフィルタの電源端子にあるコンデンサを取り除く

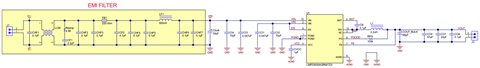

EMIフィルタは、インダクタとフェライト・ビーズで構成されることが多く、図3に示すように同相チョークが使用されていることもあります。これら3つの部品の前後や各部品間にはコンデンサが配置されます。多くの場合、フィルタの最初の部分には小型の高周波セラミック・コンデンサが配置され、降圧回路から最も遠い電源端子に接続されます(図3、CHF1)。考え方はシンプルで、コンデンサを追加することによって電源端子で発生するリップルを低減するというものです。これにより、通常は差動モードEMIが低下しますが、EMI性能の改善にはつながらない場合もあります。

図3に示す通り、CHF1(左端のコンデンサ)は、バッテリ-コンデンサ間を接続(バッテリからJ1に接続)しているハーネスの物理特性から生じる寄生インダクタンスによって、バッテリの+12VとGND(IN+とIN-)からの低抵抗パスを供給しています。インダクタンスと容量を持つ低抵抗パスは、インダクタンスと容量の積の平方根に反比例する角周波数で共振します。0.1µFのコンデンサが108MHz(FM帯域の上限であり、EMIテスト時に合格が難しい周波数として知られている)で共振するのに必要なインダクタンスは、たったの0.022nHです。

図3:EMIフィルタと『LMR33630-Q1』降圧コンバータを表す回路図の例

選択するコンデンサとレイアウトによっては、コンデンサを単純に取り除くだけで改善効果が得られることがあります。

結果:図3のCHF1を取り除いた結果、FM帯域内での平均値検波において3dBµV~5dBµVの改善が見られました。コンデンサが有効な場合もありますが、コンデンサを取り除くことによって高周波数での結果が改善することも多くあります。

ヒント3:負荷抵抗の配置を変更する

EMIテストでは、電源回路を標準的な入力電圧と最大出力電流で動作させます。テストには、コンバータをこの出力電力で動作させるために負荷が必要であり、通常は抵抗性の"ダミー"負荷を使用します(図1のRLOADを参照)。使用する負荷の種類(巻線抵抗や非誘導性抵抗など)、使用するヒート・シンク(大きなヒート・シンクは容量性結合のアンテナとして機能するが、ヒート・シンクが小さすぎると抵抗が過熱してテスト終了前に破損する可能性がある)、およびシールド処理(接地されたシールドは容量性結合を減らすが、熱気がたまるので必要な負荷/ヒート・シンクのサイズが増大する)について検討する必要があります。

負荷抵抗に関する検討事項には、他にも負荷抵抗をどのように出力に接続するのかという重要な側面があります。このヒントは、ヒント2に似ています。セラミック・コンデンサのみを使用した出力は、出力コンデンサから負荷への接続の寄生インダクタンスと共振することがあります。ダンピングがほとんどまたは全く行われていないと、この共振によってEMIテストに合格できなくなる可能性があります。この共振が大きなEMI源にならないようにする方法として最も簡単なのが、負荷を直接セラミック出力コンデンサにハンダ付けするという方法で、これにより寄生インダクタンスが最小限に抑えられて共振が減少、または問題の領域がより高い周波数にシフトします。いずれにしても、共振がEMIを引き起こしているかどうかは判明します。

結果:1つの基板上で負荷をVOUT端子から直接出力コンデンサへと移動した結果、FM帯域内の平均値検波において10dBµVの改善が見られました。つまり、結果は22dBµV(制限を4dBµV上回る値)から12dBµV(制限を6dBµV下回る値)へと改善しました。

結論

EMIの低減手法は、科学的かつ技術的な手法です。EMI関連のベスト・プラクティスについては、数多くの記事、アプリケーション・ノート、およびトレーニング資料があります。最初からテストに合格するよう最善を尽くして設計することも重要ですが、目的の基板が初回のテストで必ず合格するという保証はどこにもありません。だからこそ、設計に極端な変更を加えることなくEMIを改善するための戦略が重要になるのです。この記事で紹介したヒントは、実装に長い時間はかかりませんが、今すぐに合格するか、再設計と再テストに何時間もかけてから合格するかを決める分岐点となるかもしれません。これらのヒントを活用し、EMIを改善してテストに合格しましょう。

著者紹介

Sam Jaffe

テキサス・インスツルメンツ

広VIN 降圧コンバータおよびコントローラ部門

アプリケーション・エンジニア

※すべての登録商標および商標はそれぞれの所有者に帰属します。

※ご質問はE2E Support Forumにお願い致します。