# **C28x Digital Power Library**

**v3.2**

**March 2011**

## **Module User's Guide**

## **C28x Foundation Software**

## IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible or liable for any such use.

Resale of TI's products or services with *statements different from or beyond the parameters* stated by TI for that products or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: [Standard Terms and Conditions of Sale for Semiconductor Products](#).

[www.ti.com/sc/docs/stdterms.htm](http://www.ti.com/sc/docs/stdterms.htm)

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright ©2011, Texas Instruments Incorporated

## **Trademarks**

TMS320 is the trademark of Texas Instruments Incorporated.

All other trademarks mentioned herein are property of their respective companies

## **Acronyms**

DPLib: Digital Power library functions.

C28x: Refers to devices with the C28x CPU core.

IQmath: Fixed-point mathematical functions in C.

Q-math: Fixed point numeric format defining the binary resolution in bits.

# Contents

|                                                            |           |

|------------------------------------------------------------|-----------|

| <b>Chapter 1. Introduction .....</b>                       | <b>6</b>  |

| 1.1. Introduction.....                                     | 6         |

| <b>Chapter 2. Installing the DP Library.....</b>           | <b>8</b>  |

| 2.1. DP Library Package Contents .....                     | 8         |

| 2.2. How to Install the Digital Power Library .....        | 8         |

| 2.3. Naming Convention .....                               | 8         |

| <b>Chapter 3. Using the Digital Power Library.....</b>     | <b>10</b> |

| 3.1. Library Description and Overview .....                | 10        |

| 3.2. Steps to use the DP library .....                     | 12        |

| 3.3. Viewing DP CLA library variables in watch window..... | 14        |

| 3.4. IQ Math & IQ Math Library Usage.....                  | 15        |

| <b>Chapter 4. Module Summary .....</b>                     | <b>16</b> |

| 4.1. DP Library Function Summary .....                     | 16        |

| <b>Chapter 5. C28x Module Descriptions .....</b>           | <b>18</b> |

| 5.1. Controllers .....                                     | 18        |

| CNTL_2P2Z.....                                             | 18        |

| CNTL_3P3Z.....                                             | 23        |

| 5.2. Peripheral Configuration .....                        | 28        |

| PWM_PSFB_PCMC_CNF .....                                    | 28        |

| 5.3. Peripheral Drivers .....                              | 29        |

| ADCDRV_1ch.....                                            | 29        |

| ADCDRV_4ch.....                                            | 33        |

| ADCDRV_8ch.....                                            | 37        |

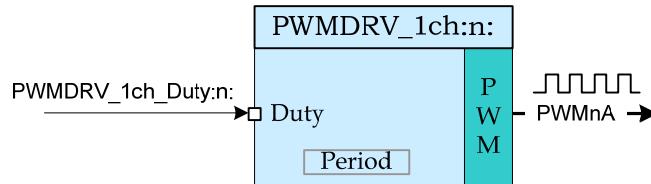

| PWMDRV_1ch .....                                           | 42        |

| PWMDRV_1chHiRes.....                                       | 46        |

| PWMDRV_PFC2PhiL.....                                       | 51        |

| PWMDRV_PSFB.....                                           | 55        |

| PWMDRV_ComplPairDB .....                                   | 59        |

| PWMDRV_DualUpDwnCnt .....                                  | 64        |

| PWMDRV_BuckBoost .....                                     | 68        |

| PWMDRV_2ch_UpCnt .....                                     | 73        |

| PWMDRV_1ch_UpDwnCnt .....                                  | 77        |

| PWMDRV_PSFB_VMC_SR.....                                    | 81        |

| PWMDRV_LLC_ComplPairDB.....                                | 85        |

| PWMDRV_LLC_1ch_UpCntDB .....                               | 90        |

| PWMDRV_LLC_1ch_UpCntDB_Compl .....                         | 95        |

| DACDRV_RAMP .....                                          | 101       |

| 5.4. Application Specific .....                            | 105       |

| PFC_ICMD .....                                             | 105       |

| PFC_INVSQR.....                                            | 108       |

| PFC_BL_ICMD .....                                          | 111       |

| PFC_InvRmsSqr.....                                         | 115       |

|                                         |            |

|-----------------------------------------|------------|

| <b>5.4 Math Blocks .....</b>            | <b>119</b> |

| MATH_EMAVG .....                        | 119        |

| SineAnalyzer.....                       | 123        |

| <b>Utilities .....</b>                  | <b>128</b> |

| DLOG_4ch.....                           | 128        |

| DLOG_1ch.....                           | 132        |

| <b>Chapter 6. Revision History.....</b> | <b>135</b> |

# Chapter 1. Introduction

## 1.1. Introduction

Texas Instruments Digital Power (DP) library is designed to enable flexible and efficient coding of digital power supply applications using the C28x processor. An important consideration of these applications is their relatively high control loop rate, which imposes certain restrictions on the way the software can be written. In particular, the designer must take care to ensure the real-time portion of the code, normally contained within an Interrupt Service Routine (ISR), must execute in as few cycles as possible. In many cases this makes the use of C code impossible, or at least inadvisable, for the ISR.

A further requirement in code development and test is for the software structure to be flexible and adaptable. This enables the designer to experiment with various control loop layouts, and to monitor software variables at various points in the code to confirm correct operation of the system. For this reason, the DP library is constructed in a modular form, with macro functions encapsulated in re-usable code blocks which can be connected together to build any desired software structure.

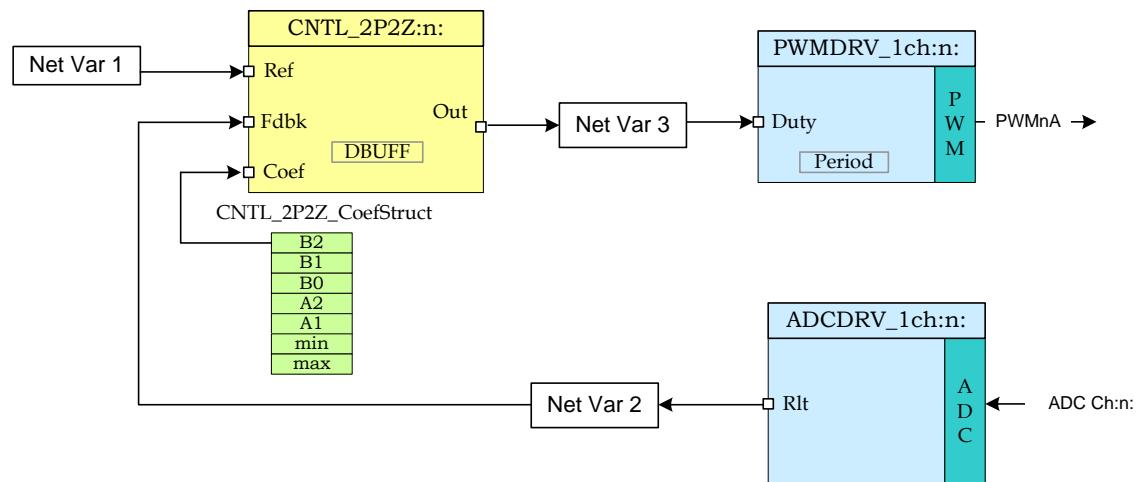

This strategy encourages the use of block diagrams to plan out the software structure before the code is written. An example of a simple block diagram showing the connection of three DP library modules to form a simple control loop is shown below.

Figure 1 Close Loop System using DPLib

In this example, three library macro-blocks are connected: an ADC driver, a second order digital controller, and a PWM driver. The labels “Net Var 1”, Net Var 2” and “Net Var 3” correspond to software variables which form the connection points, or “nodes”, in the diagram. The input and output terminals of each block are connected to these nodes by a simple method of C pointer assignment in software. In this way, designs may be rapidly re-configured to experiment with different software configurations.

Library blocks have been color coded: “turquoise” blocks represent those which interface to physical device hardware, such as an A/D converter, while “yellow” blocks indicate macros which are independent of hardware. This distinction is important, since hardware interface blocks must be configured to match only those features present on the device. In particular, care should be

taken to avoid creating blocks which access the same hardware (for example two blocks driving the same PWM output may well give undesirable results!).

Both types of blocks require initialization prior to use, and must be configured by connecting their terminals to the desired net nodes. The initialization and configuration process is described in Chapter 3.

Once the blocks have been initialized and connected, they can be executed by calling the appropriate code from an assembly ISR. Macro blocks execute sequentially, each block performing a precisely defined computation and delivering its' result to the appropriate net list variables, before the next block begins execution.

# Chapter 2. Installing the DP Library

## 2.1. DP Library Package Contents

The TI Digital Power library consists of the following components:

- C initialization functions

- Assembly macros files

- An assembly file containing a macro initialization function and a real-time run functions.

- An example CCS project showing the connection and use of DP library blocks.

- Documentation

## 2.2. How to Install the Digital Power Library

The DP library is distributed through the controlSUITE installer. The user must select the Digital Power Library Checkbox to install the library in the controlSUITE directory. By default, the installation places the library components in the following directory structure:

<base> install directory is C:\ti\controlSUITE\libs\app\_libs\digital\_power\<device>

...where <device> is the C28x platform. The following sub-directory structure is used:

|                |                                                    |

|----------------|----------------------------------------------------|

| <base>\asm     | Contains assembly macros                           |

| <base>\C       | C initialization files                             |

| <base>\doc     | Contains this file                                 |

| <base>\include | Contains the library header file for the "DPLib.h" |

The installation also installs a template project using the DPLib for the device inside the controlSUITE directory

controlSUITE\development\_kits\TemplateProjects\_<ver. No.>\

DPLibTemplate-<device\_name> \_<ver. No.>

These template projects can be quickly modified to start a new project using the DPLib.

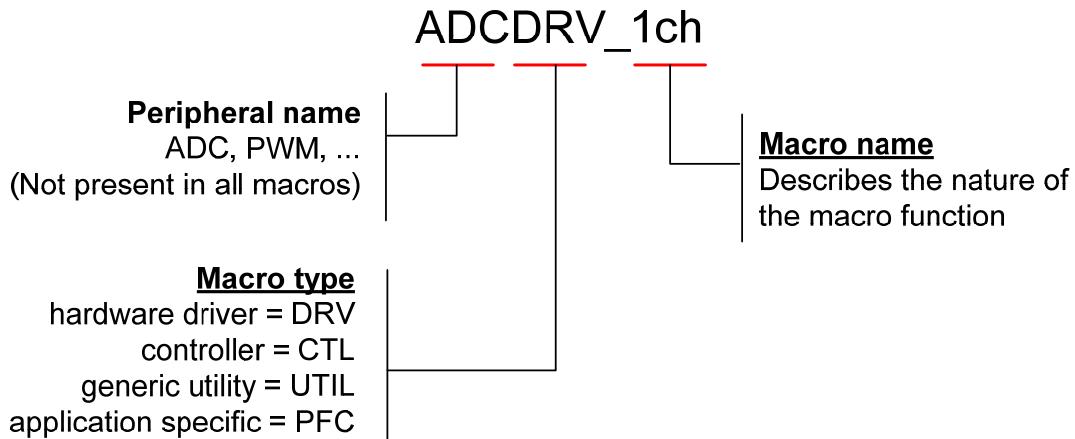

## 2.3. Naming Convention

Each macro of the digital power library has an assembly file that contains the initialization and the run time code for the block. In addition to the assembly block peripheral interface blocks use a peripheral configuration function as well.

An example of the naming convention used is shown below:

Figure 2 – Function Naming Convention

Include files, initialization functions, and execution macros share the same naming. In the above example, these would be...

Include file: `ADCDRV_1ch.asm`

Init function: `ADCDRV_1ch_INIT n`

Execution Macro: `ADCDRV_1ch n`

Where `n` refers to the instance number of the macro.

Note: In the case of some Peripheral Drivers (e.g. ADC Drivers and PWM drivers) the instance number also implies the Peripheral Number the DP Library macro would drive or use on the device. For example

`ADCDRV_1ch 0`      normalizes AdcResult0 of the ADC Peripheral &

`PWMDRV_1ch 3`      drives the EPWM3 peripheral present on the device.

# Chapter 3. Using the Digital Power Library

## 3.1. Library Description and Overview

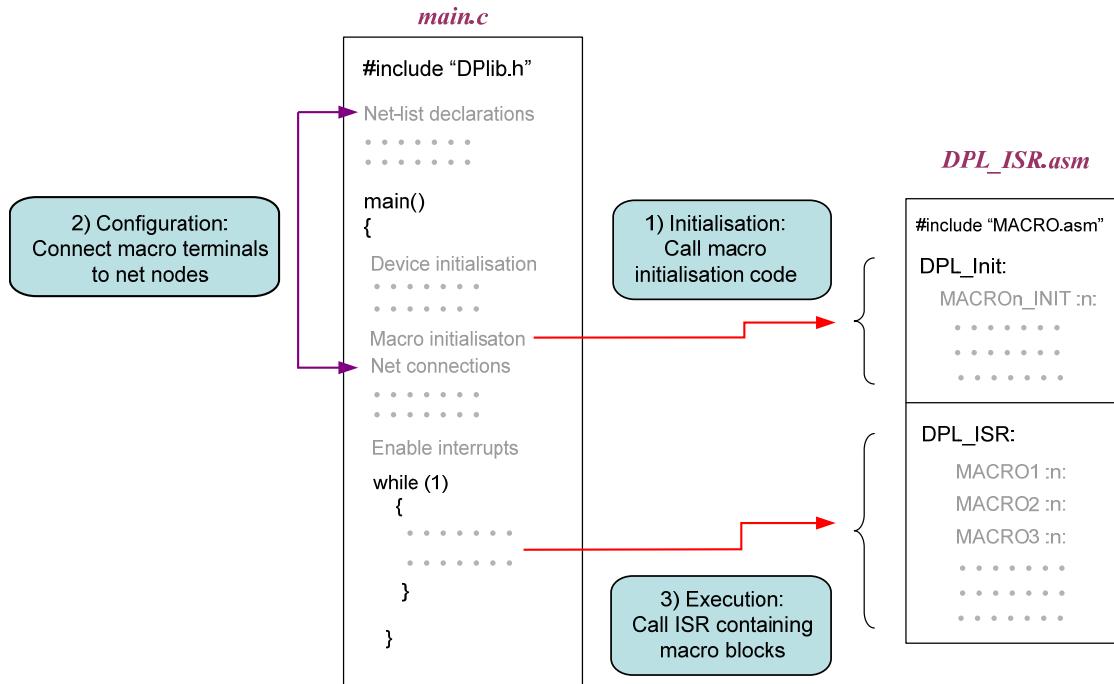

Typical user software will consist of a main framework file written in C and a single Interrupt Service Routine (ISR) written in assembly. The C framework contains code to configure the device hardware and initialize the library macros. The ISR consists of a list of optimized macro modules which execute sequentially each time a hardware trigger event occurs.

This structure of setting up an interrupt based program is common in embedded real-time systems which do not use a scheduler. For examples of device initialization code, refer to the peripheral header file examples for the C28x device.

Conceptually, the process of setting up and using the DP library can be broken down into three parts.

**1 *Initialisation*.** Macro blocks are initialized from the C environment using a C callable function (“DPL\_Init()”) which is contained in the assembly file `{ProjectName}-DPL-ISR.asm`. This function is prototyped in the library header file “`DPLib.h`” which must be included in the main C file.

**2 *Configuration*.** C pointers of the macro block terminals are assigned to net nodes to form the desired control structure. Net nodes are 32-bit integer variables declared in the C framework. Note names of these net nodes are no dependent on the macro block.

**3 *Execution*.** Macro block code is executed in the assembly ISR (“`DPL_ISR`”). This function is defined in the `“{ProjectName}-DPL-ISR.asm”`.

An example of this process and the relationship between the main C file and assembly ISR is shown below.

Figure 3 : Relation between Main.c & ISR.asm file

The DP library assembly code has a specific structure which has been designed to allow the user to freely specify the interconnection between blocks, while maintaining a high degree of code efficiency. Before any of the library macros can be called, they must be initialized using a short assembly routine located in the relevant `macro.asm` file for each module. The code which calls the macro initialization must reside in the same assembly file as the library ISR.

The assembly code in “`DPL_Init`” is C callable, and its’ prototype is in the library header file “`DPLib.h`” described above. To initialize the macros, edit the `DPL_Init` section of the file “`{ProjectName}-DPL-ISR.asm`” to add initialization calls for each macro required in the application. The order of the calls is not important, providing one call is made for each macro-block required in the application. The respective macro assembly file must be included at the starting of the “`{ProjectName}-DPL-ISR.asm`” file.

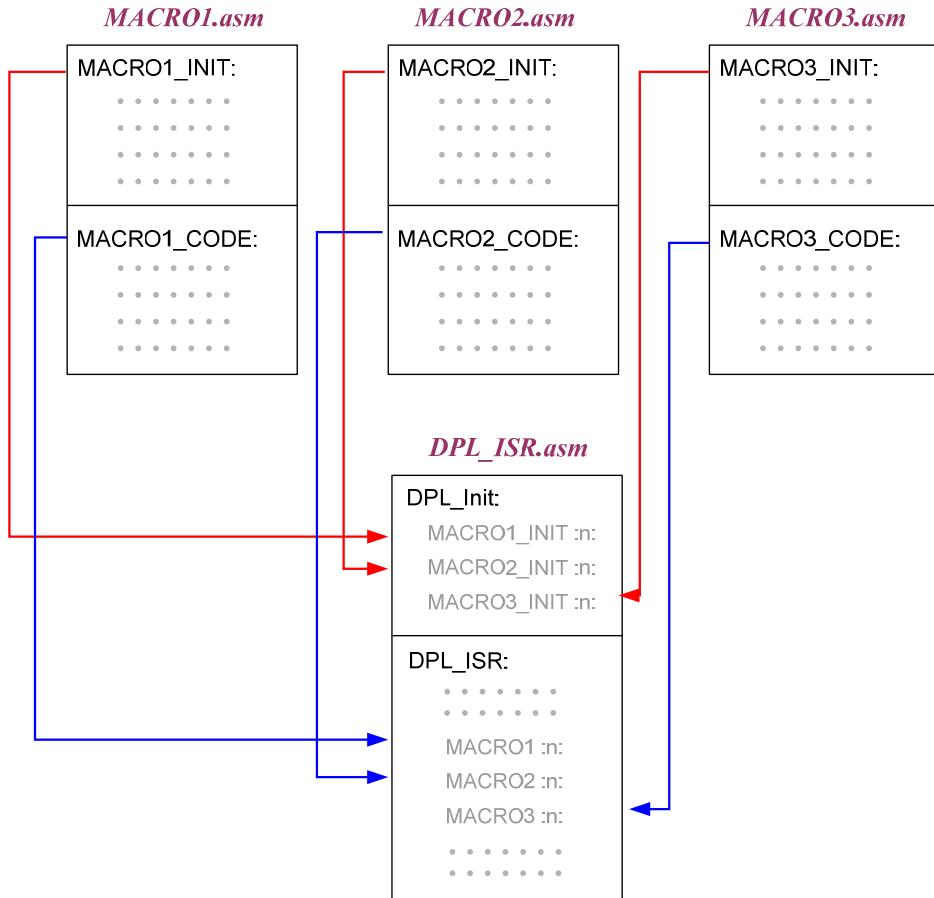

The internal layout and relationship between the ISR file and the various macro files is shown diagrammatically below. In this example, three DP library macros are being used. Each library module is contained in an assembly include file (.asm extension) which contains both initialization and macro code. The ISR file is also divided into two parts: one to initialize the macros, the other is the real-time ISR code in which the macro code is executed.

Figure 4 DP library assembly ISR and macro file

The ISR contains context save and context restore blocks to protect any registers used by the assembly modules. By default, the template performs a complete context save of all the main CPU registers. PUSH/POP instructions can be commented to save cycles if specific registers are known to be unused by any of the macros in the ISR. A list of registers used by each module is shown below.

### 3.2. Steps to use the DP library

The first task before using the DP library should be to sketch out in diagram form the modules and block topology required. The aim should be to produce a diagram similar to that in Figure 1. This will indicate which macro-blocks are required and how they interface with one another. Once this is known, the code can be configured as follows:

**Step 1 Add the library header file.** The C header file “DPLib.h” contains prototypes and variable declarations used by the library. Add the following line at the top of your main C file:

```

#include "DPLib.h"

```

This file is located in the at,

controlSUITE\libs\app\_libs\digital\_power\{device\_name\_VerNo}\include

This path needs to be added to the include path in the build options for the project.

**Step 2 Declare terminal pointers in C.** The “{ProjectName}-Main.c” file needs to be edited to add extern declarations to all the macro terminal pointers which will be needed in the application under the “DPLIB Net Terminals” section inside this file. In the example below, three pointers to an instance of the 2P2Z control block are referenced. Please note the use of volatile keyword for the net pointers, as they point to net variables which are volatile as the ISR computes these values.

```

// ----- DPLIB Net Pointers -----

// Declare net pointers that are used to connect the DP Lib Macros here

// CNTL_2P2Z #instance 1

extern volatile long      *CNTL_2P2Z_Ref1;

extern volatile long      *CNTL_2P2Z_Fdbk1;

extern volatile long      *CNTL_2P2Z_Out1;

extern volatile long      *CNTL_2P2Z_Coef1;

```

**Step 3 Declare signal net nodes/net variables in C.** Edit the “{ProjectName}-Main.c” C file to define the net variables which will be needed in the application under the “DPLIB Variables” section . In the example below, three arbitrarily named variables are declared as global variables in C.

```

// ----- DPLIB Variables -----

// Declare the net variables being used by the DP Lib Macro here

volatile long      Net1, Net2, Net3;

```

**Step 4 Call the Peripheral configuration function.** Call the peripheral configuration functions that are needed to configure the peripherals being used by the library macros being used in the system.

Note as CNTL\_2P2Z is a software block this step is not needed.

**Step 5 Call the initialisation function from C.** Call the initialization function from the C framework using the syntax below.

```

/* Digital Power (DP) library initialization */

DPL_Init();           // initialize DP library

```

**Step 6 Assign macro block terminals to net nodes.** This step connects macro blocks together via net nodes to form the desired control structure. The process is one of pointer assignment using the net node variables and terminal pointers declared in the previous two steps.

For example, to connect the ADC driver (instance 0) and 2P2Z control block (instance 1) to net node “Net2” as shown in Figure 1, the following assignment would be made:

```

// feedback node connections

ADCDRV_1ch_Rlt0 = &Net2;

CNTL_2P2Z_Fdbk1 = &Net2;

```

Note that net pointer assignment can be dynamic: *i.e.* the user code can change the connection between modules at run-time if desired. This allows the user to construct flexible and complex control topologies which adapt intelligently to changing system conditions.

**Step 7 Add the ISR file.** A single assembly file containing the ISR code and calls to the macro initialisation functions must exist in the project. The relationship between these elements is described in Chapter 3.1. A blank template “`ProjectName-DPL-ISR.asm`” is included with the DP library for this purpose in the template directory. To use this file, rename the file as “`{ProjectName}-DPL-ISR.asm`” and add it to the project.

**Step 8 Include the required macro header files.** Add assembly include files to the top of the ISR file “`{ProjectName}-DPL_ISR.asm`” as required. The include (.asm) file is required for each block type being used in the project. For example, to use the 2P2Z controller block, add this line to the top of the ISR file:

```

.include "CNTL_2P2Z.asm"

```

**Step 9 Initialize required macro blocks.** Edit the function “`DPL_Init`” in the above ISR file to add calls to the initialization code in each macro file. Each call is invoked with a number to identify the unique instance of that macro block. For example, to create an instance of the 2P2Z control block with the identifier “1”:

```

CNTL_2P2Z_INIT      1

```

**Step 10 Edit the assembly ISR to execute the macros in the required order.** Edit the function “`DPL_Run`” to add calls to the run time routine of each macro and instance being used in the system. In the example above the first instance of a 2P2Z control macro would be executed by:

```

CNTL_2P2Z      1

```

**Step 11 Add the DP library sections to the linker command file.** The linker places DP library code in named sections as specified in the linker command file “`{DeviceName}-RAM/FLASH-ProjectName.CMD`”. A sample CMD file is provided with the sections specified for the entire DPS library in the template folder. The file only provides a sample memory allocation and can be edited by the user to suit their application.

This DPLib Macros need to be placed in the data RAM. The sample linker file specifies where each memory section from each DP library module would be placed in internal memory. An example of section placement for the CNTL\_2P2Z module is shown below.

```

/* CNTL_2P2Z section */

CNTL_2P2Z_Section      : > dataRAM          PAGE = 1

CNTL_2P2Z_InternalData : > dataRAM          PAGE = 1

CNTL_2P2Z_Coeff         : > dataRAM          PAGE = 1

```

Where dataRAM is a location in the RAM on the device which is specified in the sample CMD file.

### 3.3. Viewing DP CLA library variables in watch window

If it is desired to see the DP CLA library macro variables, i.e. the net pointers can be added to the watch window by adding a qualifier of `*(type*)`. Shown below is the value stored in the net pointer `Ref`, and the net variable the pointer points to. Note the address of the net variable is stored in the net pointer.

| Watch (1)                               |              |                 |      |             |

|-----------------------------------------|--------------|-----------------|------|-------------|

| Name                                    | Value        | Address         | Type | Format      |

| <code>(*) Ref</code>                    | 0.1999999881 | 0x00008C50@Data | long | Q-Value(24) |

| <code>(*) *(long*)CNTL_2P2Z_Ref1</code> | 0x00008C50   | 0x00008E00@Data | long | Hexadecimal |

### 3.4. IQ Math & IQ Math Library Usage

The DPlib modules use a common Q24 value for the variables that interface to the net pointers of the macros. The modules assume and write to variables in Q24 format. Please see the module specific document for what range of Q24 values are supported at the terminals of the macros. Some variables that are local to the macro may be saved in Q30 or other Q format to save resolution.

The DP Lib does not use IQ Math Library for its functions and macros. However IQMath library is used in the code snippets given in this file for ease of readability of the code. For example reference variable can be written with a value of 0.2 in Q24 in the following two fashion, both of which write the same value to the variable.

```

Ref    = _IQ24(0.2);      //Uses IQ Math Library

Ref    = 0x333333;        //Does not use IQMath Library

```

# Chapter 4. Module Summary

## 4.1. DP Library Function Summary

The Digital Power Library consists modules than enable the user to implement digital control for different power topologies. The following table lists the modules existing in the power library and a summary of cycle counts and code size.

**Note:** The memory sizes are given in 16-bit words and cycles are the system clock cycles taken to execute the Macro run file.

| Module Name         | Module Type | Description                                                                         | HW Config File | Cycles | Init Code Size (W) | Run Code Size (W) | Data Size (W) | Multiple Instance Support |

|---------------------|-------------|-------------------------------------------------------------------------------------|----------------|--------|--------------------|-------------------|---------------|---------------------------|

| CNTL_2P2Z           | CNTL        | Second Order Control Law                                                            | NA             | 34     | 17                 | 46                | 18            | Yes                       |

| CNTL_3P3Z           | CNTL        | Third Order Control Law                                                             | NA             | 42     | 17                 | 56                | 22            | Yes                       |

| ADCDRV_1ch          | HW          | Single Channel ADC Driver                                                           | Yes            | 5      | 5                  | 8                 | 2             | Yes                       |

| ADCDRV_4ch          | HW          | Four Channel ADC Driver                                                             | Yes            | 14     | 8                  | 20                | 8             | No                        |

| PWMDRV_1ch          | HW          | Single Channel PWM Driver                                                           | Yes            | 10     | 12                 | 12                | 4             | Yes                       |

| PWMDRV_1chHiRes     | HW          | Single Channel PWM Driver with Hi Res capability                                    | Yes            | 10     | 12                 | 12                | 4             | Yes                       |

| PWMDRV_PFC2PhiL     | HW          | PWM driver for Two Phase Interleaved PFC stage                                      | Yes            | 17     | 13                 | 18                | 6             | Yes                       |

| PWMDRV_PSFB         | HW          | PWM driver for Phase Shifted Full Bridge Power stage                                | Yes            | 21     | 13                 | 21                | 6             | Yes                       |

| PWMDRV_ComplPairDB  | HW          | PWM driver for complimentary pair PWMs                                              | Yes            | 10     | 15                 | 12                | 6             | Yes                       |

| PWMDRV_DualUpDwnCnt | HW          | PWM driver with independent duty control on ch A and ch B, using up down count mode | Yes            | 14     | 13                 | 16                | 6             | Yes                       |

| PWMDRV_BuckBoost    | HW          | PWM driver for a four switch Buck Boost Stage                                       | Yes            | 12     | 12                 | 16                | 4             | Yes                       |

| PWMDRV_2ch_UpCnt    | HW          | PWM driver with independent duty control on ch A and ch B, using up down count mode | Yes            | 13     | 12                 | 16                | 6             | Yes                       |

| PFC_ICMD            | APPL        | Power Factor Correction Current Command Block                                       | NA             | 17     | 9                  | 19                | 10            | Yes                       |

| PFC_INVSQR          | APPL        | Power Factor                                                                        | NA             | 71     | 15                 | 39                | 12            | Yes                       |

|            |      |                                 |    |          |    |    |    |     |

|------------|------|---------------------------------|----|----------|----|----|----|-----|

|            |      | Correction Inverse Square Block |    |          |    |    |    |     |

| MATH_EMAVG | MATH | Exponential moving average      | NA | 16       | 6  | 16 | 6  | Yes |

| DLOG_4ch   | UTIL | 4 channel Data Logger Module    | NA | 33 (Avg) | 14 | 56 | 24 | No  |

| DLOG_1ch   | UTIL | 1 channel Data Logger Module    | NA | 20 (Avg) | 17 | 41 | 12 | Yes |

# Chapter 5. C28x Module Descriptions

## 5.1. Controllers

### CNTL\_2P2Z

### Two Pole Two Zero Controller

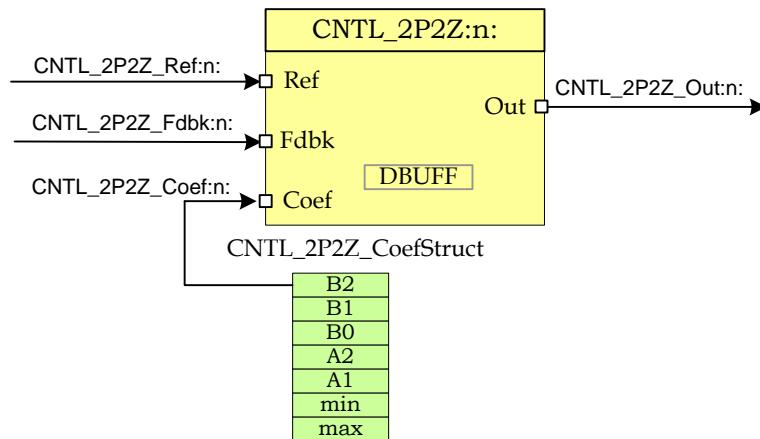

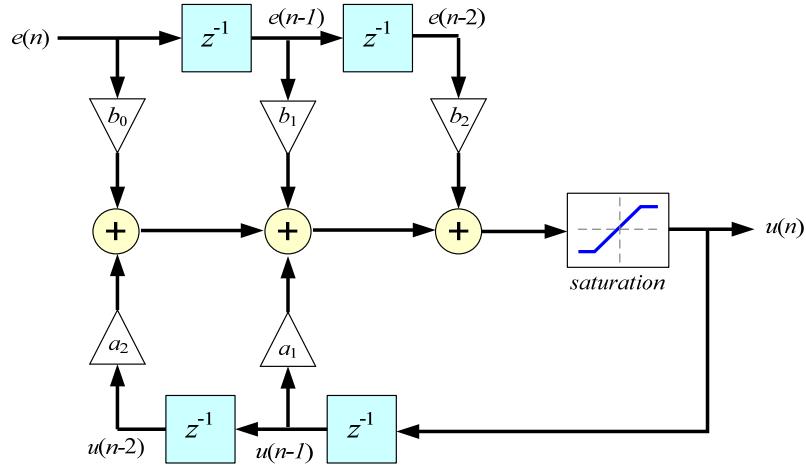

**Description:** This assembly macro implements a second order control law using a 2-pole, 2-zero construction. The code implementation is a second order IIR filter with programmable output saturation.

**Macro File:** CNTL\_2P2Z.asm

**Module Description:** The 2-pole 2-zero control block implements a second order control law using an IIR filter structure with programmable output saturation. This type of controller requires two delay lines: one for input data and one for output data, each consisting of two elements.

The discrete transfer function for the basic 2P2Z control law is...

$$\frac{U(z)}{E(z)} = \frac{b_2 z^{-2} + b_1 z^{-1} + b_0}{1 - a_1 z^{-1} - a_2 z^{-2}}$$

This may be expressed in difference equation form as:

$$u(n) = a_1 u(n-1) + a_2 u(n-2) + b_0 e(n) + b_1 e(n-1) + b_2 e(n-2)$$

Where...

$u(n)$  = present controller output (after saturation)

$u(n-1)$  = controller output on previous cycle

$u(n-2)$  = controller output two cycles previously

$e(n)$  = present controller input

$e(n-1)$  = controller input on previous cycle

$e(n-2)$  = controller input two cycles previously

The 2P2Z control law may be represented graphically as shown below.

Input and output data are located in internal RAM with address designated by `CNTL_2P2Z_DBUFF` as shown below. Note that to preserve maximum resolution the module saves the values inside `CNTL_2P2Z_DBUFF` in `_IQ30` format.

`CNTL_2P2Z_DBUFF`

|   |          |

|---|----------|

| 0 | $u(n-1)$ |

| 2 | $u(n-2)$ |

| 4 | $e(n)$   |

| 6 | $e(n-1)$ |

| 8 | $e(n-2)$ |

Controller coefficients and saturation settings are located in memory as follows:

`CNTL_2P2Z_CoeffStruct`

|                    |

|--------------------|

| $_IQ26(b_2)$       |

| $_IQ26(b_1)$       |

| $_IQ26(b_0)$       |

| $_IQ26(a_2)$       |

| $_IQ26(a_1)$       |

| $_IQ24(sat_{max})$ |

| $_IQ24(sat_{min})$ |

Where  $sat_{max}$  and  $sat_{min}$  are the upper and lower control effort bounds respectively. Note that to preserve maximum resolution the coefficients are

saved in Q26 format and the saturation limits are stored in Q24 format to match the output format.

Controller coefficients must be initialized before the controller is used. A structure `CNTL_2P2Z_CoefStruct` is used to ensure that the coefficients are stored exactly as shown in the table as the `CNTL_2P2Z` accesses them relative to a base address pointer. The structure is defined in the library header file `DPLib.h` to allow easy access to the elements from C.

**Usage:** This section explains how to use `CNTL_2P2Z` this module.

**Step 1 Add the library header file** in the file `{ProjectName}-Main.c`

```

#include "DPLib.h"

```

**Step 2 Declare the terminal pointers** in C in the file `{ProjectName}-Main.c`

```

// ----- DPLIB Net Pointers -----

// declare net pointers that are used to connect the DP Lib Macros here

// and the data variables being used by the macros internally

// CNTL_2P2Z - instance #1

extern volatile long *CNTL_2P2Z_Ref1;

extern volatile long *CNTL_2P2Z_Out1;

extern volatile long *CNTL_2P2Z_Fdbk1;

extern volatile long *CNTL_2P2Z_Coef1;

```

**Step 3 Declare signal net nodes/ variables in C** in the file `{ProjectName}-Main.c`

*Note signal net mode names change from system to system, no dependency exist between these names and module.*

```

// ----- DPLIB Variables -----

// declare the net nodes/variables being used by the DP Lib Macro here

long Ref , Fdbk , Out;

#pragma DATA_SECTION(CNTL_2P2Z_CoefStruct1, "CNTL_2P2Z_Coef");

struct CNTL_2P2Z_CoefStruct CNTL_2P2Z_CoefStruct1;

```

**Step 4 “Call” the `DPL_Init()` function to initialize the macros and “connect” the module terminals to the signal nets in “C” in `{ProjectName}-Main.c`**

```

-----Connect the macros to build a system-----

// Digital Power (DP) library initialisation

DPL_Init();

// Connect the CNTL_2P2Z block to the variables

CNTL_2P2Z_Fdbk1 = &Fdbk;

CNTL_2P2Z_Out1 = &Out;

CNTL_2P2Z_Ref1 = &Ref;

CNTL_2P2Z_Coef1 = &CNTL_2P2Z_CoefStruct1.b2;

```

```

// Initialize the Controller Coefficients

CNTL_2P2Z_CoefStruct1.b2 = _IQ26(0.05);

CNTL_2P2Z_CoefStruct1.b1 = _IQ26(-0.20);

CNTL_2P2Z_CoefStruct1.b0 = _IQ26(0.20);

CNTL_2P2Z_CoefStruct1.a2 = _IQ26(0.0);

CNTL_2P2Z_CoefStruct1.a1 = _IQ26(1.0);

CNTL_2P2Z_CoefStruct1.max =_IQ24(0.7);

CNTL_2P2Z_CoefStruct1.min =_IQ24(0.0);

//Initialize the net Variables/nodes

Ref=_IQ24(0.0);

Fdbk=_IQ24(0.0)

Out=_IQ24(0.0);

```

**Step 5** Add the ISR assembly file “{ProjectName}-DPL-ISR.asm” to the project

**Step 6** Include the assembly macro file in the {ProjectName}-DPL-ISR.asm

```

;Include files for the Power Library Macro's being used by the system

.include "CNTL_2P2Z.asm"

```

**Step 7** Instantiate the INIT macro in assembly (this is one-time pass through code) inside the C-callable DPL\_Init() function which is defined in {ProjectName}-DPL-ISR.asm

```

;Macro Specific Initialization Functions

CNTL_2P2Z_INIT 1 ; CNTL_2P2Z Initialization

```

**Step 8** Call the run time macro in assembly inside the C-callable function DPL\_ISR() which is the looped or ISR code. The function is defined in {ProjectName}-DPL-ISR.asm

```

;"Call" the Run macro

CNTL_2P2Z 1 ; Run the CNTL_2P2Z Macro

```

**Step 9** Include the memory sections in {DeviceName}-{RAM/FLASH}-{ProjectName}.CMD. Note, for the CNTL\_2P2Z module the net pointers and the internal data do not assume anything about allocation on a single data page.

```

/*CNTL_2P2Z sections*/

CNTL_2P2Z_Section      : > dataRAM PAGE = 1

CNTL_2P2Z_InternalData : > dataRAM PAGE = 1

CNTL_2P2Z_Coef         : > dataRAM PAGE = 1

```

**Module Net Definition:**

| <b>Net Name</b><br>(:n: is the instance<br>number) | <b>Description</b> | <b>Format</b>                                                                                           | <b>Acceptable Range<br/>of Variable or of the<br/>Variable being<br/>pointed to</b> |

|----------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| CNTL_2P2Z_Ref:n:                                   | Input Pointer      | Pointer to 32 bit fixed point input data<br>location storing the Reference value for<br>the controller. | Q24: [0, 1)                                                                         |

| CNTL_2P2Z_Fdbk:n:                                  | Input Pointer      | Pointer to 32 bit fixed point input data<br>location storing the Feedback value for<br>the controller.  | Q24: [0, 1)                                                                         |

| CNTL_2P2Z_Coef:n:                                  | Input Pointer      | Pointer to the location where coefficient<br>structure is stored.                                       | See Module<br>Description                                                           |

| CNTL_2P2Z_Out:n:                                   | Output<br>Pointer  | Pointer to 32 bit fixed point output<br>location where the reference for the<br>current loop is stored  | Q24:[ 0,1)                                                                          |

| CNTL_2P2Z_DBUFF:n:                                 | Internal<br>Data   | Data Variable storing the scaling factor                                                                | See Module<br>Description                                                           |

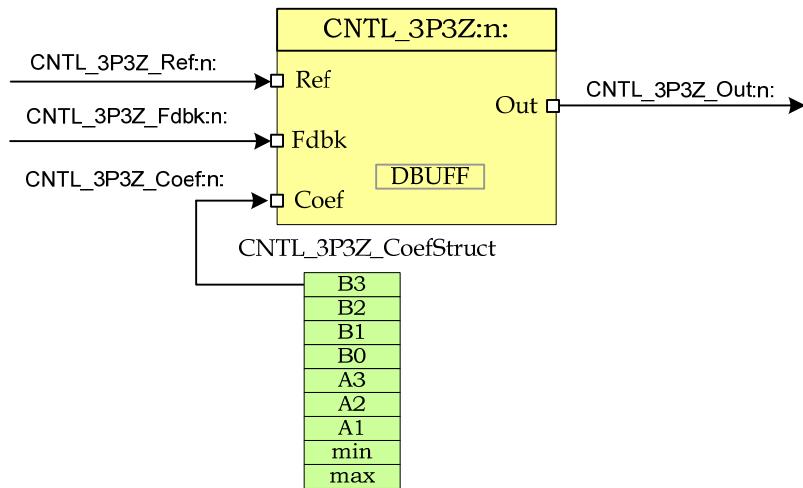

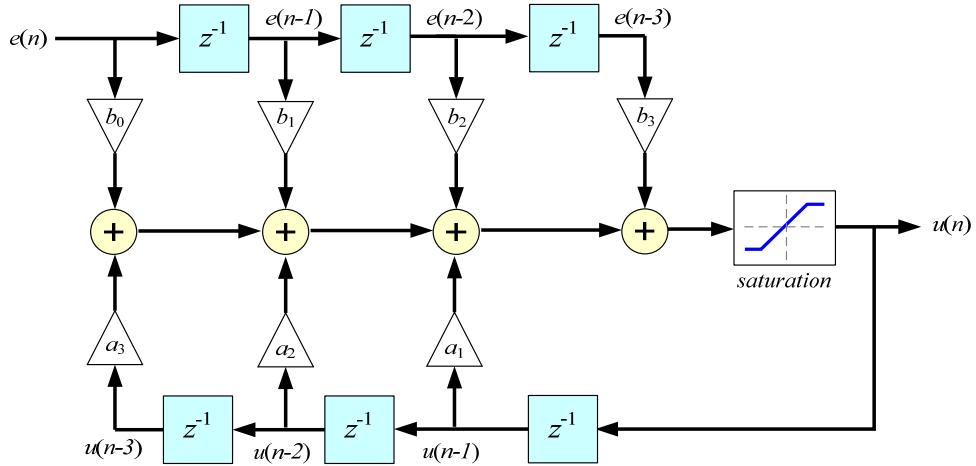

**Description:** This assembly macro implements a third order control law using a 3-pole, 3-zero construction. The code implementation is a third order IIR filter with programmable output saturation.

**Macro File:** CNTL\_3P3Z.asm

**Module**

**Description:**

The 3-pole 3-zero control block implements a third order control law using an IIR filter structure with programmable output saturation. This type of controller requires three delay lines: one for input data and one for output data, each consisting of three elements.

The discrete transfer function for the basic 3P3Z control law is...

$$\frac{U(z)}{E(z)} = \frac{b_3 z^{-3} + b_2 z^{-2} + b_1 z^{-1} + b_0}{1 - a_3 z^{-3} - a_2 z^{-2} - a_1 z^{-1}}$$

This may be expressed in difference equation form as:

$$u(n) = a_1 u(n-1) + a_2 u(n-2) + a_3 u(n-3) + b_0 e(n) + b_1 e(n-1) + b_2 e(n-2) + b_3 e(n-3)$$

Where...

- $u(n)$  = present controller output (after saturation)

- $u(n-1)$  = controller output on previous cycle

- $u(n-2)$  = controller output two cycles previously

- $u(n-3)$  = controller output three cycles previously

- $e(n)$  = present controller input

- $e(n-1)$  = controller input on previous cycle

- $e(n-2)$  = controller input two cycles previously

- $e(n-3)$  = controller input three cycles previously

The 3P3Z control law may also be represented graphically as shown below.

Input and output data are located in internal RAM with address designated by `CNTL_3P3Z_DBUFF` as shown below. Note that to preserve maximum resolution the module saves the values inside `CNTL_3P3Z_DBUFF` in `_IQ30` format.

| CNTL_3P3Z_DBUFF |          |

|-----------------|----------|

| 0               | $u(n-1)$ |

| 2               | $u(n-2)$ |

| 4               | $u(n-3)$ |

| 6               | $e(n)$   |

| 8               | $e(n-1)$ |

| 10              | $e(n-2)$ |

| 12              | $e(n-3)$ |

Controller coefficients and saturation settings are located in memory as shown:

### CNTL\_3P3Z\_CoefStruct

|                    |

|--------------------|

| $_IQ26(b_3)$       |

| $_IQ26(b_2)$       |

| $_IQ26(b_1)$       |

| $_IQ26(b_0)$       |

| $_IQ26(a_3)$       |

| $_IQ26(a_2)$       |

| $_IQ26(a_1)$       |

| $_IQ24(sat_{max})$ |

| $_IQ24(sat_{min})$ |

Where  $sat_{max}$  and  $sat_{min}$  are the upper and lower control effort bounds respectively. Note that to preserve maximum resolution the coefficients are saved in Q26 format and the saturation limits are stored in Q24 format to match the output format.

Controller coefficients must be initialized before the controller is used. A structure `CNTL_3P3Z_CoefStruct` is used to ensure that the coefficients are stored exactly as shown in the table as the `CNTL_3P3Z` accesses them relative to a base address pointer. The structure is defined in the library header file `DPLib.h` to allow easy access to the elements from C.

**Usage:** This section explains how to use this module.

**Step 1 Add library header file** in the file `{ProjectName}-Main.c`

```

#include "DPLib.h"

```

**Step 2 Declare the terminal pointers** in C in the file `{ProjectName}-Main.c`

```

// ----- DPLIB Net Pointers -----

// declare net pointers that are used to connect the DP Lib Macros here

// and the data variables being used by the macros internally

// CONTROL_3P3Z - instance #1

extern volatile long      *CNTL_3P3Z_Ref1;

extern volatile long      *CNTL_3P3Z_Out1;

extern volatile long      *CNTL_3P3Z_Fdbk1;

extern volatile long      *CNTL_3P3Z_Coef1;

```

**Step 3 Declare signal net nodes/ variables in C** in the file `{ProjectName}-Main.c`

*Note signal net mode names change from system to system, no dependency exist between these names and module.*

```

// ----- DPLIB Variables -----

// declare the net nodes/variables being used by the DP Lib Macro here

volatile long Ref , Fdbk , Out;

#pragma DATA_SECTION(CNTL_3P3Z_CoefStruct1, "CNTL_3P3Z_Coef")

struct CNTL_3P3Z_CoefStruct CNTL_3P3Z_CoefStruct1;

```

**Step 4** “Call” the DPL\_Init() to initialize the macros and “connect” the module terminals to the signal nets in “C” in {ProjectName}-Main.c

```

//-----Connect the macros to build a system-----

// Digital Power (DP) library initialisation

DPL_Init();

// Connect the CNTL_2P2Z block to the variables

CNTL_3P3Z_Fdbk1 = &Fdbk;

CNTL_3P3Z_Out1 = &Out;

CNTL_3P3Z_Ref1 = &Ref;

CNTL_3P3Z_Coef1 = &CNTL_3P3Z_CoefStruct1.b2;

```

```

// Initialize the Controller Coefficients

CNTL_3P3Z_CoefStruct1.b2 = _IQ26(0.05);

CNTL_3P3Z_CoefStruct1.b1 = _IQ26(-0.20);

CNTL_3P3Z_CoefStruct1.b0 = _IQ26(0.20);

CNTL_3P3Z_CoefStruct1.a2 = _IQ26(0.0);

CNTL_3P3Z_CoefStruct1.a1 = _IQ26(1.0);

CNTL_3P3Z_CoefStruct1.max =_IQ24(0.7);

CNTL_3P3Z_CoefStruct1.min =_IQ24(0.0);

//Initialize the net Variables/nodes

Ref=_IQ24(0.0);

Fdbk=_IQ24(0.0)

Out=_IQ24(0.0);

```

**Step 5** Add the ISR assembly file “{ProjectName}-DPL-ISR.asm” to the project

**Step 6** Include the macro's assembly file in the {ProjectName}-DPL-ISR.asm

```

;Include files for the Power Library Macro's being used by the system

.include "CNTL_3P3Z.asm"

```

**Step 7** Instantiate the INIT macro in assembly (this is one-time pass through code) inside the C-callable DPL\_Init() function which is defined in {ProjectName}-DPL-ISR.asm

```

;Macro Specific Initialization Functions

CNTL_3P3Z_INIT 1 ; CNTL_3P3Z Initialization

```

**Step 8 Call the run time macro** in assembly inside the C-callable function `DPL_ISR()` which is the looped or ISR code. The function is defined in `{ProjectName}-DPL-ISR.asm`

```

; "Call" the Run macro

CNTL_3P3Z 1           ; Run the CNTL_3P3Z Macro

```

**Step 9 Include the memory section** in the `{DeviceName}-{RAM/FLASH}-{ProjectName}.CMD`. Note, for the CNTL\_3P3Z module the net pointers and the internal data do not assume anything about allocation on a single data page.

```

/*CNTL_3P3Z sections*/

CNTL_3P3Z_Section      : > dataRAM PAGE = 1

CNTL_3P3Z_InternalData : > dataRAM PAGE = 1

CNTL_3P3Z_Coef         : > dataRAM PAGE = 1

```

#### Module Net Definition:

| Net Name<br>(:n: is the instance<br>number) | Description       | Format                                                                                                  | Acceptable Range<br>of Variable or of the<br>Variable being<br>pointed to |

|---------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| CNTL_3P3Z_Ref:n:                            | Input Pointer     | Pointer to 32 bit fixed point input data<br>location storing the Reference value for<br>the controller. | Q24: [0, 1)                                                               |

| CNTL_3P3Z_Fdbk:n:                           | Input Pointer     | Pointer to 32 bit fixed point input data<br>location storing the Feedback value for<br>the controller.  | Q24: [0, 1)                                                               |

| CNTL_3P3Z_Coef:n:                           | Input Pointer     | Pointer to the location where coefficient<br>structure is stored.                                       | See Module<br>Description                                                 |

| CNTL_3P3Z_Out:n:                            | Output<br>Pointer | Pointer to 32 bit fixed point output<br>location where the reference for the<br>current loop is stored  | Q24:[ 0,1)                                                                |

| CNTL_3P3Z_DBUFF:n:                          | Internal<br>Data  | Data Variable storing the scaling factor                                                                | See Module<br>Description                                                 |

## 5.2. Peripheral Configuration

### PWM\_PSFB\_PCMC\_CNF

### *PWM Configuration for PCMC controlled PSFB Stage*

**Description:** This module configures the PWM generators to control a phase shifted full bridge (PSFB) in peak current mode control (PCMC) and also configures synchronous rectifiers (SR), if used.

**Peripheral Initialization File:** PWM\_PSFB\_PCMC\_Cnf.c

**Description:** This module sets the initial configuration of two PWM peripheral modules to drive the four switches of the full bridge. It also has an option to configure the PWM module driving synchronous rectifier (SR) switches, if used. In this configuration the master module operates in up-down count mode and is used to drive switches in the full bridge leg with passive to active transitions. The next higher module in the PWM chain operates in up-count mode and is used to drive switches in the leg with active to passive transitions. The PWM module that drives SR switches also operates in up-count mode. These two slaved PWM module time-bases are synced at every half period of the master and are also directly synced by the comparator1 output.

This file is used in conjunction with the assembly code in the corresponding project specific ISR file.

The PWM\_PSFB\_PCMC\_Cnf.c file consists of the PWM configuration function

```

void PWMDRV_PSFB_PCMC_CNF(int16 n, int16 period, int16 SR_Enable, int16 Comp2_Pro

```

where

n is the master PWM peripheral configured for driving switches in one leg of the full bridge. PWM n+1 is configured to work with sync pulses from PWM n module and drives switches in the other leg. PWM n+3 drives SR switches if SR\_Enable is 1.

Period is the maximum count value of the PWM timer

SR\_Enable This enables drive to SR switches using PWM n+3 module.

Comp2\_Prot Enables catastrophic protection based on on-chip comparator2 and DAC.

#### Usage:

Call the peripheral configuration function PWMDRV\_PSFB\_PCMC\_CNF(int16 n, int16 Period, int16 SR\_Enable, int16 Comp2\_Prot) in {ProjectName}-Main.c, this function is defined in PWM\_PSFB\_PCMC\_SR\_Cnf.c. This file must be linked manually to the project.

```

// ePWM1 is the master, Period=PWM_PRD, SR_Enable=1, Comp2_Prot=1

PWMDRV_PSFB_PCMC_CNF(1, PWM_PRD, 1, 1);

```

### 5.3. Peripheral Drivers

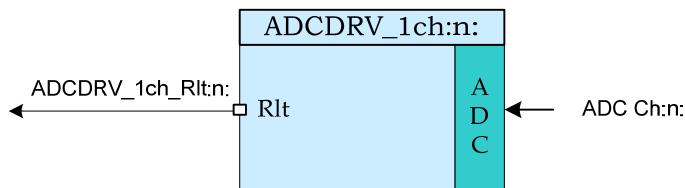

#### ADCDRV\_1ch

#### ADC Driver Single Channel

**Description:** This assembly macro reads a result from the internal ADC module Result Register:n: and delivers it in Q24 format to the output terminal, where :n: is the instance number. The output is normalized to 0-1.0 such that the minimum input voltage will generate nominally 0.0 at the driver output, and a maximum full scale input voltage read +1.0. The result is then stored in the memory location pointed to by the net terminal pointer.

**Macro File:** ADCDRV\_1ch.asm

**Peripheral Initialization File:** ADC\_SOC\_Cnf.c

**Description:** The ADC module in the F2802x & F2803x devices includes a ratio-metric input which enables the user to determine the maximum and minimum input voltages. The ADC converts this input range with 12-bits of resolution. The ADCDRV macro reads one pre-defined result register (determined by the instance number of the macro i.e. instance 0 reads AdcResult.ADCRESULT0 and instance 5 reads AdcResult.ADCRESULT5). The module then scales this to Q24 format and writes the result in unipolar Q24 format to the output net terminal.

This macro is used in conjunction with the peripheral configuration file ADC\_SOC\_Cnf.c. The file defines the function

```

void ADC_SOC_CNF(int ChSel[], int TrigSel[], int ACQPS[],

int IntChSel, int mode)

```

where

ChSel[] stores which ADC pin is used for conversion when a Start of Conversion(SOC) trigger is received for the respective channel

TrigSel[] stores what trigger input starts the conversion of the respective channel

ACQPS[] stores the acquisition window size used for the respective channel

IntChSel is the channel number that triggers interrupt ADCINT 1. If the ADC interrupt is not being used enter a value of 0x10.

Mode      determines what mode the ADC is configured in

Mode =0 Start/Stop mode, configures ADC conversions to be started by the appropriate channel trigger, an ADC interrupt is raised whenever conversion is complete for the IntChSel channel. The ADC interrupt flag needs to be cleared for the interrupt to be retriggered. This is the mode used for most C28x based projects.

Mode =1 The ADC is configured in continuous conversion mode. This mode maintains compatibility with previous generation ADCs.

Mode =2 CLA Mode, configures ADC conversions to be started by the appropriate channel trigger. An ADC interrupt is triggered when conversion is complete and the ADC interrupt flag is automatically cleared. This mode is used for all of the CLA based projects.

Note the function configures the complete ADC module in a single function call. Hence this function is called only once even for multiple ADCDRV modules.

**Usage:**

**Step 1 Add library header file** in the file {ProjectName}-Main.c

```

#include "DPLib.h"

```

**Step 2 Declare the terminal pointers** in C in the file {ProjectName}-Main.c

```

// ----- DPLIB Net Pointers -----

// Declare net pointers that are used to connect the DP Lib Macros here

// and the data variables being used by the macros internally

//ADCDRV_1ch - instance #1

extern volatile long *ADCDRV_1ch_Rlt1;

```

**Step 3 Declare signal net nodes/ variables in C** in the file {ProjectName}-Main.c

*Note signal net node names change from system to system, no dependency exist between these names and module.*

```

// ----- DPLIB Variables -----

// Declare the net variables being used by the DP Lib Macro here

volatile long Out;

```

**Step 4 Call the peripheral configuration function** ADC\_SOC\_CNF(int ChSel[], int TrigSel[], int ACQPS[], int IntChSel, int mode) in {ProjectName}-Main.c, this function is defined in ADC\_SOC\_CNF.c. This file must be included manually into the project.

```

/* Configure ADC channel 0 to convert ADCINB5, and ADC channel 1 to

convert the ADCINA3. The ADC is configured in start stop mode and

channel 0 is configured to raise ADCINT 1. ADC Channel 0 is configured

to be use PWM1 SOCA and channel 1 is configured to use PWM 5 SOCB as

trigger. The following code snippet assumes that the PWM peripherals

have been configured appropriately to generate a SOCA and SOCB */

// Specify ADC Channel - pin Selection for Configuring the ADC

ChSel[0] = 13;           // ADC B5

ChSel[1] = 3;            // ADC A3

// Specify the Conversion Trigger for each channel

TrigSel[0]= ADCTRIG_EPWM1_SOCA;

TrigSel[1]= ADCTRIG_EPWM5_SOCB;

// Call the ADC Configuration Function

ADC_SOC_CNF(ChSel,TrigSel,ACQPS,1,0);

```

**Step 5 “Call” the DPL\_Init() to initialize the macros and “connect” the module terminals to the signal nets in “C” in {ProjectName}-Main.c.**

```

-----Connect the macros to build a system-----

// Digital Power (DP) library initialisation

DPL_Init();

// ADCDRV_1ch block connections

ADCDRV_1ch_Rlt1=&Out;

// Initialize the net variables

Out=_IQ24(0.0);

```

**Step 6 Add the ISR assembly file “{ProjectName}-DPL-ISR.asm” to the project.**

**Step 7 Include the macro's assembly file in the {ProjectName}-DPL-ISR.asm**

```

;Include files for the Power Library Macro's being used by the system

.include "ADCDRV_1ch.asm"

```

**Step 8 Instantiate the INIT macro in assembly (this is one-time pass through code) inside the C-callable DPL\_Init() function which is defined in {ProjectName}-DPL-ISR.asm**

```

;Macro Specific Initialization Functions

ADCDRV_1ch_INIT 1 ; ADCDRV_1ch Initialization

```

**Step 9 Call the run time macro** in assembly inside the C-callable function DPL\_ISR() which is the looped or ISR code. The function is defined in {ProjectName}-DPL-ISR.asm

```

; "Call" the Run macro

ADCDRV_1ch 1      ; Run ADCDRV_1ch

```

**Step 10 Include the memory sections** in the {DeviceName}- {RAM/FLASH} -

{ProjectName}.CMD. Note that the net pointers and the internal data are forced to be placed in a single data page by use of the .usect directive in the source file of the module.

```

/*ADCDRV_1ch sections*/

ADCDRV_1ch_Section    : > dataRAM          PAGE = 1

```

#### Module Net Definition:

| Net name<br>(:n: is the instance<br>number) | Description       | Format                                                                           | Acceptable Range<br>of Variable or of<br>the Variable being<br>pointed to |

|---------------------------------------------|-------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| ADCDRV_1ch_Rlt:n:                           | Output<br>Pointer | Pointer to 32 bit fixed point data location<br>storing the result of the module. | Q24: [0, 1)                                                               |

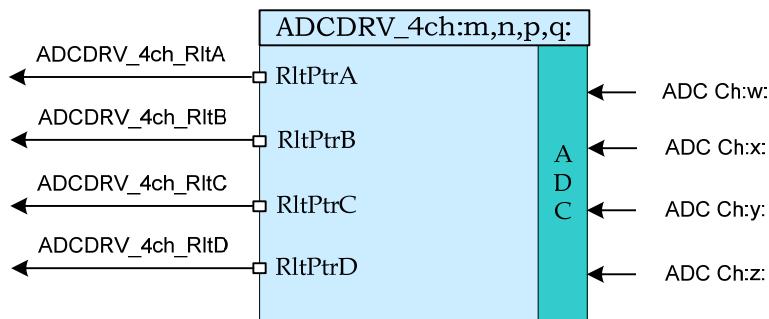

**Description:** This assembly macro reads four results from the internal ADC module result registers m,n,p,q and delivers them in Q24 format to the output terminals. The output is normalized to 0-1.0 such that the minimum input voltage will generate nominally 0.0 at the driver output, and a maximum full scale input voltage read +1.0. The result are then stored in the memory location pointed to by the net terminal pointers.

**Macro File:** ADCDRV\_4ch.asm

**Peripheral Initialization File:** ADC\_SOC\_Cnf.c

**Description:** The ADC module in the F2802x & F2803x devices includes a ratio-metric input which enables the user to determine the maximum and minimum input voltages. The ADC converts this input range with 12-bits of resolution. The ADCDRV macro reads the result register (determined by the numbers that are parsed to the run time macro m,n,p and q. The module then scales these to Q24 format and writes the result in unipolar Q24 format to the output net terminal.

This macro is used in conjunction with the peripheral configuration file ADC\_SOC\_Cnf.c. The file defines the function

```

void ADC_SOC_CNF(int ChSel[], int TrigSel[], int ACQPS[],

int IntChSel, int mode)

```

where

ChSel[] Array that stores which ADC pin is used for conversion when a start of conversion is received for the respective channel

TrigSel[] stores what trigger Input starts the conversion of the respective channel

ACQPS[] stores the acquisition window size used for the respective channel

IntChSel is the channel number that triggers interrupt ADCINT 1. If the ADC interrupt is not being used enter a value of 0x10.

Mode      determines what mode the ADC is configured in

Mode =0 Start/Stop mode, configures ADC conversions to be started by the appropriate channel trigger, an ADC interrupt is raised whenever conversion is complete for the IntChSel channel. The ADC interrupt flag needs to be cleared for the interrupt to be retriggered. This is the mode used for most C28x based projects.

Mode =1 The ADC is configured in continuous conversion mode. This mode maintains compatibility with previous generation ADCs.

Mode =2 CLA Mode, configures ADC conversions to be started by the appropriate channel trigger. an ADC interrupt is raised whenever conversion is complete and the ADC Interrupt Flag is auto cleared. This mode is used for all of the CLA based projects.

Note the function configures the complete ADC module in a single function call. Hence this function is called only once.

This function is responsible for associating the ADC peripheral pins to result registers. The macro run time call is only responsible for reading these registers.

Multiple instantiation of this macro is not supported.

#### Usage:

**Step 1 Add library header file** in the file {ProjectName}-Main.c

```

#include "DPLib.h"

```

**Step 2 Declare the terminal pointers** in C in the file {ProjectName}-Main.c

```

// ----- DPLIB Net Pointers -----

// Declare net pointers that are used to connect the DP Lib Macros here

// and the data variables being used by the macros internally

//ADCDRV_4ch

extern volatile long *ADCDRV_4ch_RltA;

extern volatile long *ADCDRV_4ch_RltB;

extern volatile long *ADCDRV_4ch_RltC;

extern volatile long *ADCDRV_4ch_RltD;

```

**Step 3 Declare signal net nodes/ variables in C** in the file {ProjectName}-Main.c

*Note signal net node names change from system to system, no dependency exist between these names and module.*

```

// ----- DPLIB Variables -----

// Declare the net variables being used by the DP Lib Macro here

volatile long RltA,RltB,RltC,RltD;

```

**Step 4 Call the peripheral configuration function** ADC\_SOC\_CNF(int ChSel[], int TrigSel[], int ACQPS[], int IntChSel, int mode) in {ProjectName}-Main.c, this function is defined in ADC\_SOC\_CNF.c. This file must be included manually into the project.

```

/* Configure ADC channel 0 to convert ADCINB5, and ADC channel 1 to

convert the ADCINA3, ADC Channel 2 converts ADCINA7 and ADC channel 5

converts ADCINB2. The ADC is configured in start stop mode and ADC

Interrupt is disabled. ADC Channel 0,2 is configured to use PWM1 SOCA

and channel 1,5 is configured to use PWM 5 SOCB as trigger. The

following code snippet assumes that the PWM peripherals have been

configured appropriately to generate a SOCA and SOCB */

// Specify ADC Channel - pin Selection for Configuring the ADC

ChSel[0] = 13;           // ADC B5

ChSel[1] = 3;            // ADC A3

ChSel[2] = 7;            // ADC A7

ChSel[5] = 10;           // ADC B2

// Specify the Conversion Trigger for each channel

TrigSel[0]= ADCTRIG_EPWM1_SOCA;

TrigSel[1]= ADCTRIG_EPWM5_SOCB;

TrigSel[2]= ADCTRIG_EPWM1_SOCA;

TrigSel[5]= ADCTRIG_EPWM5_SOCB;

// Call the ADC Configuration Function

ADC_SOC_CNF(ChSel,TrigSel,ACQPS,1,0);

```

**Step 5 “Call” the DPL\_Init() to initialize the macros and “connect” the module terminals to the Signal nets in “C” in {ProjectName}-Main.c.**

```

-----Connect the macros to build a system-----

// Digital Power (DP) library initialisation

DPL_Init();

// ADCDRV_4ch block connections

ADCDRV_4ch_RltA=&RltA;

ADCDRV_4ch_RltB=&RltB;

ADCDRV_4ch_RltC=&RltC;

ADCDRV_4ch_RltD=&RltD;

// Initialize the net variables

RltA=_IQ24(0.0);

RltB=_IQ24(0.0);

RltC=_IQ24(0.0);

RltD=_IQ24(0.0);

```

**Step 6 Add** the ISR assembly file “{ProjectName}-DPL-ISR.asm” to the project.

**Step 7 Include** the macro's assembly file in the {ProjectName}-DPL-ISR.asm

```

;Include files for the Power Library Macro's being used by the system

.include "ADCDRV_4ch.asm"

```

**Step 8 Instantiate the INIT macro** in assembly (this is one-time pass through code) inside the C-callable DPL\_Init() function which is defined in {ProjectName}-DPL-ISR.asm. Four numbers need to be specified to identify which result registers would be read and scaled results written to the respective pointers. The following code snippet would do the following

```

AdcResult.ADCRESULT0 -> (Scale) -> *(ADCDRV_4ch_RltA)

AdcResult.ADCRESULT5 -> (Scale) -> *(ADCDRV_4ch_RltB)

AdcResult.ADCRESULT2 -> (Scale) -> *(ADCDRV_4ch_RltC)

AdcResult.ADCRESULT1 -> (Scale) -> *(ADCDRV_4ch_RltD)

```

```

;Macro Specific Initialization Functions

ADCDRV_4ch_INIT 0,5,2,1 ; ADCDRV_4ch Initialization

```

**Step 9 Call the run time macro** in assembly inside the C-callable function DPL\_ISR() which is the looped or ISR code. The function is defined in {ProjectName}-DPL-ISR.asm

```

;"Call" the Run macro

ADCDRV_4ch 0,5,2,1 ; Run ADCDRV_4ch

```

**Step 10 Include the memory sections** in the {DeviceName}-{RAM/FLASH}-{ProjectName}.CMD. Note that the net pointers and the internal data are forced to be placed in a single data page by use of the .usect directive in the source file of the module.

```

/*ADCDRV_4ch sections*/

ADCDRV_4ch_Section : > dataRAM PAGE = 1

```

#### Module Net Definition:

| Net name<br>(:n: is the instance<br>number) | Description       | Format                                                                           | Acceptable Range<br>of Variable or of<br>the Variable being<br>pointed to |

|---------------------------------------------|-------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| ADCDRV_4ch_RltA                             | Output<br>Pointer | Pointer to 32 bit fixed point data location<br>storing the result of the module. | Q24: [0, 1)                                                               |

| ADCDRV_4ch_RltB                             | Output<br>Pointer | Pointer to 32 bit fixed point data location<br>storing the result of the module. | Q24: [0, 1)                                                               |

| ADCDRV_4ch_RltC                             | Output<br>Pointer | Pointer to 32 bit fixed point data location<br>storing the result of the module. | Q24: [0, 1)                                                               |

| ADCDRV_4ch_RltD                             | Output<br>Pointer | Pointer to 32 bit fixed point data location<br>storing the result of the module. | Q24: [0, 1)                                                               |

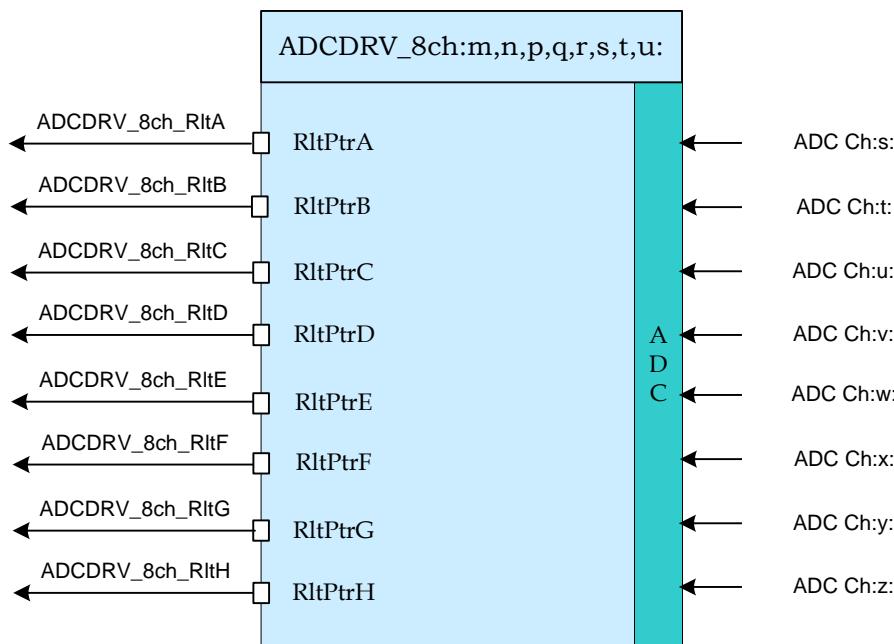

**Description:** This assembly macro reads eight results from the internal ADC module result registers m,n,p,q,r,s,t,u and delivers them in Q24 format to the output terminals. The output is normalized to 0-1.0 such that the minimum input voltage will generate nominally 0.0 at the driver output, and a maximum full scale input voltage read +1.0. The results are then stored in the memory locations pointed to by the net terminal pointers.

**Macro File:** ADCDRV\_8ch.asm

**Peripheral**

**Initialization File:** ADC\_SOC\_Cnf.c

**Description:** The ADC module in the F2802x & F2803x devices includes a ratio-metric input which enables the user to determine the maximum and minimum input voltages. The ADC converts this input range with 12-bits of resolution. The ADCDRV macro reads the result register (determined by the numbers that are parsed to the run time macro m,n,p,q,r,s,t and u. The module then scales these to Q24 format and writes the result in unipolar Q24 format to the output net terminal.

This macro is used in conjunction with the peripheral configuration file ADC\_SOC\_Cnf.c. The file defines the function

```

void ADC_SOC_CNF(int ChSel[], int Trigsel[], int ACQPS[],

int IntChSel, int mode)

```

where

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ChSel[]   | Array that stores which ADC pin is used for conversion when a start of conversion is received for the respective channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TrigSel[] | stores what trigger Input starts the conversion of the respective channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ACQPS[]   | stores the acquisition window size used for the respective channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IntChSel  | is the channel number that triggers interrupt ADCINT 1. If the ADC interrupt is not being used enter a value of 0x10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Mode      | <p>determines what mode the ADC is configured in</p> <p>Mode =0 Start/Stop mode, configures ADC conversions to be started by the appropriate channel trigger, an ADC interrupt is raised whenever conversion is complete for the IntChSel channel. The ADC interrupt flag needs to be cleared for the interrupt to be retrigged. This is the mode used for most C28x based projects.</p> <p>Mode =1 The ADC is configured in continuous conversion mode. This mode maintains compatibility with previous generation ADCs.</p> <p>Mode =2 CLA Mode, configures ADC conversions to be started by the appropriate channel trigger. An ADC interrupt is raised whenever conversion is complete and the ADC Interrupt Flag is auto cleared. This mode is used for all of the CLA based projects.</p> |

Note the function configures the complete ADC module in a single function call. Hence this function is called only once.

This function is responsible for associating the ADC peripheral pins to result registers. The macro run time call is only responsible for reading these registers.

Multiple instantiations of this macro are not supported.

#### Usage:

**Step 1 Add library header file** in the file {ProjectName}-Main.c

```

#include "DPLib.h"

```

**Step 2 Declare the terminal pointers** in C in the file {ProjectName}-Main.c

```

// ----- DPLIB Net Pointers -----

// Declare net pointers that are used to connect the DP Lib Macros here

// and the data variables being used by the macros internally

//ADCDRV_8ch

extern volatile long *ADCDRV_4ch_RltA;

extern volatile long *ADCDRV_4ch_RltB;

extern volatile long *ADCDRV_4ch_RltC;

extern volatile long *ADCDRV_4ch_RltD;

extern volatile long *ADCDRV_4ch_RltE;

extern volatile long *ADCDRV_4ch_RltF;

extern volatile long *ADCDRV_4ch_RltG;

extern volatile long *ADCDRV_4ch_RltH;

```

**Step 3 Declare signal net nodes/ variables in C** in the file {ProjectName}-Main.c

*Note signal net node names change from system to system, no dependency exist between these names and module.*

```

// ----- DPLIB Variables -----

// Declare the net variables being used by the DP Lib Macro here

volatile long RltA,RltB,RltC,RltD,RltE,RltF,RltG,RltH;

```

**Step 4 Call the peripheral configuration function** ADC\_SOC\_CNF(int ChSel[],int TrigSel[],int ACQPS[], int IntChSel, int mode) in {ProjectName}-Main.c, this function is defined in ADC\_SOC\_CNF.c. This file must be included manually into the project.

```

/* Configure ADC channel 0 to convert ADCINB5, and ADC channel 1 to

convert the ADCINA3, ADC Channel 2 converts ADCINA7, ADC channel 3

converts ADCINB2, channel 4 converts ADCINA0, channel 5 converts

ADCINA1, channel 6 converts ADCINB1 and channel 7 converts ADCINA4. The

ADC is configured in start stop mode and ADC Interrupt is disabled. ADC

Channel 0,2 is configured to use PWM1 SOCA, channel 1,3 is configured

to use PWM 5 SOCB as trigger, channel 4,7 use PWM 3 SOCA as trigger and

channel 5,6 use PWM 2 SOCB as trigger . The following code snippet

assumes that the PWM peripherals have been configured appropriately to

generate a SOCA and SOCB */

// Specify ADC Channel - pin Selection for Configuring the ADC

ChSel[0] = 13;           // ADC B5

ChSel[1] = 3;            // ADC A3

ChSel[2] = 7;            // ADC A7

ChSel[3] = 10;           // ADC B2

ChSel[4] = 0;             // ADC A0

ChSel[5] = 1;             // ADC A1

ChSel[6] = 9;             // ADC B1

ChSel[7] = 4;             // ADC A4

// Specify the Conversion Trigger for each channel

TrigSel[0]= ADCTRIG_EPWM1_SOCA;

TrigSel[1]= ADCTRIG_EPWM5_SOCB;

TrigSel[2]= ADCTRIG_EPWM1_SOCA;

TrigSel[3]= ADCTRIG_EPWM5_SOCB;

```

```

TrigSel[4]= ADCTRIG_EPWM3_SOCA;

TrigSel[5]= ADCTRIG_EPWM2_SOCB;

TrigSel[6]= ADCTRIG_EPWM2_SOCB;

TrigSel[7]= ADCTRIG_EPWM3_SOCA;

// Call the ADC Configuration Function

ADC_SOC_CNF(ChSel,TrigSel,ACQPS,1,0);

```

**Step 5** “Call” the DPL\_Init() to initialize the macros and “connect” the module terminals to the Signal nets in “C” in {ProjectName}-Main.c.

```

//-----Connect the macros to build a system-----

// Digital Power (DP) library initialisation

DPL_Init();

// ADCDRV_8ch block connections

ADCDRV_8ch_RltA=&RltA;

ADCDRV_8ch_RltB=&RltB;

ADCDRV_8ch_RltC=&RltC;

ADCDRV_8ch_RltD=&RltD;

ADCDRV_8ch_RltE=&RltE;

ADCDRV_8ch_RltF=&RltF;

ADCDRV_8ch_RltG=&RltG;

ADCDRV_8ch_RltH=&RltH;

// Initialize the net variables

RltA=_IQ24(0.0);

RltB=_IQ24(0.0);

RltC=_IQ24(0.0);

RltD=_IQ24(0.0);

RltE=_IQ24(0.0);

RltF=_IQ24(0.0);

RltG=_IQ24(0.0);

RltH=_IQ24(0.0);

```

**Step 6** Add the ISR assembly file “{ProjectName}-DPL-ISR.asm” to the project.

**Step 7** Include the macro’s assembly file in the {ProjectName}-DPL-ISR.asm

```

;Include files for the Power Library Macro's being used by the system

.include "ADCDRV_8ch.asm"

```

**Step 8** Instantiate the INIT macro in assembly (this is one-time pass through code) inside the C-callable DPL\_Init() function which is defined in {ProjectName}-DPL-ISR.asm. Eight numbers need to be specified to identify which result registers would be read and scaled results written to the respective pointers. The following code snippet would do the following

```

AdcResult.ADCRESULT0 -> (Scale) -> *(ADCDRV_4ch_RltA)

AdcResult.ADCRESULT1 -> (Scale) -> *(ADCDRV_4ch_RltB)

AdcResult.ADCRESULT2 -> (Scale) -> *(ADCDRV_4ch_RltC)

AdcResult.ADCRESULT3 -> (Scale) -> *(ADCDRV_4ch_RltD)

AdcResult.ADCRESULT4 -> (Scale) -> *(ADCDRV_4ch_RltE)

AdcResult.ADCRESULT5 -> (Scale) -> *(ADCDRV_4ch_RltF)

```

```

AdcResult.ADCRESULT6 -> (Scale) -> *(ADCDRV_4ch_RltG)

AdcResult.ADCSESLT7 -> (Scale) -> *(ADCDRV_4ch_RltH)

```

```

;Macro Specific Initialization Functions

ADCDRV_8ch_INIT 0,1,2,3,4,5,6,7      ; ADCDRV_8ch Initialization

```

**Step 9 Call the run time macro** in assembly inside the C-callable function DPL\_ISR() which is the looped or ISR code. The function is defined in {ProjectName}-DPL-ISR.asm

```

;;"Call" the Run macro

ADCDRV_8ch 0,1,2,3,4,5,6,7      ; Run ADCDRV_8ch

```

**Step 10 Include the memory sections** in the {DeviceName}-{RAM/FLASH}-{ProjectName}.CMD. Note that the net pointers and the internal data are forced to be placed in a single data page by use of the .usect directive in the source file of the module.

```

/*ADCDRV_8ch sections*/

ADCDRV_8ch_Section      : > dataRAM          PAGE = 1

```

#### Module Net Definition:

| Net name<br>(:n: is the instance<br>number) | Description       | Format                                                                           | Acceptable Range<br>of Variable or of<br>the Variable being<br>pointed to |

|---------------------------------------------|-------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| ADCDRV_8ch_RltA                             | Output<br>Pointer | Pointer to 32 bit fixed point data location<br>storing the result of the module. | Q24: [0, 1)                                                               |

| ADCDRV_8ch_RltB                             | Output<br>Pointer | Pointer to 32 bit fixed point data location<br>storing the result of the module. | Q24: [0, 1)                                                               |

| ADCDRV_8ch_RltC                             | Output<br>Pointer | Pointer to 32 bit fixed point data location<br>storing the result of the module. | Q24: [0, 1)                                                               |

| ADCDRV_8ch_RltD                             | Output<br>Pointer | Pointer to 32 bit fixed point data location<br>storing the result of the module. | Q24: [0, 1)                                                               |

| ADCDRV_8ch_RltE                             | Output<br>Pointer | Pointer to 32 bit fixed point data location<br>storing the result of the module. | Q24: [0, 1)                                                               |

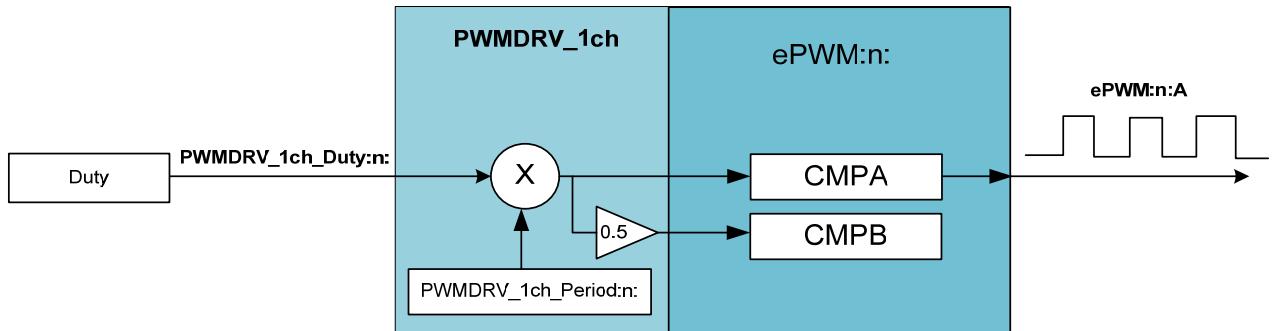

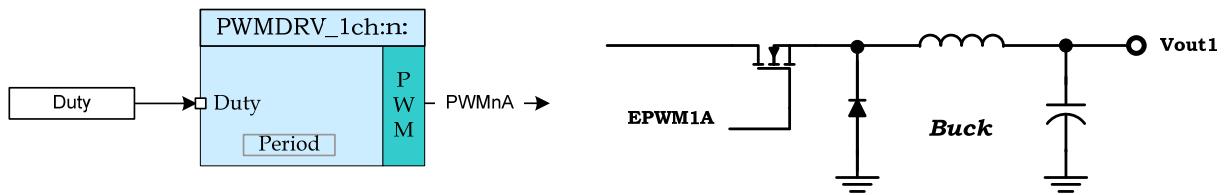

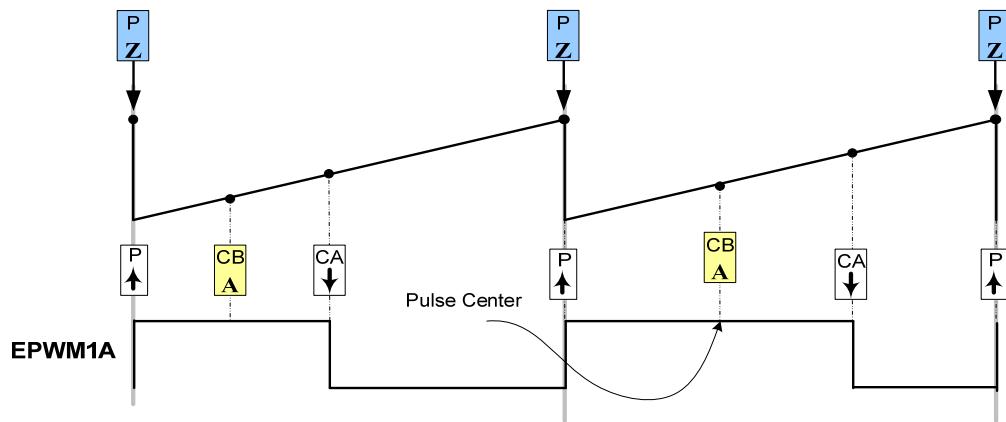

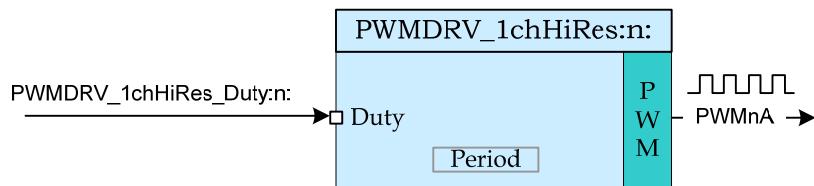

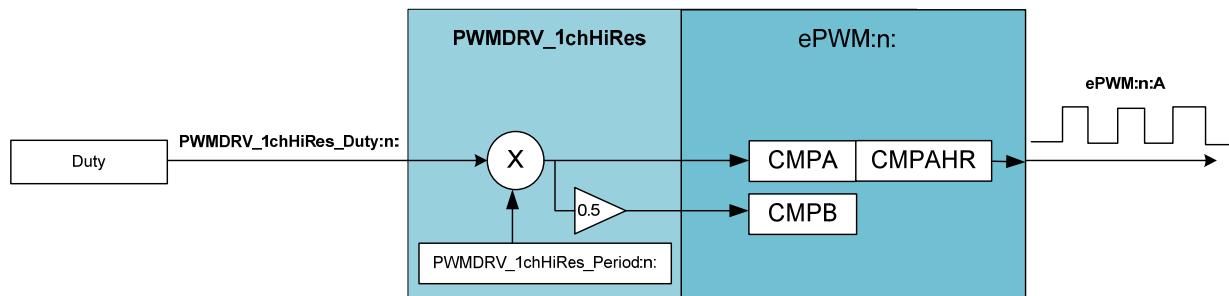

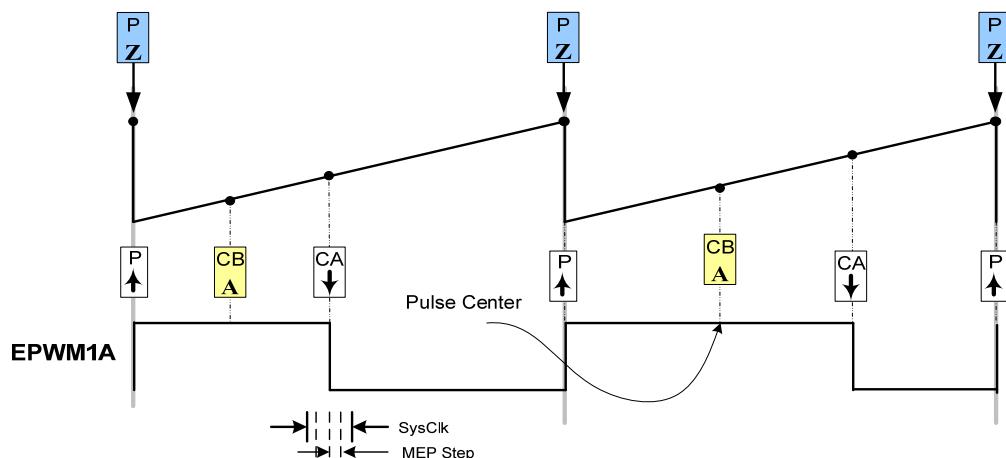

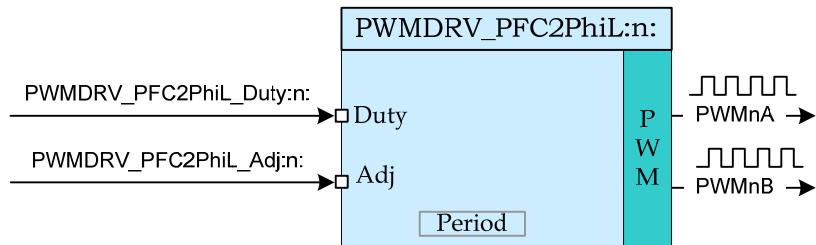

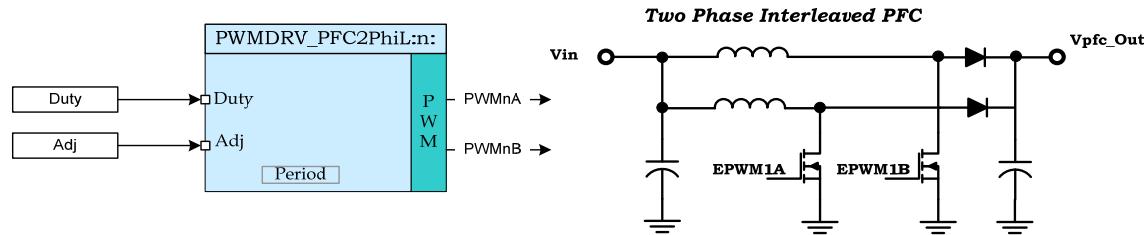

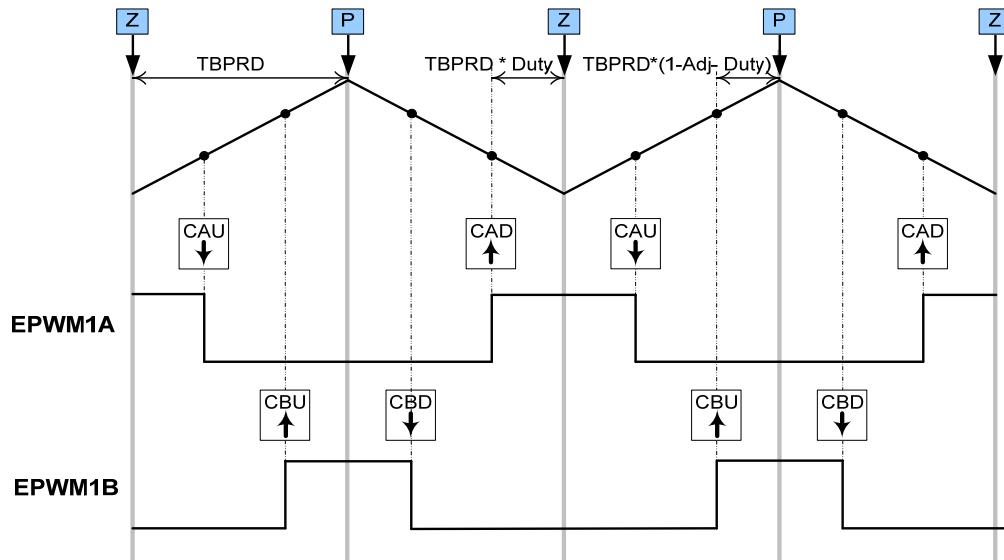

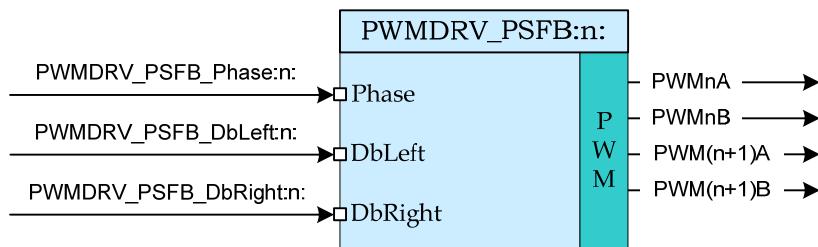

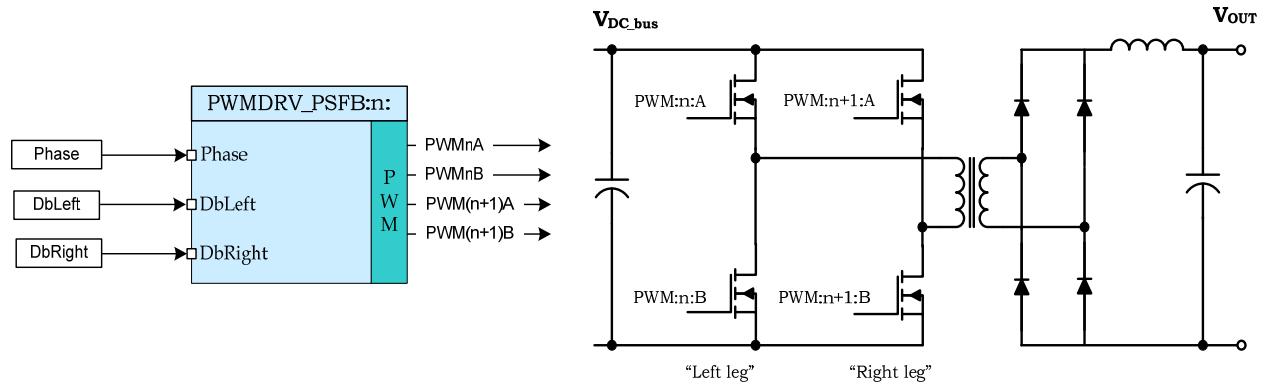

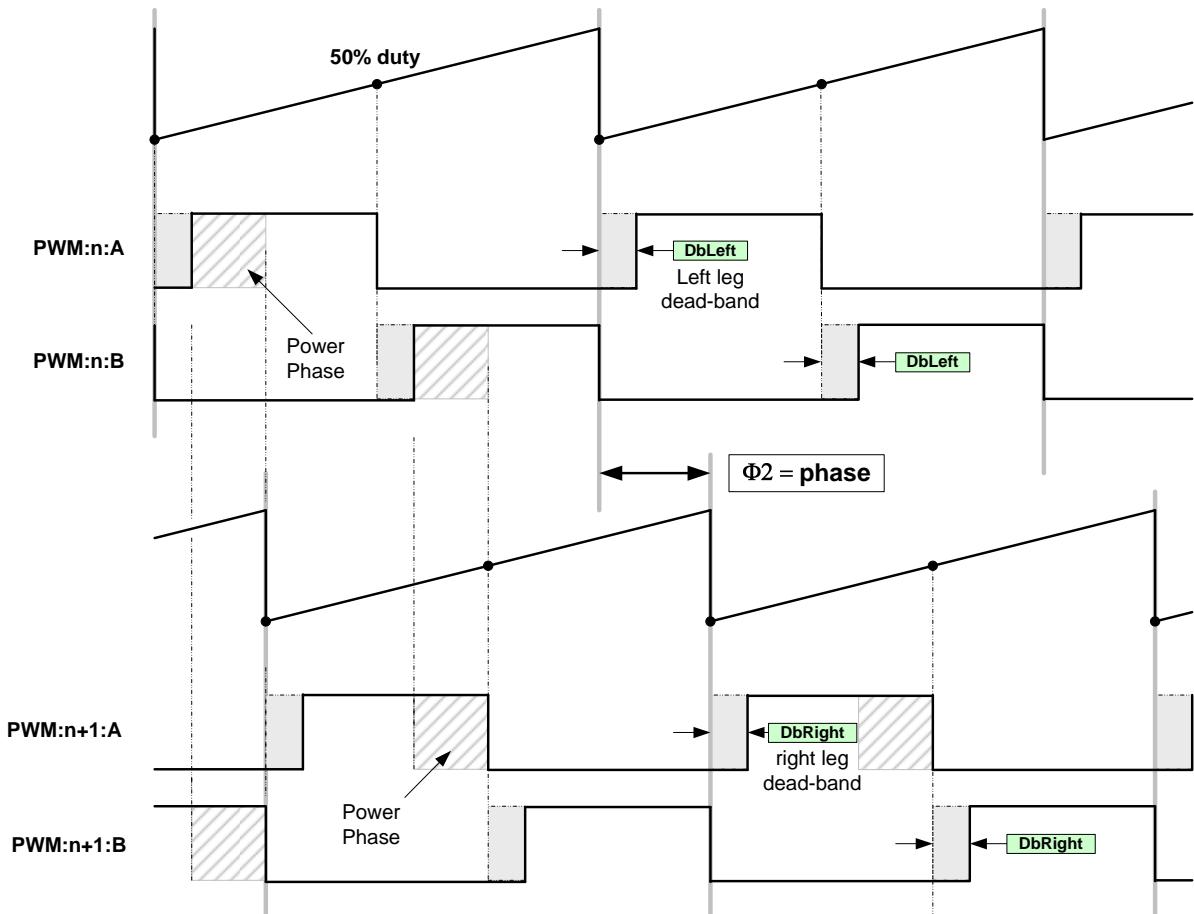

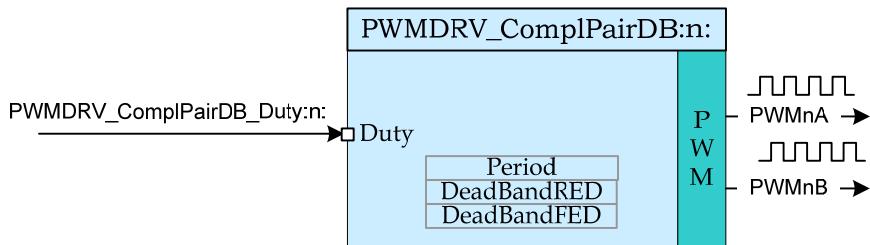

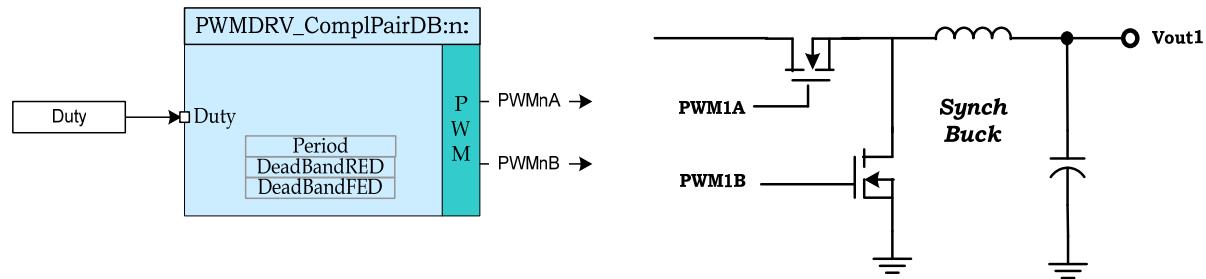

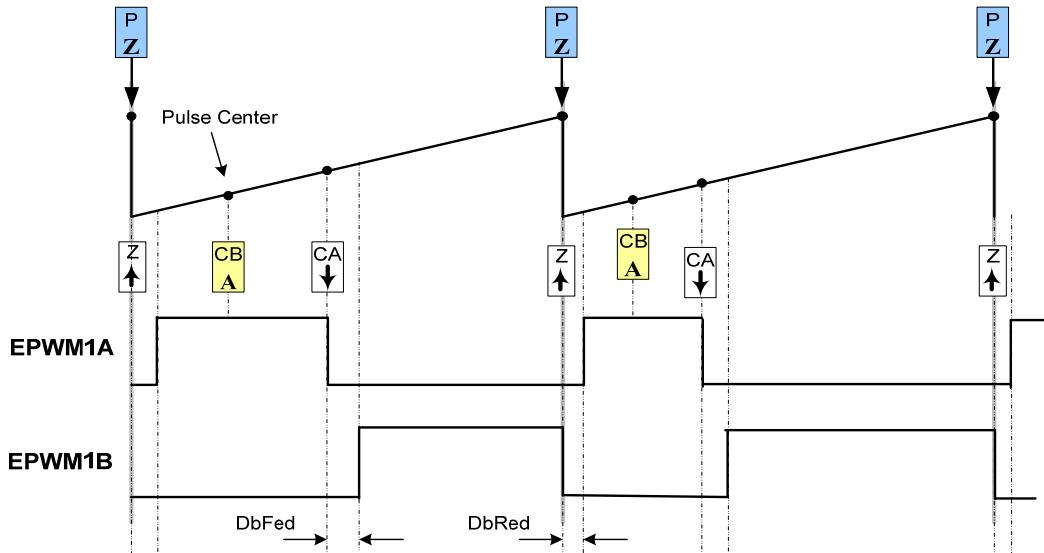

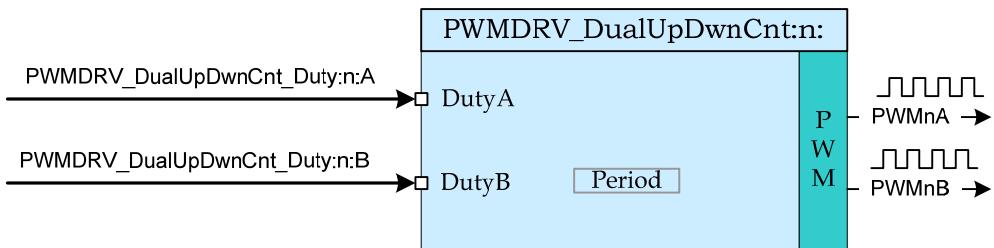

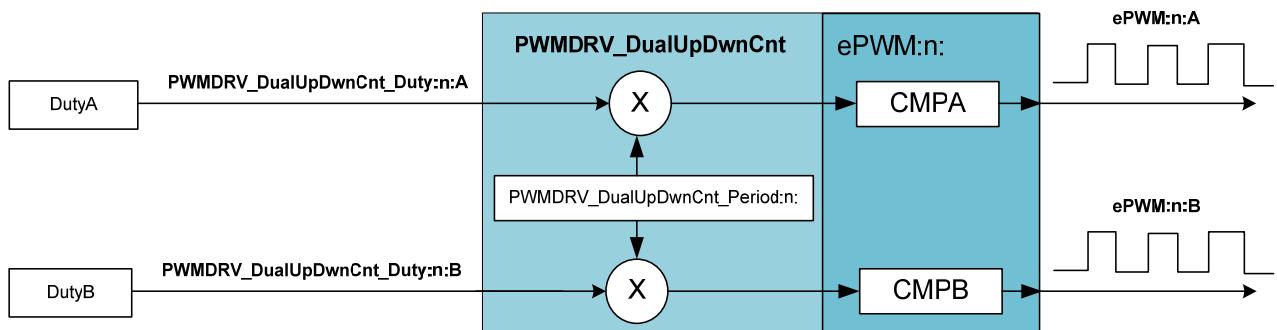

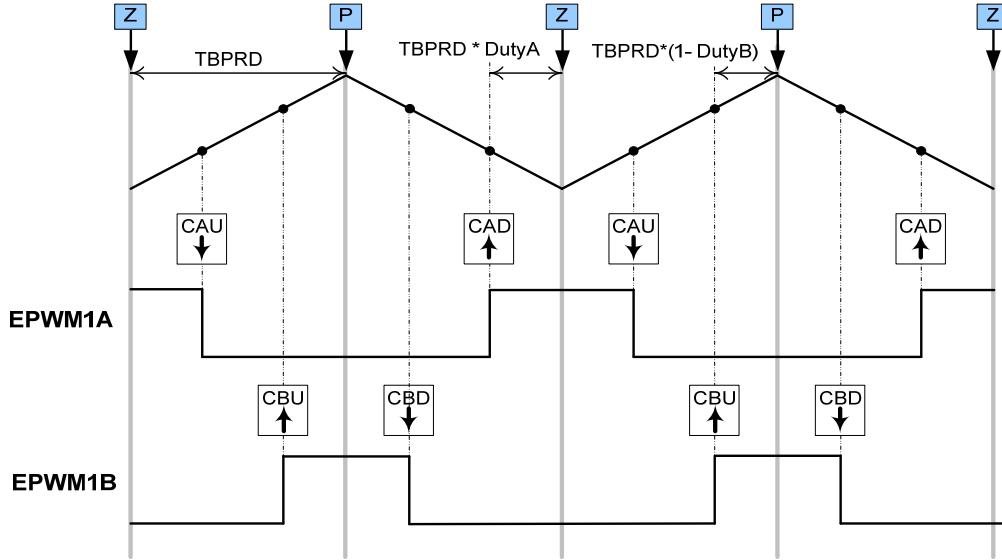

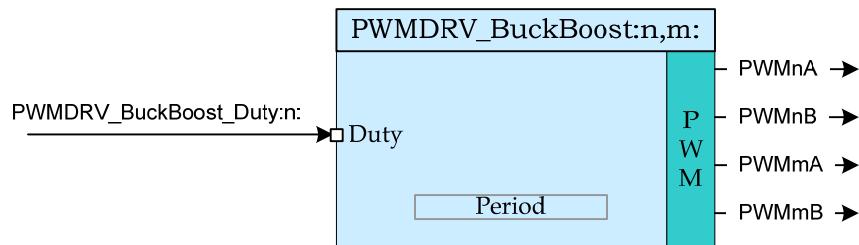

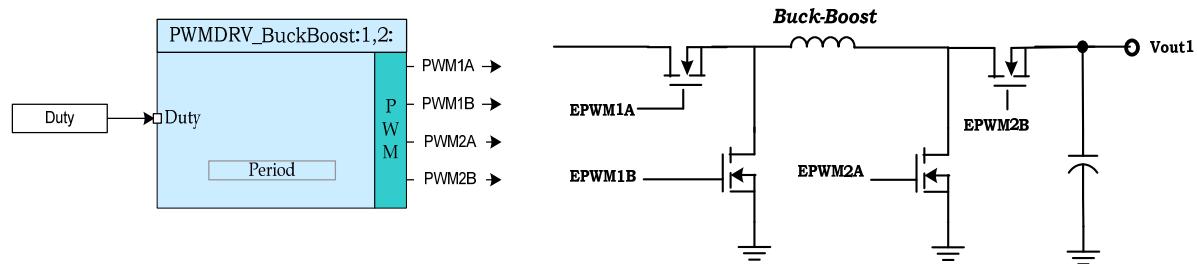

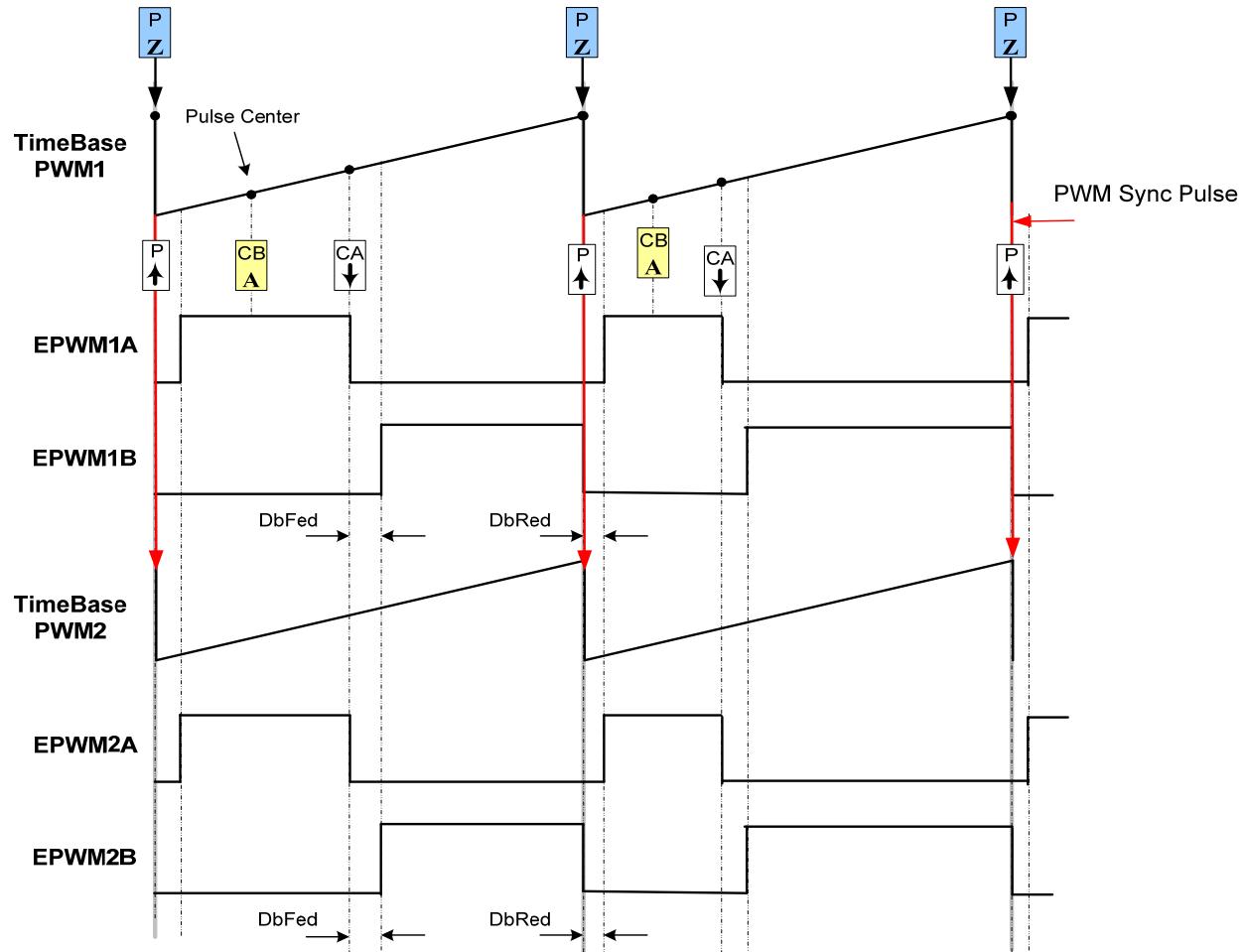

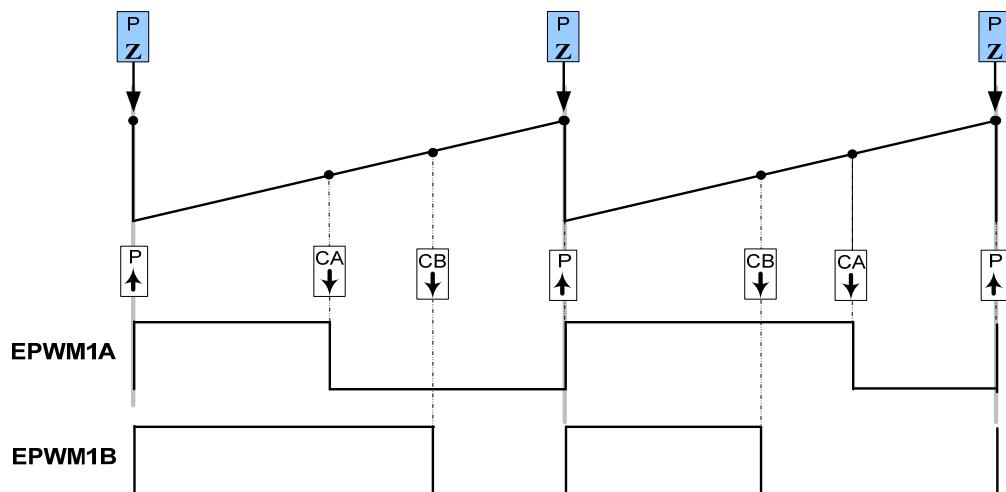

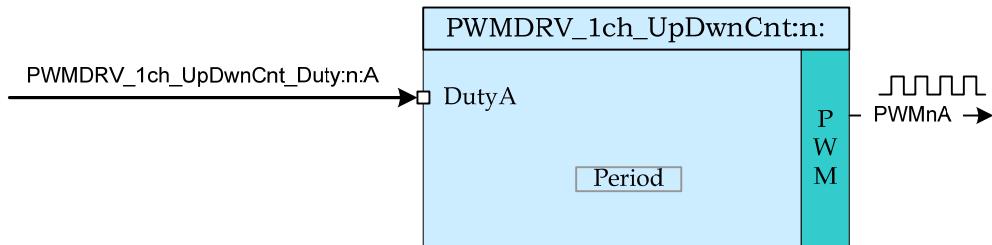

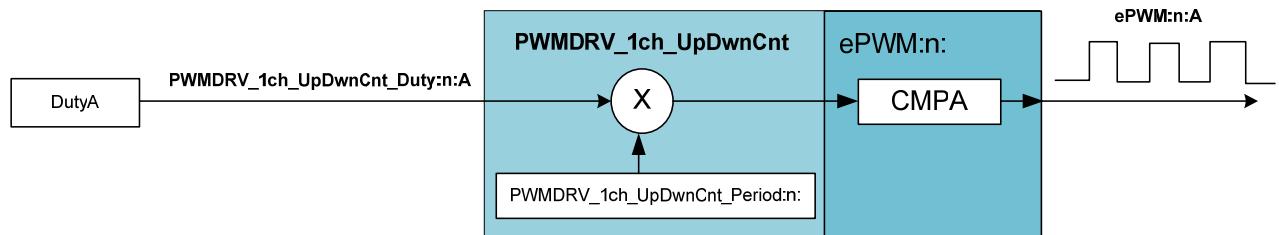

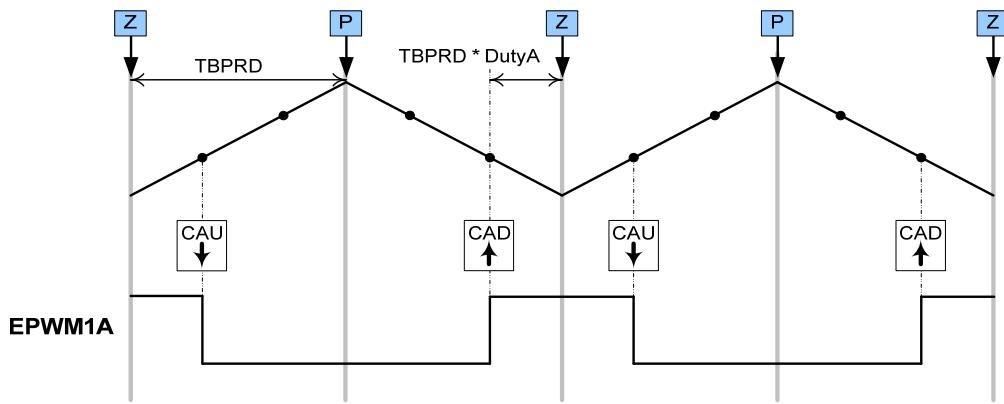

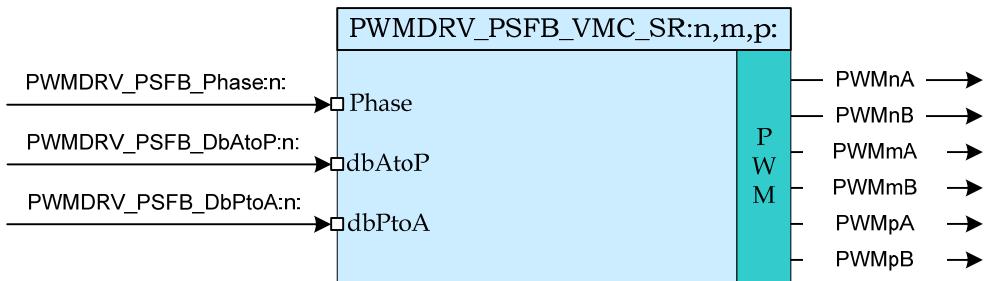

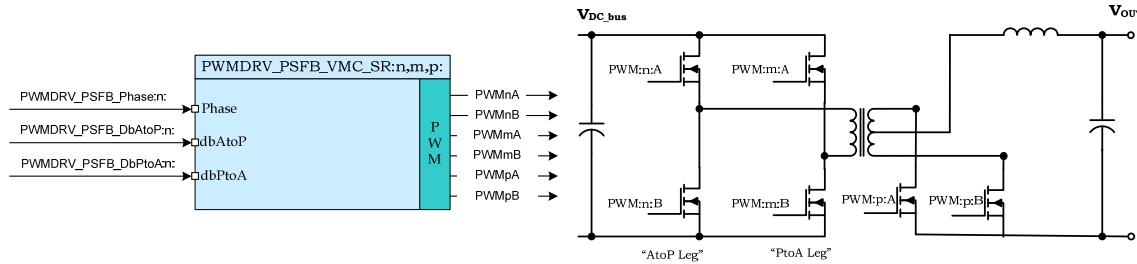

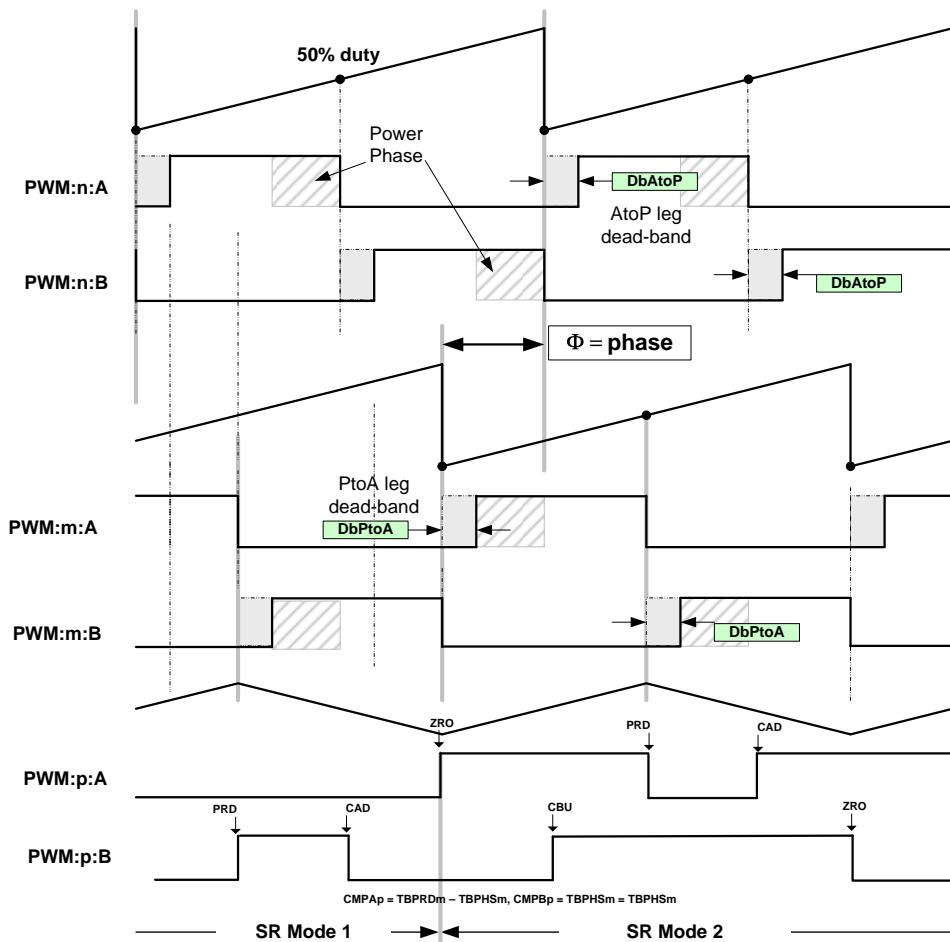

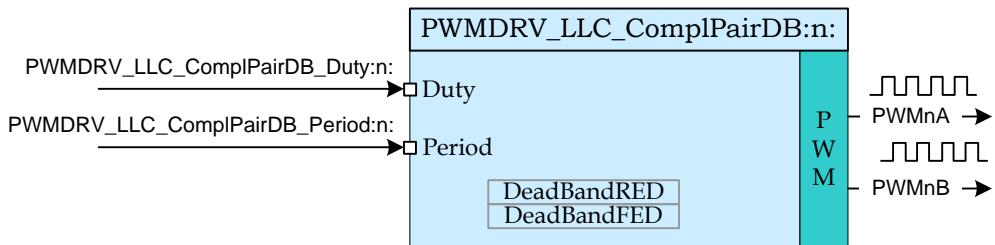

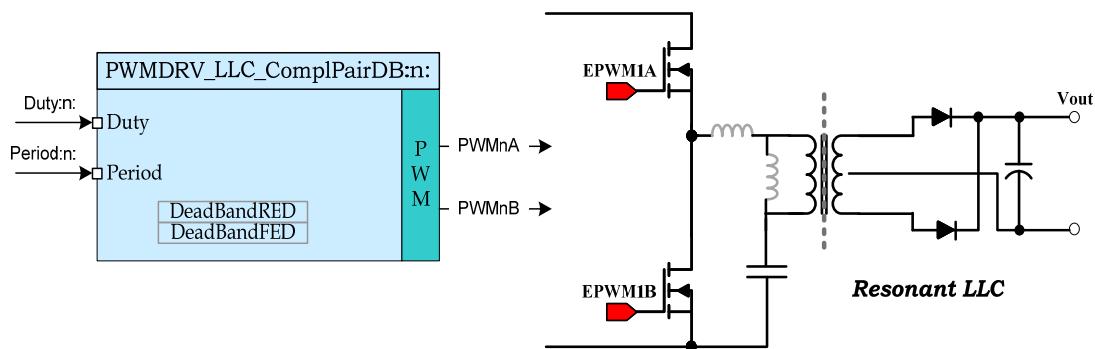

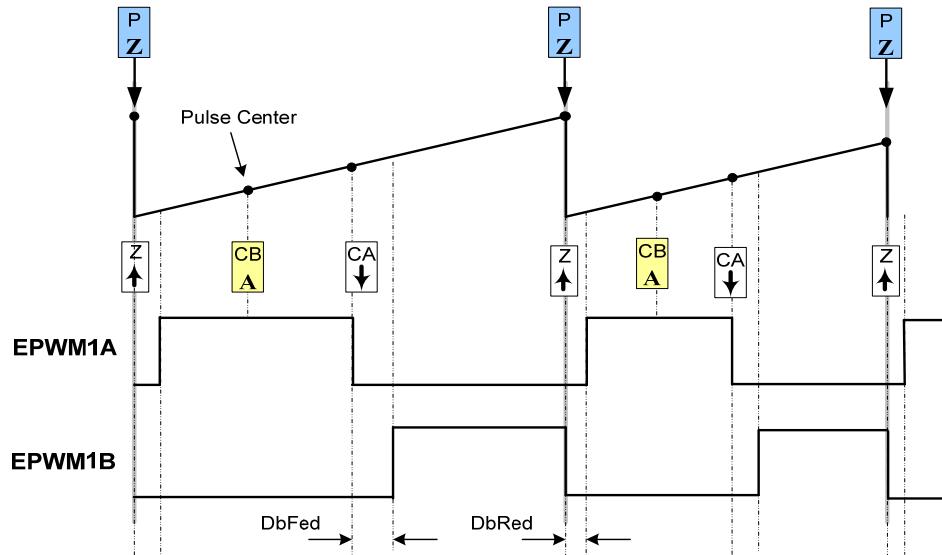

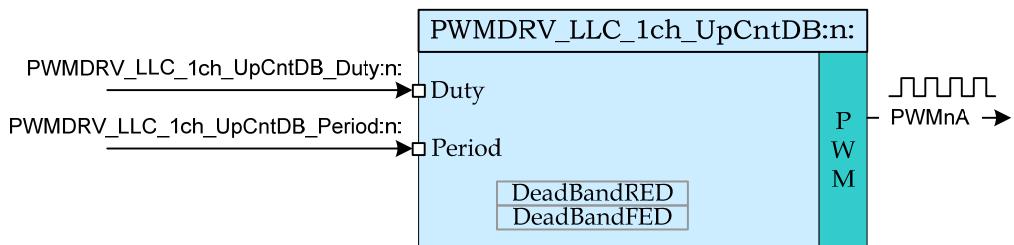

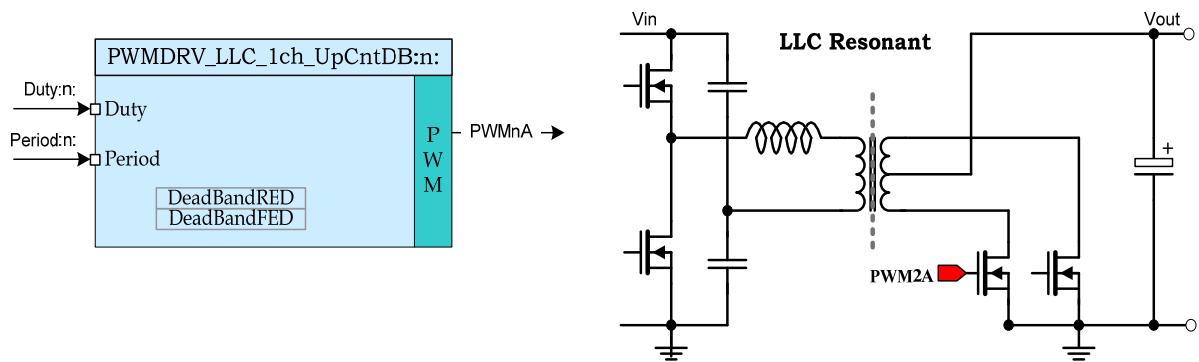

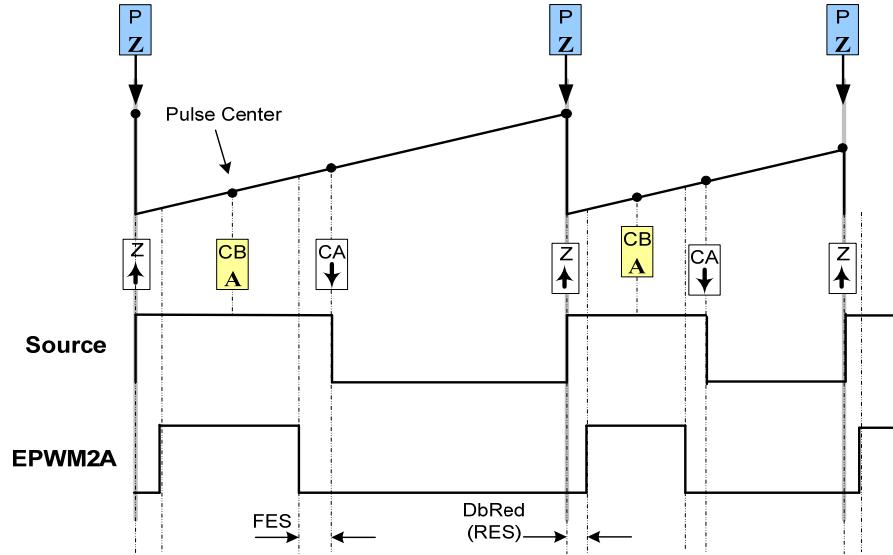

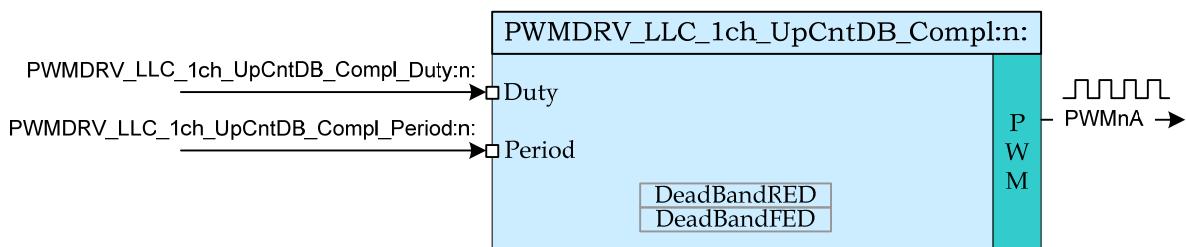

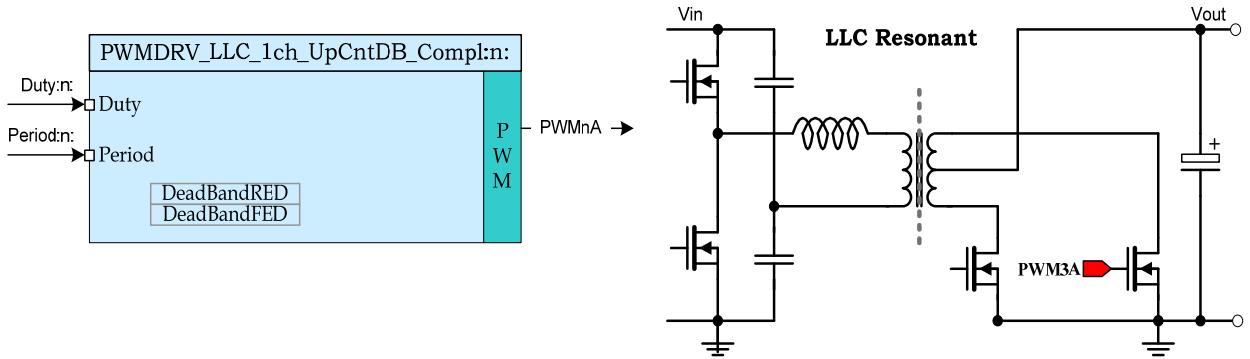

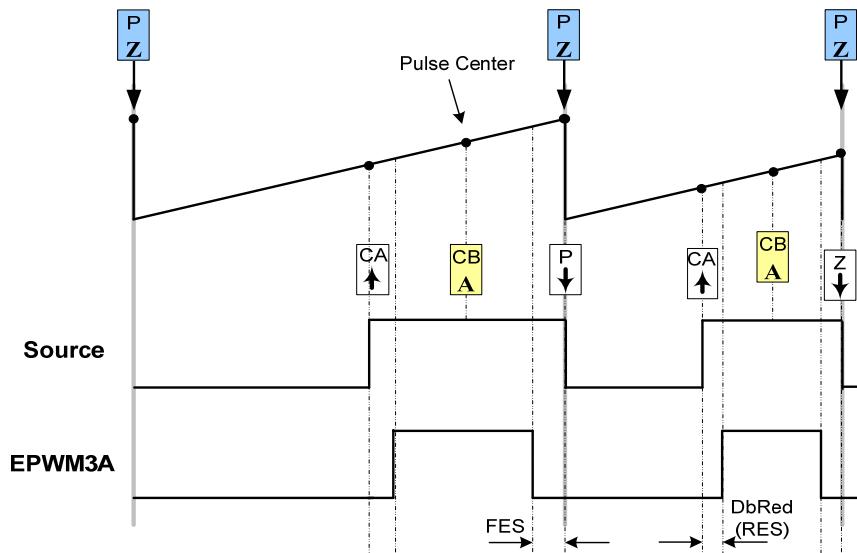

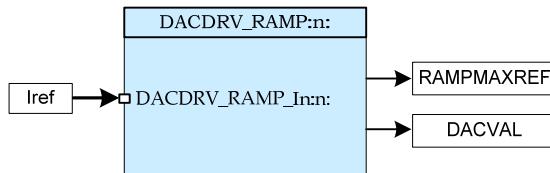

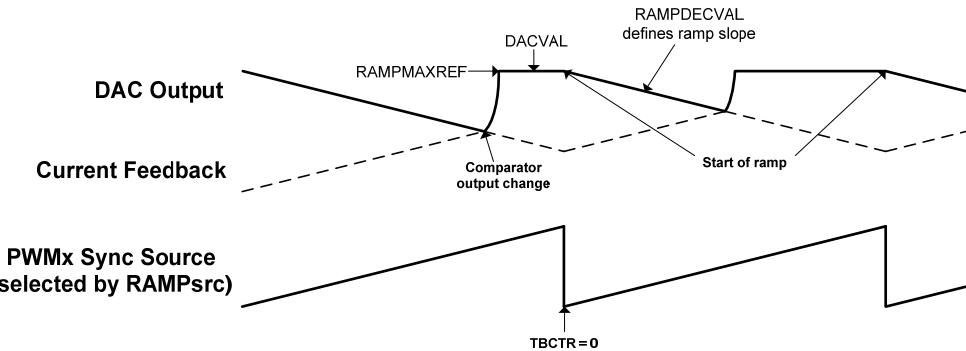

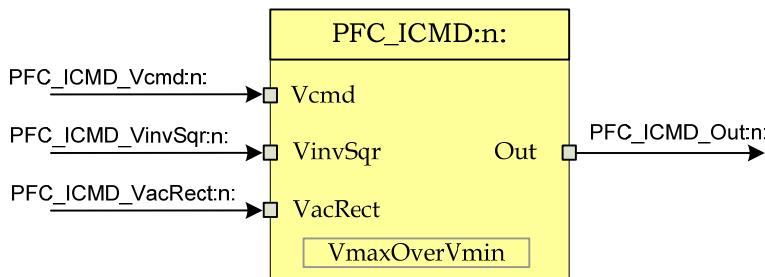

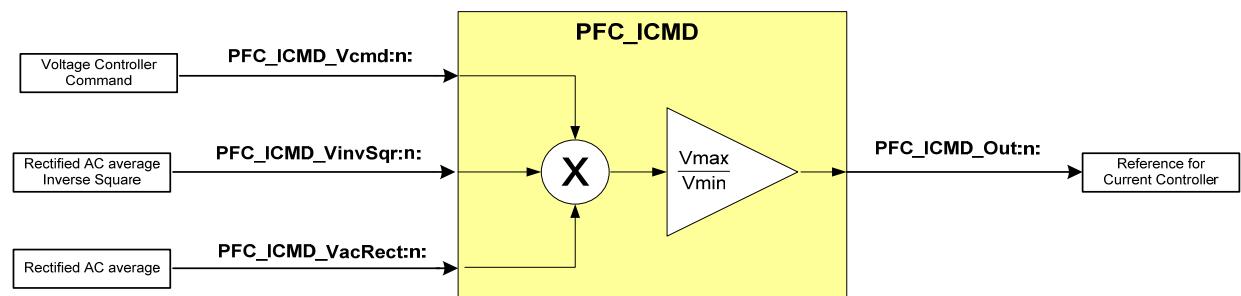

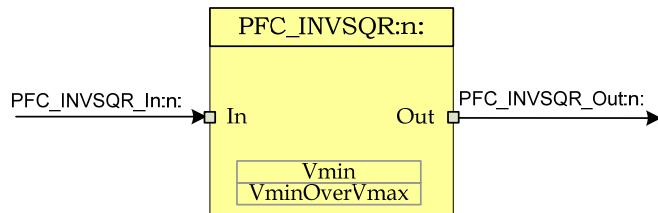

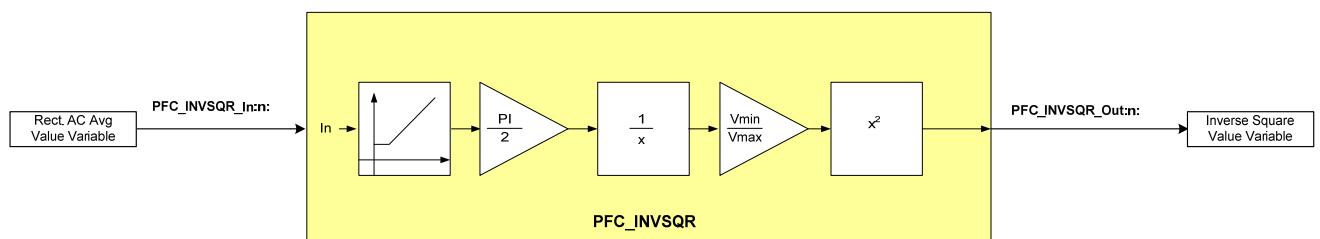

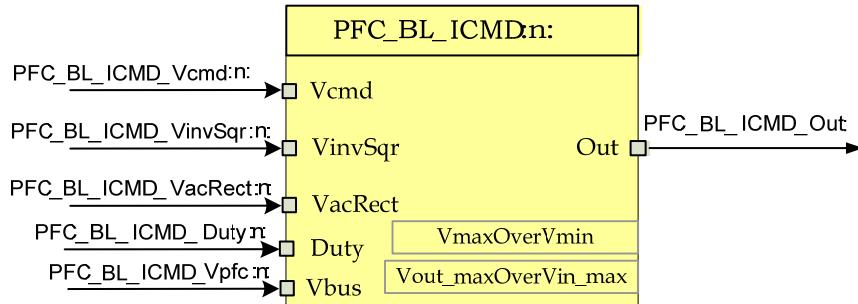

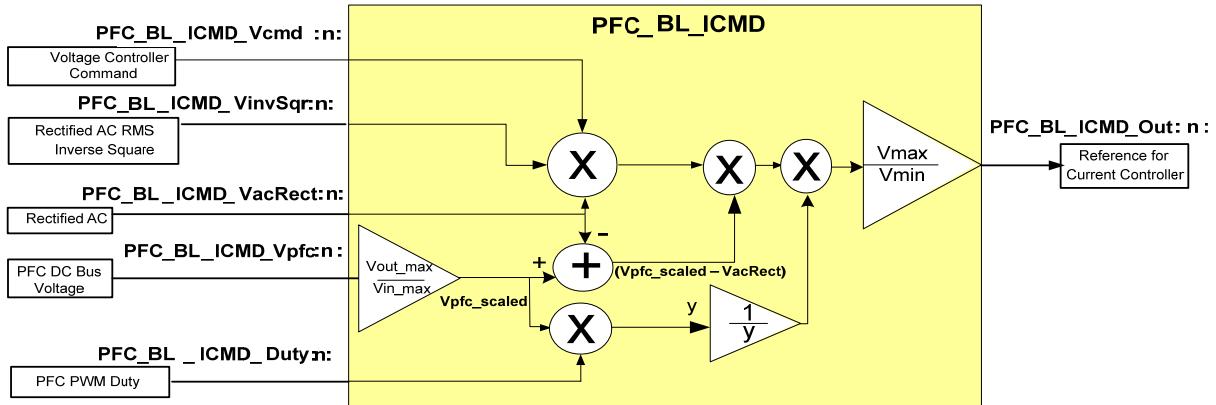

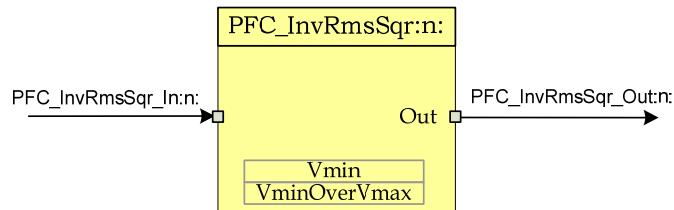

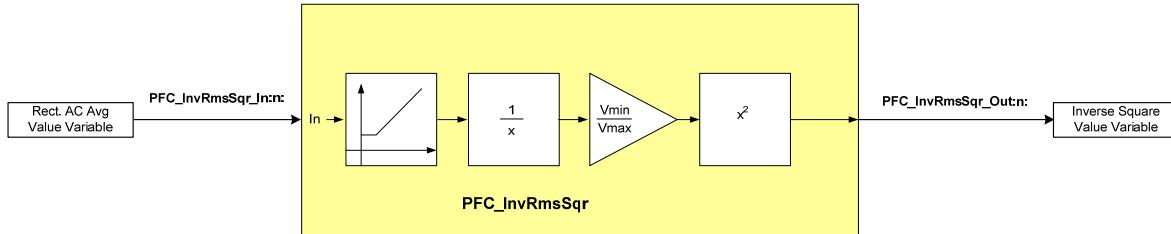

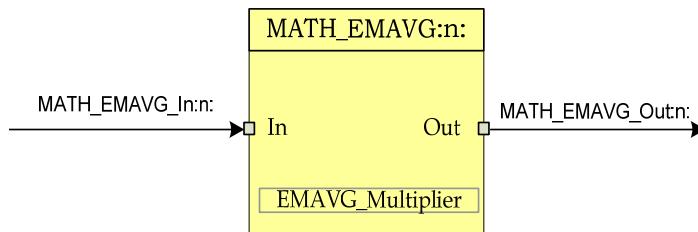

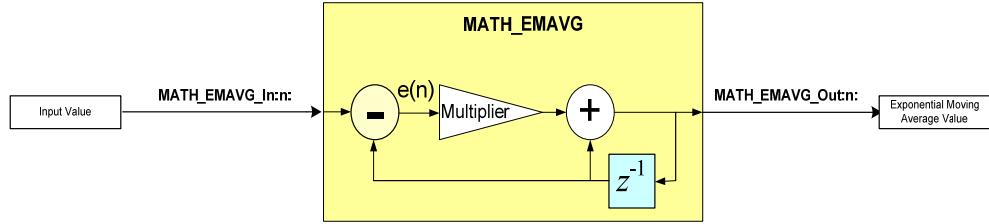

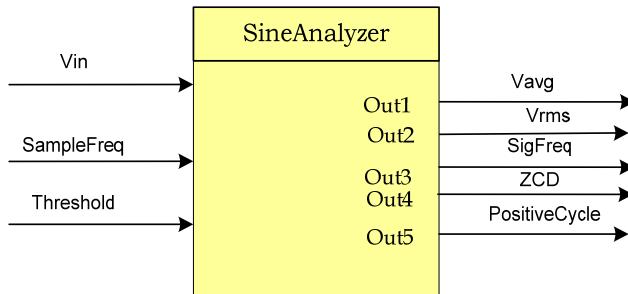

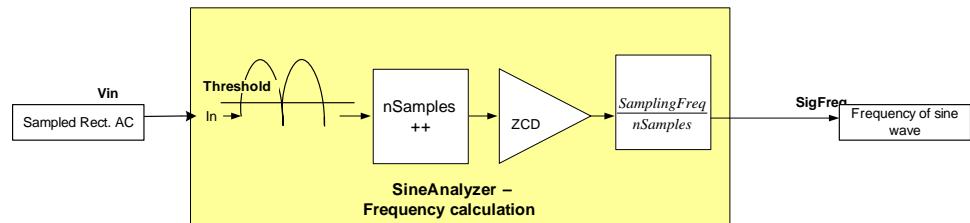

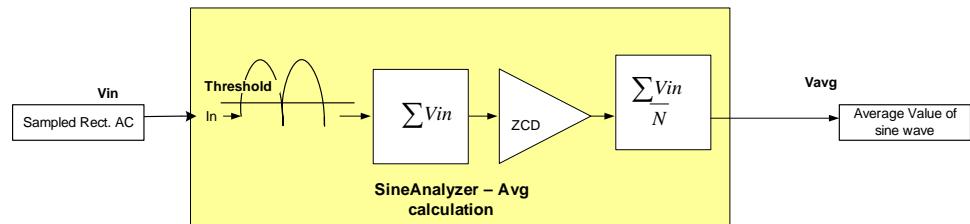

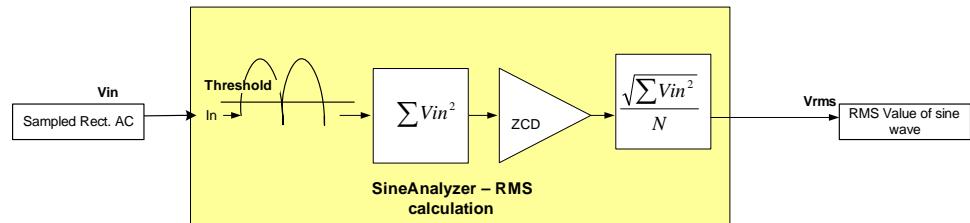

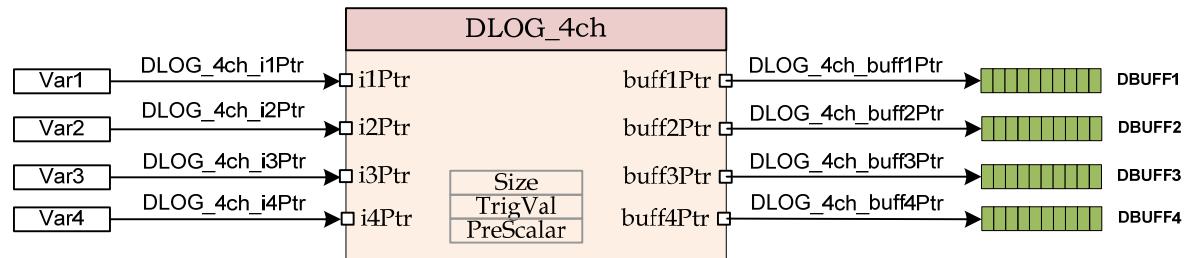

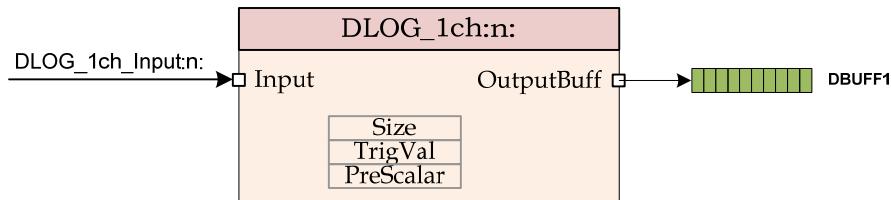

| ADCDRV_8ch_RltF                             | Output<br>Pointer | Pointer to 32 bit fixed point data location<br>storing the result of the module. | Q24: [0, 1)                                                               |