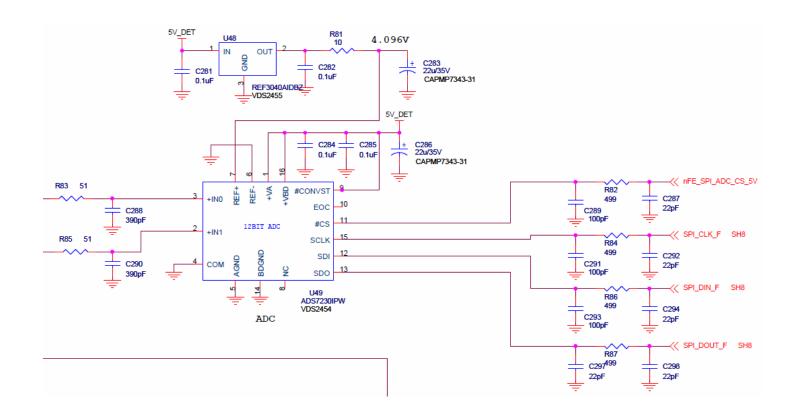

## **ADC ADS7230 Test Results**

VREF is tied to 4096 mV for 12-bit ADC, so the read result is supposed to follow the input

| Channel 0  |           | Channel 1  |           |

|------------|-----------|------------|-----------|

| Input (mV) | Read (mV) | Input (mV) | Read (mV) |

| 0          | 1152      | 0          | 16        |

| 250        | 848       | 500        | 3840      |

| 500        | 560       | 1000       | 3600      |

| 750        | 288       | 1500       | 3568      |

| 1000       | 0         | 2000       | 3504      |

| 1250       | 3808      | 2500       | 3456      |

| 1500       | 3520      | 3000       | 3392      |

| 1750       | 3232      | 3500       | 3328      |

| 2000       | 2944      | 4000       | 3232      |

| 2250       | 2624      | 4500       | 4080      |

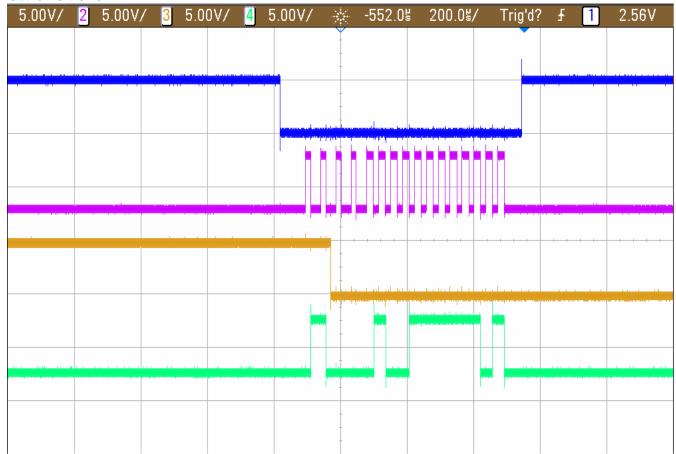

## Init

- 1. Write 16-bit 0xE000 to reset the chip

- 2. Write 16-bit 0xE4FD for config data 0x4FD with:, verified by readback with exactly the same data written to ensure the right clock phase and polarity for SPI bus of the chip

- a. Manual Channel Select

- b. Internal Clock

- c. Auto Trigger

- d. No TAG bit

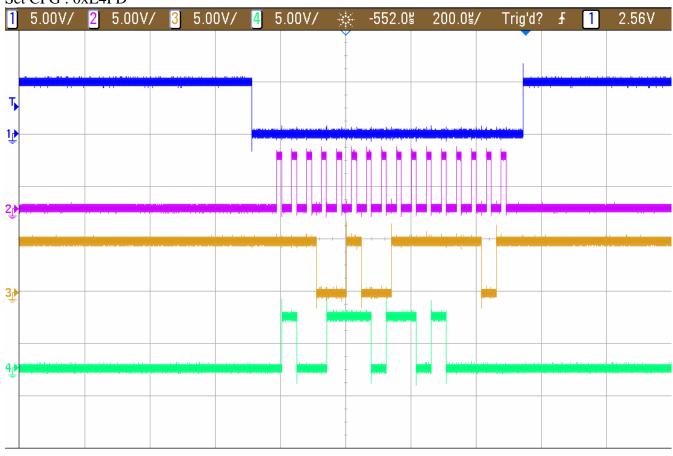

- 3. Read Result with 2 operations

- a. Write 4-bit channel number

- b. Write 4-bit read cmd 0xD and Read 12-bit result (repeat 4)

- 4. Read Result with 1 operation : write 4-bit channel number and read 12-bit result (repeat 4)

Both ways give almost identical results.

In read operation, the chip sends out at falling edge, so the host MCU must read at rising edge.

Set CFG: 0xE4FD