# Atrua Wings<sup>™</sup> ATW300 Family Fingerprint Touch Sensor Data Sheet

## **KEY FEATURES**

#### Low Power Consumption

- 1.4 mA avg. operating current

- 1.1 mA avg. navigation operating current

- 2.6 µA finger detection current

- 0.2 µA power down current

#### High Performance

- Up to 48 cm/sec swipe/movement rate

- Acquisition rate greater than 3,700 frames per sec. (512 bytes per frame)

- Compact Size

- 0.56 x 8.73 mm active sensing area

- 2.5 x 14.5 x 1.06 mm (1.32 mm package caps) package size

- Integrated CLK & Over-Current Protection Circuits

- Reduces component count and BOM cost

- Minimizes total solution board area

#### I/O Interface Flexibility

- 8-bit parallel MCU interface

- High Speed Serial Peripheral Interface (SPI)

- Low Voltage

- 1.8 V 3.3 V I/O

- 2.5 V 3.3 V core

#### Highly Rugged

- ± 20 kV ESD protection (Exceeds max. IEC61000-4-2 level)

- Withstands over 20 million swipes

- Abrasion & corrosion resistant

#### Adaptable Sensitivity

Automatic gain control for optimized gray-scale image with wide range of finger, skin & environmental conditions

#### Green/RoHS Compliant

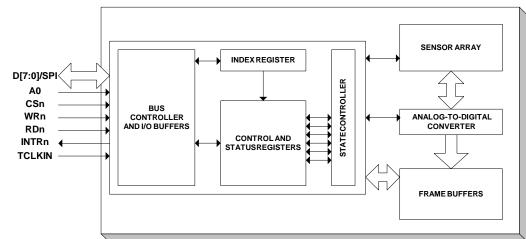

#### **BLOCK DIAGRAM**

# **TYPICAL APPLICATIONS**

ATW300 family's low cost, small size and low power consumption make it especially suited for use in mobile device applications such as:

- Mobile phones

- Smart cards

- Portable MP3 and media players

- Secure storage products

- Portable gaming devices

- PDAs

- Mobile computing devices and peripherals

- Portable products that benefit from small, feature-rich controls

## QUICK TIME-TO-MARKET

Extending the ATW300's market-leading easeof-integration, Atrua provides a comprehensive set of hardware and software support tools for rapid application development:

- Evaluation Kit

- Software Development Kit

- Hardware Development Kit for Embedded Systems

### **General Description**

The ATW300 family of fingerprint touch sensors (ATW3xx) is the sensor portion of the Atrua Wings<sup>™</sup> touch processing system. The system consists of:

- Touch sensors small, low cost and low power sensors that provide information on finger features and movement.

- Algorithms fingerprint recognition, navigation and control functions that are highly precise and accurate and operate in a very CPU- and memory-efficient manner.

The ATW3xx touch sensor creates partial images (frames) of the finger by sensing the ridges and valleys on the finger as it is moved or "swept" across its surface. This small Adaptive Capacitance™ sensor provides high performance and low power consumption through an integrated 124 x 8 sensing array of metal electrodes. Ridges and valleys on the finger yield varying capacitance values across the array, which are read to form a partial image of the fingerprint. Internal circuits within the sensor die convert the sensed data into a stream of digital data (a frame) that is presented to the host microprocessor via an 8-bit bidirectional bus interface, which is compatible with most microprocessors, or through a high-speed SPI interface.

There are two key classes of algorithms that execute on the host processor and comprise the core functions of this fingerprint touch processing system:

- Fingerprint Authentication

- Control and Navigation

These algorithms operate on the data streamed from the sensor. Authentication extracts minutiae features used for fingerprint verification, and matches the minutiae pattern to the template for the user's enrolled finger. The navigation/control algorithms analyze finger motions to provide control functions. Optimized for use in mobile devices, the low cost, small physical size and minimal power consumption of the ATW3xx touch sensor simplify its integration into mobile phones and other small mobile devices. The ATW3xx integrates the typically external over-current protection circuit to enable significant BOM cost savings and to further minimize the board area required for the total solution.

Additionally, the ATW3xx has an integrated analog-to-digital converter to digitize the sensed data and an automatic gain control (AGC) function that provides high quality fingerprint images from all types of skin, dry to moist, in a wide range of climatic conditions, even cold and dry.

In addition to the sensor's low power requirements, the end system's power consumption can be further minimized by utilizing one of the ATW3xx's advanced finger detect modes. These modes are designed to analyze on-sensor the finger's characteristics and wake the host CPU only after the sensor concludes that contact was made by an actual finger, not a foreign object. This reduces the need to unnecessarily wake the CPU subsystem, thus saving even more power.

The ATW3xx touch sensor is fabricated in standard CMOS technology and is provided in a Green/RoHS compliant LGA package. The sensor surface is protected by a special abrasion and chemical-resistant coating to provide long life with high reliability.

#### Conventions

Unless otherwise noted, a positive logic (active High) convention is assumed throughout this document. A lowercase 'n' following a signal name (e.g., INTRn) indicates that the signal is active Low.

The designation 0xNNNN indicates a hexadecimal number.

The designation 0bNNNN indicates a binary number.

| Name   | Туре           | Description                                                                                                                                                                                                                                                                                                                |

|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | Bi-directional | 8-bit Mode:<br>Data bus with CMOS inputs. These pins provide an 8-bit data path<br>for read and write operations. The bus is in the high-impedance state<br>when CSn or RDn is negated.                                                                                                                                    |

|        |                | <b>SPI Mode:</b><br>D7/MISO functions as the MISO (Master In Slave Out). Data is<br>shifted out of the SPI slave and into the SPI master.                                                                                                                                                                                  |

|        |                | D6/MOSI functions as the MOSI (Master Out Slave In). Data is shifted out of the SPI master and into the SPI slave.                                                                                                                                                                                                         |

|        |                | D5/SCK_INV selects the polarity of SCK. When SCK_INV is Low,<br>data is shifted out of the MISO on the falling edge of SCK and the<br>MOSI is sampled on the rising edge of SCK. When SCK_INV is High,<br>data is shifted out of the MISO on the rising edge of SCK and the<br>MOSI is sampled on the falling edge of SCK. |

| A0/SCK | Input          | 8-bit Mode:<br>Address. CMOS input.<br>When A0 is Low, the Index Address register (IDX_REG) is selected<br>as the source/destination for read and write transactions. When A0 is<br>High, the indexed register (see Functional Description) is selected as<br>the source/destination for read and write transactions.      |

|        |                | SPI Mode:<br>SPI Clock. CMOS input.                                                                                                                                                                                                                                                                                        |

|        |                | When SCK_INV is Low, data is shifted out the MISO on the falling<br>edge of SCK and the MOSI is sampled on the rising edge of SCK.<br>When SCK_INV is High, data is shifted out the MISO on the rising<br>edge of SCK and the MOSI is sampled on the falling edge of SCK.                                                  |

# **Signal Descriptions**

| 00m/000          | I.e 4      | 0 hit Mada                                                                                                                            |

|------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| CSn/SCSn         | Input      | 8-bit Mode:                                                                                                                           |

|                  |            | Chip Select, active Low. CMOS input.                                                                                                  |

|                  |            | This input must be apported to read data from any with data to the                                                                    |

|                  |            | This input must be asserted to read data from or write data to the                                                                    |

|                  |            | ATW3xx. When High, the data bus is in the high impedance state.                                                                       |

|                  |            | SPI Mode:                                                                                                                             |

|                  |            | Slave Chip Select, active Low. CMOS input.                                                                                            |

|                  |            | olave only ocleat, active Low. Olivioo input.                                                                                         |

|                  |            | Drive SCSn Low to select the device as an SPI slave. Drive SCSn                                                                       |

|                  |            | High to deselect the device, reset the SPI, and to place the MISO in                                                                  |

|                  |            | the high impedance state.                                                                                                             |

| RDn              | Input      | 8-bit Mode:                                                                                                                           |

|                  |            | Read Enable, active Low. CMOS input.                                                                                                  |

|                  |            |                                                                                                                                       |

|                  |            | This input must be asserted for read operations and negated for write                                                                 |

|                  |            | operations. When High, data outputs from the device are disabled                                                                      |

|                  |            | and the data bus pins are placed in the high impedance state.                                                                         |

|                  |            |                                                                                                                                       |

|                  |            | SPI Mode:                                                                                                                             |

|                  |            | RDn must be driven Low. Drive both RDn and WRn Low to place the                                                                       |

|                  |            | device into SPI mode. The device returns to 8-bit Mode if either RDn                                                                  |

|                  | La sa sa t | or WRn is driven High.                                                                                                                |

| WRn              | Input      | 8-bit Mode:                                                                                                                           |

|                  |            | Write Enable, active Low. CMOS input.                                                                                                 |

|                  |            | Controls writing of commands or data to the ATW3xx. A write                                                                           |

|                  |            | operation takes place when WRn is asserted while CSn is Low and                                                                       |

|                  |            | RDn is High. The data is latched on the rising edge of WRn.                                                                           |

|                  |            |                                                                                                                                       |

|                  |            | SPI Mode:                                                                                                                             |

|                  |            | WRn must be driven Low. Drive both RDn and WRn Low to place the                                                                       |

|                  |            | device into SPI mode. The device returns to 8-bit Mode if either RDn                                                                  |

|                  |            | or WRn is driven High.                                                                                                                |

| INTRn            | Output     | Interrupt Request, active Low. INTRn is asserted if interrupts are                                                                    |

|                  |            | enabled and an interrupt event takes place.                                                                                           |

| TCLKIN           | Input      | External Clock Input. The ATW3xx has an internal clock and does                                                                       |

|                  |            | not require an external clock input. This input is for testing only and                                                               |

|                  | D.         | should be left unconnected for normal operation.                                                                                      |

|                  | Power      | Core Power.                                                                                                                           |

| V <sub>SSC</sub> | Ground     | Core Ground.                                                                                                                          |

|                  | Power      | I/O Power.                                                                                                                            |

|                  | Ground     | I/O Ground.                                                                                                                           |

| SHGND            | Ground     | <b>ESD Ground.</b> These pins are intended to provide a discharge path during an electrostatic discharge event. Connect these pins to |

|                  |            | during an electrostatic discharge event. Connect these pins to                                                                        |

| 1                |            | chassis ground.                                                                                                                       |

| Symbol            | Parameter                                                               | Value                           | Unit |

|-------------------|-------------------------------------------------------------------------|---------------------------------|------|

| T <sub>STG</sub>  | Storage Temperature                                                     | -40 to +125                     | O°   |

| T <sub>BIAS</sub> | Ambient Temperature with Power Applied                                  | -40 to +85                      | °C   |

| TL                | Lead Temperature, max 20s duration <sup>2</sup>                         | +250                            | O°   |

|                   | Voltage on Pin with Respect to V <sub>SSO</sub> :                       |                                 |      |

| V <sub>IN</sub>   | V <sub>DDO</sub>                                                        | -0.5 to +4.0                    | V    |

|                   | All Other Pins                                                          | -0.5 to (V <sub>DD</sub> + 0.5) | V    |

| l <sub>os</sub>   | Output Short Circuit Current                                            | 200                             | mA   |

| ESD (HBM)         | Electrostatic Discharge, Human Body Model,<br>EIA/JEDEC JESD22-A114     | ± 2000                          | V    |

| ESD (CDM)         | Electrostatic Discharge, Charged Device Model,<br>EIA/JEDEC JESD22-C101 | ±1800                           | V    |

| Surface ESD       | Electrostatic Air Discharge, IEC-61000-4-2 <sup>3</sup>                 | ± 20                            | kV   |

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

Notes:

1. Conditions in excess of those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this data sheet is not implied. Exposure of the device to absolute maximum rating conditions for extended periods may affect device reliability.

2. Reflow details per Lead-Free IR Reflow Profile in IPC/JEDEC J-STD-020.

3. Per internal procedure for testing the component on a standard development board per IEC-61000-4-2.

## **RECOMMENDED OPERATING CONDITIONS<sup>1</sup>**

| Symbol           | Parameter                                       | Value        | Unit |

|------------------|-------------------------------------------------|--------------|------|

| T <sub>A</sub>   | Ambient Operating Temperature                   | -20 to +70   | °C   |

| V <sub>DDC</sub> | Core Power Operating Supply Voltage             | +2.5 to +3.3 | V    |

| V <sub>DDO</sub> | I/O Power Operating Supply Voltage <sup>2</sup> | +1.8 to +3.3 | V    |

| MSL              | JEDEC Moisture Sensitivity Level                | 3            |      |

Notes:

1. Recommended Operating Conditions define those limits between which the functionality of the device is guaranteed.

2.  $V_{DDO}$  can be at a lower supply level than  $V_{DDC}$  if the application requires. Allowed modes of operation are in the following table.

## ALLOWED POWER SUPPLY VOLTAGE COMBINATIONS

| V <sub>DDO</sub> | V <sub>DDC</sub> |

|------------------|------------------|

| 1.8 V            | 2.5 V or 3.3 V   |

| 2.5 V            | 2.5 V or 3.3 V   |

| 3.3 V            | 3.3 V            |

Notes:

1.  $V_{\text{DDC}}$  must be equal to or higher than  $V_{\text{DDO}}.$

2.  $V_{DDO}$  is not allowed to be higher than  $V_{DDC}$ .

# **POWER SEQUENCING**

$V_{DDC}$  and  $V_{DDO}$  should be applied at the same time. If  $V_{DDC}$  and  $V_{DDO}$  cannot be applied concurrently, then  $V_{DDC}$  must be applied before applying voltage to  $V_{DDO}$  or any signal pin.

| Parameter         | Description                                                                                                                                           | Test Conditions                                 | Min                       | Тур | ical | Max                       | Unit |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------|-----|------|---------------------------|------|

| V <sub>DDC</sub>  | Core Supply Voltage                                                                                                                                   |                                                 | 2.25                      | 2.5 | 2.5  | 2.75                      | V    |

| V <sub>DDO</sub>  | I/O Supply Voltage                                                                                                                                    |                                                 | 1.65                      | 1.8 | 2.5  | 2.75                      | V    |

| I <sub>I</sub>    | Input Leakage                                                                                                                                         | $0 \le V_{IN} \le V_{DDO},$<br>$V_{DDO} = Max$  | -3                        |     |      | 3                         | μA   |

| l <sub>oz</sub>   | Input current for outputs in<br>Hi-Z                                                                                                                  | $0 \le V_{OUT} \le V_{DDO},$<br>$V_{DDO} = Max$ | -1                        |     |      | 1                         | μA   |

| I <sub>DD1</sub>  | V <sub>DD</sub> Stand-by without partial<br>power down,<br>Quiescent Current                                                                          | V <sub>DDC</sub> = Max                          |                           | 15  | 20   | 72                        | μA   |

| I <sub>DD2</sub>  | V <sub>DD</sub> Peak Operating Current <sup>4</sup>                                                                                                   | V <sub>DDC</sub> = Max                          |                           | 3.9 | 3.9  | 6.8                       | mA   |

| I <sub>DD3</sub>  | V <sub>DD</sub> Average Operating<br>Current, 500 fps                                                                                                 | V <sub>DDC</sub> = Typ                          |                           | 1.4 | 1.5  |                           | mA   |

| I <sub>DD4</sub>  | V <sub>DD</sub> Average Operating<br>Current, 250 fps (Navigation)                                                                                    | V <sub>DDC</sub> = Typ                          |                           | 1.1 | 1.1  |                           | mA   |

| I <sub>DD5</sub>  | V <sub>DD</sub> Average Operating<br>Current with Finger Detect<br>Surface Contact Detect State<br>Active (Monitoring)                                | V <sub>DDC</sub> = Max                          |                           | 2.6 | 2.7  | 27                        | μA   |

| I <sub>DD6</sub>  | V <sub>DD</sub> Peak Operating Current <sup>4</sup><br>with Finger Detect Mode 3<br>Active (Monitoring) or Mode 2<br>prior to asserting the interrupt | V <sub>DDC</sub> = Max                          |                           | 3.9 | 3.9  | 6.8                       | mA   |

| I <sub>DD7</sub>  | V <sub>DD</sub> Average Operating<br>Current with Finger Detect<br>Mode 3 Active (Monitoring,<br>Interval=400 ms)                                     | V <sub>DDC</sub> = Max                          |                           | 3.9 | 4.0  | 45                        | μA   |

| I <sub>DD8</sub>  | V <sub>DD</sub> Quiescent Current with<br>Finger Detect Mode 1, 2 or 3<br>Triggered (After interrupt<br>asserted)                                     | V <sub>DDC</sub> = Max                          |                           | 23  | 23   | 60                        | μA   |

| I <sub>DD9</sub>  | V <sub>DD</sub> Partial Power Down,<br>Quiescent Current                                                                                              | V <sub>DDC</sub> = Max                          |                           | 0.7 | 1.5  | 19                        | μA   |

| I <sub>DD10</sub> | V <sub>DD</sub> Full Power Down<br>Quiescent Current                                                                                                  | V <sub>DDC</sub> = Max                          |                           | 0.2 | 0.2  | 3                         | μA   |

| V <sub>IL</sub>   | Input Low Voltage                                                                                                                                     |                                                 |                           |     |      | 0.3 x<br>V <sub>DDO</sub> | V    |

| VIH               | Input High Voltage                                                                                                                                    |                                                 | 0.7 x<br>V <sub>DDO</sub> |     |      |                           | V    |

| V <sub>OL</sub>   | Low-Level Output Voltage                                                                                                                              | I <sub>OL</sub> = Min                           |                           |     |      | 0.2 x<br>V <sub>DDO</sub> | V    |

| V <sub>OH</sub>   | High-Level Output Voltage                                                                                                                             | I <sub>OH</sub> = Max                           | 0.8 x<br>V <sub>DDO</sub> |     |      |                           | V    |

# DC CHARACTERISTICS (2.5 V Core) <sup>1, 2, 3</sup>

Notes:

1. All maximum  $I_{DD}$  specifications in table are tested with  $V_{DD} = V_{DD}$  Max and ambient temperature = 85°C.

2. All typical specifications in table are measured with ambient temperature = 25°C.

3. All operating  $I_{DD}$  specifications in table are tested with 2X clock.

4. Peak operating current ( $I_{DD2}$ ,  $I_{DD6}$ ) is observed when performing an A/D conversion, which lasts nominally 256 µs.

# DC CHARACTERISTICS (3.3 V Core) <sup>1, 2, 3</sup>

| Parameter         | Description                                                                                                                                           | Test Conditions                                 | Min                    | Тур | Max                    | Unit |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------|-----|------------------------|------|

| V <sub>DDC</sub>  | Core Supply Voltage                                                                                                                                   |                                                 | 3.0                    | 3.3 | 3.63                   | V    |

| V <sub>DDO</sub>  | I/O Supply Voltage                                                                                                                                    |                                                 | 1.65                   | 3.3 | 3.63                   | V    |

| I <sub>I</sub>    | Input Leakage                                                                                                                                         | $0 \le V_{IN} \le V_{DDO},$<br>$V_{DDO} = Max$  | -3                     |     | 3                      | μA   |

| I <sub>OZ</sub>   | Input current for outputs in<br>Hi-Z                                                                                                                  | $0 \le V_{OUT} \le V_{DDO},$<br>$V_{DDO} = Max$ | -1                     |     | 1                      | μA   |

| I <sub>DD1</sub>  | V <sub>DD</sub> Stand-by without partial<br>power down,<br>Quiescent Current                                                                          |                                                 |                        | 40  | 95                     | μA   |

| I <sub>DD2</sub>  | V <sub>DD</sub> Peak Operating Current <sup>4</sup>                                                                                                   | V <sub>DDC</sub> = Max                          |                        | 5   | 9                      | mA   |

| I <sub>DD3</sub>  | V <sub>DD</sub> Average Operating Current,<br>500 fps                                                                                                 | V <sub>DDC</sub> = Typ                          |                        | 2   |                        | mA   |

| I <sub>DD4</sub>  | V <sub>DD</sub> Average Operating Current,<br>250 fps (Navigation)                                                                                    | V <sub>DDC</sub> = Typ                          |                        | 1.7 |                        | mA   |

| I <sub>DD5</sub>  | V <sub>DD</sub> Average Operating Current<br>with Finger Detect Surface<br>Contact Detect State Active<br>(Monitoring)                                | V <sub>DDC</sub> = Max                          |                        | 4.6 | 36                     | μA   |

| I <sub>DD6</sub>  | V <sub>DD</sub> Peak Operating Current <sup>4</sup><br>with Finger Detect Mode 3<br>Active (Monitoring) or Mode 2<br>prior to asserting the interrupt | V <sub>DDC</sub> = Max                          |                        | 5   | 9                      | mA   |

| I <sub>DD7</sub>  | V <sub>DD</sub> Average Operating Current<br>with Finger Detect Mode 3<br>Active (Monitoring, Interval=400<br>ms)                                     | V <sub>DDC</sub> = Max                          |                        | 4.4 | 60                     | μA   |

| I <sub>DD8</sub>  | V <sub>DD</sub> Quiescent Current with<br>Finger Detect Mode 1, 2 or 3<br>Triggered (After interrupt<br>asserted)                                     | V <sub>DDC</sub> = Max                          |                        | 38  | 80                     | μA   |

| I <sub>DD9</sub>  | V <sub>DD</sub> Partial Power Down,<br>Quiescent Current                                                                                              | V <sub>DDC</sub> = Max                          |                        | 1.6 | 25                     | μA   |

| I <sub>DD10</sub> | V <sub>DD</sub> Full Power Down Quiescent<br>Current                                                                                                  | V <sub>DDC</sub> = Max                          |                        | 0.2 | 4                      | μA   |

| VIL               | Input Low Voltage                                                                                                                                     |                                                 |                        |     | 0.3 x V <sub>DDO</sub> | V    |

| V <sub>IH</sub>   | Input High Voltage                                                                                                                                    |                                                 | 0.7 x V <sub>DDO</sub> |     |                        | V    |

| V <sub>OL</sub>   | Low-Level Output Voltage                                                                                                                              | I <sub>OL</sub> = Min                           |                        |     | 0.2 x V <sub>DDO</sub> | V    |

| V <sub>OH</sub>   | High-Level Output Voltage                                                                                                                             | I <sub>OH</sub> = Max                           | 0.8 x V <sub>DDO</sub> |     |                        | V    |

Notes:

1. All maximum  $I_{DD}$  specifications in table are tested with  $V_{DD} = V_{DD}$  Max and ambient temperature = 85°C. 2. All typical specifications in table are measured with ambient temperature = 25°C.

3. All operating  $I_{DD}$  specifications in table are tested with 2X clock.

4. Peak operating current (I<sub>DD2</sub>, I<sub>DD6</sub>) is observed when performing an A/D conversion, which lasts nominally 256 µs.

### ATW300 Fingerprint Touch Sensor Family Data Sheet

| Parameter       | Description                 | Test Conditions                  |                | Min | Max | Unit |

|-----------------|-----------------------------|----------------------------------|----------------|-----|-----|------|

|                 |                             |                                  | Strong Drivers |     | -6  | mA   |

|                 |                             | V <sub>DDO</sub> ≥ 2.25V         | Medium Drivers |     | -4  | mA   |

|                 | High-Level Output           |                                  | Weak Drivers   |     | -2  | mA   |

| I <sub>ОН</sub> | Current                     | 1.65V ≤ V <sub>DDO</sub> ≤ 1.95V | Strong Drivers |     | -3  | mA   |

|                 |                             |                                  | Medium Drivers |     | -2  | mA   |

|                 |                             |                                  | Weak Drivers   |     | -1  | mA   |

|                 |                             | V <sub>DDO</sub> ≥ 2.25V         | Strong Drivers | 6   |     | mA   |

|                 | Low-Level Output<br>Current |                                  | Medium Drivers | 4   |     | mA   |

| 1               |                             |                                  | Weak Drivers   | 2   |     | mA   |

| I <sub>OL</sub> |                             |                                  | Strong Drivers | 3   |     | mA   |

|                 |                             | $1.65V \le V_{DDO} \le 1.95V$    | Medium Drivers | 2   |     | mA   |

|                 |                             |                                  | Weak Drivers   | 1   |     | mA   |

Note: Default setting is "Strong Drivers".

# **KEY TO SWITCHING WAVEFORMS**

| WAVEFORM | INPUTS OUTPUTS                                          |  |  |  |

|----------|---------------------------------------------------------|--|--|--|

|          | Steady                                                  |  |  |  |

|          | Changing from H to L                                    |  |  |  |

|          | Changing from L to H                                    |  |  |  |

|          | Don't Care, Any Change Permitted Changing, State Unknow |  |  |  |

|          | Does Not Apply<br>State (Hi-Z)                          |  |  |  |

# **TEST CONDITIONS**

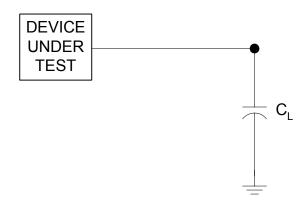

#### Figure 1. Test Setup

# **Table 1. AC Test Specifications**

| Test Condition                   | Value                            | Unit |  |

|----------------------------------|----------------------------------|------|--|

| Output Load                      | See Test Setup                   |      |  |

| Output Load Capacitance          | 15                               | pF   |  |

| Input Rise and Fall Times        | 5                                | ns   |  |

| Input Signal Low Level           | 0                                | V    |  |

| Input Signal High Level          | $0.9 x V_{DDO}$                  | V    |  |

| Input Timing Reference<br>Level  | $0.5 x V_{DDO}$                  | V    |  |

| Output Timing Reference<br>Level | $0.5 \mathrm{xV}_{\mathrm{DDO}}$ | V    |  |

# AC CHARACTERISTICS

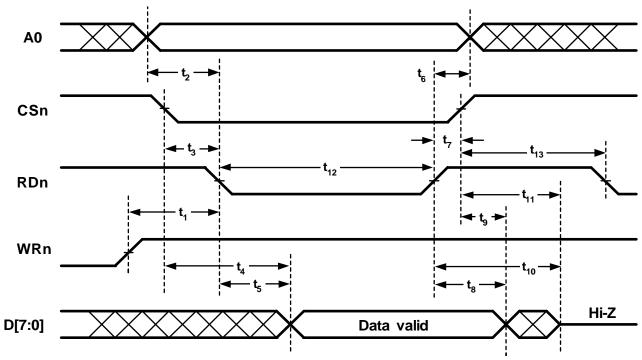

#### **Read Operation**

|                 | Parameter | Description                | Test<br>Setup         | Min | Max | Unit |

|-----------------|-----------|----------------------------|-----------------------|-----|-----|------|

| t <sub>1</sub>  | td(W-R)   | WRn High to RDn Low delay  |                       | 20  |     | ns   |

| t <sub>2</sub>  | tsu(A-R)  | A0 setup to RDn Low        |                       | 10  |     | ns   |

| t <sub>3</sub>  | tsu(S-R)  | CSn setup to RDn Low       |                       | 0   |     | ns   |

| t <sub>4</sub>  | ta(S)     | D[7:0] valid from CSn Low  | RDn ≤ V <sub>IL</sub> |     | 40  | ns   |

| t <sub>5</sub>  | ta(R)     | D[7:0] valid from RDn Low  | CSn ≤ V <sub>IL</sub> |     | 40  | ns   |

| t <sub>6</sub>  | th(R-A)   | A0 hold after RDn High     |                       | 5   |     | ns   |

| t <sub>7</sub>  | th(R-S)   | CSn hold after RDn High    |                       | 0   |     | ns   |

| t <sub>8</sub>  | th(R-Q)   | D[7:0] hold after RDn High |                       | 0   |     | ns   |

| t <sub>9</sub>  | th(R-S)   | D[7:0] hold after CSn High |                       | 0   |     | ns   |

| t <sub>10</sub> | tdis(R)   | D[7:0] Hi-Z after RDn High | CSn ≤ V <sub>IL</sub> |     | 20  | ns   |

| t <sub>11</sub> | tdis(S)   | D[7:0] Hi-Z after CSn High | RDn ≤ V <sub>IL</sub> |     | 20  | ns   |

| t <sub>12</sub> | tw(RL)    | RDn Low pulse width        | CSn ≤ V <sub>IL</sub> | 40  |     | ns   |

| t <sub>13</sub> | tw(RH)    | RDn High pulse width       | RDn ≤ V <sub>IL</sub> | 20  |     | ns   |

Figure 2. Read Operation Timing

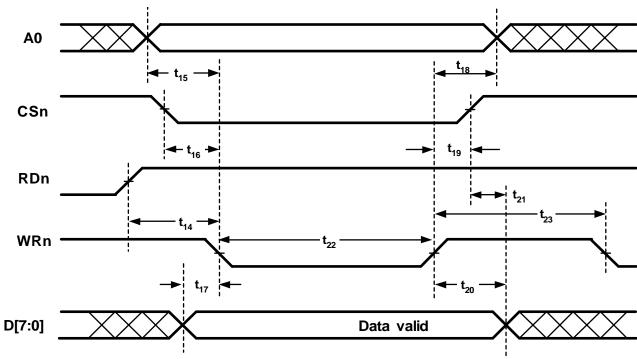

| Write           | • Operations |                                |     |     |      |

|-----------------|--------------|--------------------------------|-----|-----|------|

|                 | Parameter    | Description                    | Min | Max | Unit |

| t <sub>14</sub> | td(R-W)      | RDn High to WRn Low delay      | 20  |     | ns   |

| t <sub>15</sub> | tsu(A-W)     | A0 setup to WRn Low            | 10  |     | ns   |

| t <sub>16</sub> | tsu(S-W)     | CSn setup to WRn Low           | 10  |     | ns   |

| t <sub>17</sub> | tsu(D-W)     | Input data setup to WRn Low    | 10  |     | ns   |

| t <sub>18</sub> | th(W-A)      | A0 hold after WRn High         | 5   |     | ns   |

| t <sub>19</sub> | th(W-S)      | CSn hold after WRn High        | 5   |     | ns   |

| t <sub>20</sub> | th(W-D)      | Input data hold after WRn High | 5   |     | ns   |

| t <sub>21</sub> | th(W-S)      | Input data hold after CSn High | 5   |     | ns   |

| t <sub>22</sub> | tw(WL)       | WRn Low pulse width            | 20  |     | ns   |

| t <sub>23</sub> | tw(WH)       | WRn High pulse width           | 20  |     | ns   |

Figure 3. Write Operation Timings

|                 | Parameter | Description              | Test<br>Setup             | Min | Max | Unit |

|-----------------|-----------|--------------------------|---------------------------|-----|-----|------|

| t <sub>24</sub> | tw(KL)    | SCK Low pulse width      |                           | 35  |     | ns   |

| t <sub>25</sub> | tw(KH)    | SCK High pulse width     |                           | 35  |     | ns   |

| t <sub>26</sub> | ta(S)     | MISO valid from SCSn Low |                           |     | 25  | ns   |

| t <sub>27</sub> | tsu(D-K)  | MOSI setup to SCK High   |                           | 10  |     | ns   |

| t <sub>28</sub> | ta(K-Q)   | SCK Low to MISO valid    | SCSn ≤<br>V <sub>IL</sub> |     | 27  | ns   |

| t <sub>29</sub> | tdis(S)   | SCSn High to MISO Hi-Z   |                           |     | 15  | ns   |

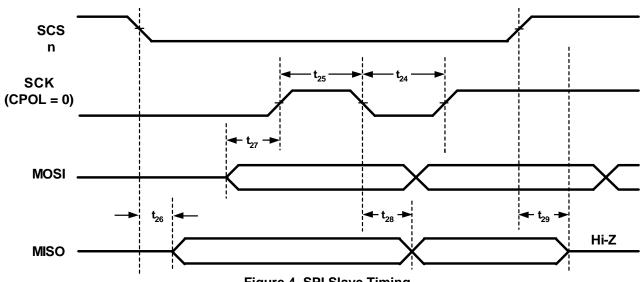

#### SPI Slave Timing (1.8 V V<sub>DDO</sub>)

# SPI Slave Timing (2.5 V or 3.3 V V<sub>DDO</sub>)

|                 | Parameter | Description              | Test<br>Setup             | Min | Max | Unit |

|-----------------|-----------|--------------------------|---------------------------|-----|-----|------|

| t <sub>24</sub> | tw(KL)    | SCK Low pulse width      |                           | 25  |     | ns   |

| t <sub>25</sub> | tw(KH)    | SCK High pulse width     |                           | 25  |     | ns   |

| t <sub>26</sub> | ta(S)     | MISO valid from SCSn Low |                           |     | 20  | ns   |

| t <sub>27</sub> | tsu(D-K)  | MOSI setup to SCK High   |                           | 5   |     | ns   |

| t <sub>28</sub> | ta(K-Q)   | SCK Low to MISO valid    | SCSn ≤<br>V <sub>IL</sub> |     | 20  | ns   |

| t <sub>29</sub> | tdis(S)   | SCSn High to MISO Hi-Z   |                           |     | 15  | ns   |

Figure 4. SPI Slave Timing

# ATW300 Fingerprint Touch Sensor Family Data Sheet

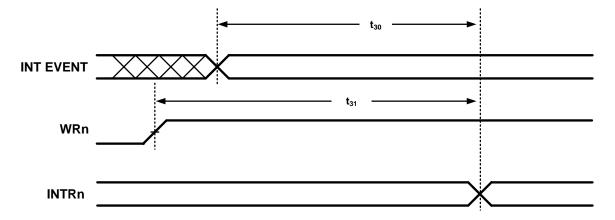

# INTRn Timing

|                 | Parameter | Description                                            | Test<br>Setup | Min | Max | Unit |

|-----------------|-----------|--------------------------------------------------------|---------------|-----|-----|------|

| t <sub>30</sub> | td(E-I)   | Interrupt Event or INT Register status to INTRn valid. |               |     | 60  | ns   |

| t <sub>31</sub> | td(W-I)   | td(W-I) Writing INT Register to INTRn valid.           |               |     | 60  | ns   |

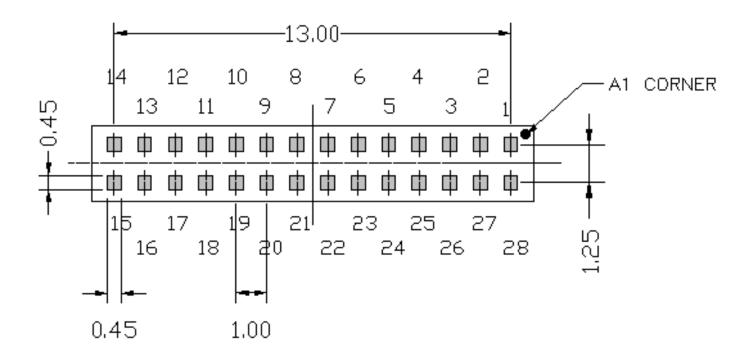

# SENSOR PINOUT DESCRIPTION

| 14                 | 13          | 12     | 11         | 10  | 9   | 8            | 7                | 6                | 5                | 4                | 3                | 2     | 1     |

|--------------------|-------------|--------|------------|-----|-----|--------------|------------------|------------------|------------------|------------------|------------------|-------|-------|

| D6/<br>MOSI        | D7/<br>MISO | TCLKIN | A0/<br>SCK | RDn | WRn | CSn/<br>SCSn | V <sub>ssc</sub> | $v_{\rm ssc}$    | $V_{\text{DDC}}$ | $V_{DDO}$        | V <sub>sso</sub> | SHGND | SHGND |

| Top View           |             |        |            |     |     |              |                  |                  |                  |                  |                  |       |       |

| D5/<br>SCK_<br>INV | D4          | D3     | D2         | D1  | D0  | INTRn        | V <sub>ssc</sub> | V <sub>ssc</sub> | V <sub>DDC</sub> | V <sub>DDO</sub> | V <sub>sso</sub> | SHGND | SHGND |

| 15                 | 16          | 17     | 18         | 19  | 20  | 21           | 22               | 23               | 24               | 25               | 26               | 27    | 28    |

# **Sensor Pinout Table**

| Pin#                  | Name             |

|-----------------------|------------------|

| 1                     | SHGND            |

| 2                     | SHGND            |

| 2<br>3<br>4<br>5<br>6 | V <sub>SSO</sub> |

| 4                     | VODO             |

| 5                     | V <sub>DDC</sub> |

| 6                     | V <sub>SSC</sub> |

| 7                     | V <sub>SSC</sub> |

| 8                     | CSn / SCSn       |

| 9                     | WRn              |

| 10                    | RDn              |

| 11                    | A0 / SCK         |

| 12                    | TCLKIN           |

| 13                    | D7 / MISO        |

| 14                    | D6 / MOSI        |

| 15                    | D5 / SCK_INV     |

| 16                    | D4               |

| 17                    | D3               |

| 18                    | D2<br>D1         |

| 19                    | D1               |

| 20                    | D0               |

| 21                    | INTRn            |

| 22                    | V <sub>SSC</sub> |

| 23                    | V <sub>SSC</sub> |

| 24                    | V <sub>DDC</sub> |

| 25                    | V <sub>DDO</sub> |

| 26                    | V <sub>SSO</sub> |

| 27                    | SHGND            |

| 28                    | SHGND            |

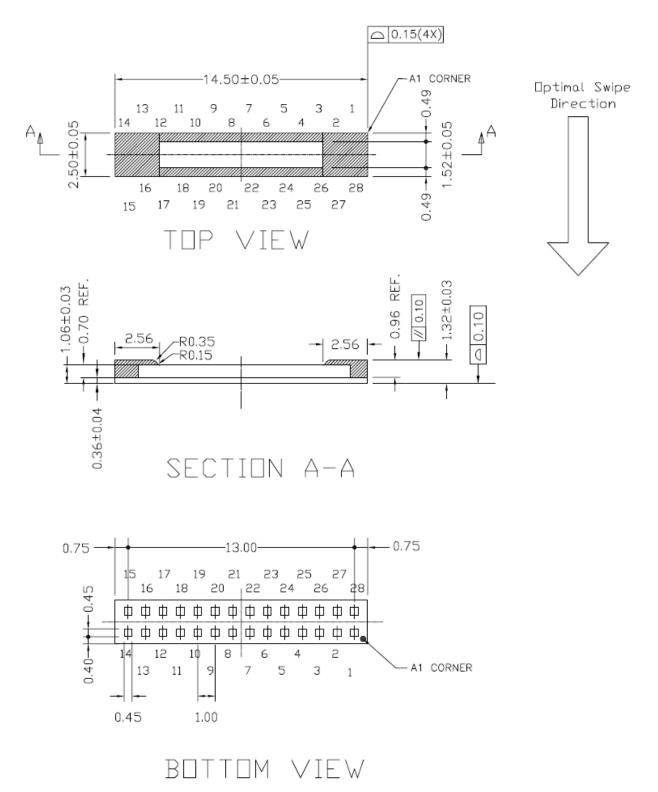

All measurements in millimeters.

850-0003-001 Rev. E December 2007 Atrua Technologies Confidential & Proprietary

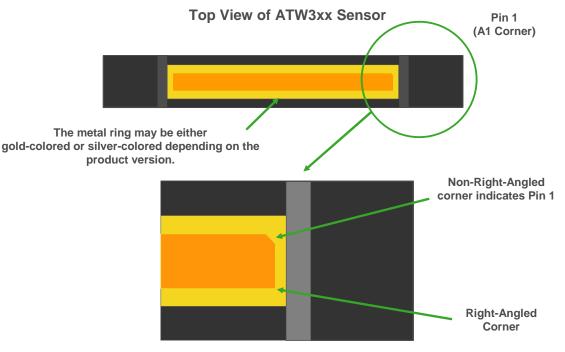

# TOP VIEW PIN 1 MARK

ATW3xx sensors have a microscopic pin 1 indicator on the top surface of the package to mark the orientation of pin 1. Please refer to the diagram below. The pin 1 orientation is marked by a single non-right-angled corner of the sensing region. The other three corners of the sensing region have right-angled corners. The pin 1 indicator allows the orientation of the sensor to be determined by microscope inspection and/or through automated optical inspection of the top surface of the sensor.

**Enlarged View of Circled Region**

This marking is a recent addition to the ATW3xx. For information on whether the particular sensors that you have include this marking or not, please contact your local sales person.

# RECOMMENDED LAND PATTERN

Recommended land pattern for the ATW3xx LGA. All dimensions are in millimeters.

Please note that the recommended land pattern pad size is the same as the LGA pad size. No over or under sizing of pads is recommended.

## SENSOR HANDLING GUIDELINES

This information is provided for reference only. Refer to the Manufacturing Guidelines document (631-0002-002) for the latest and most complete guidelines and for additional details on sensor handling during manufacturing operations such as SMT and assembly.

- 1) Do not allow the sensor's exposed die surface to come in contact with any hard or metallic objects.

- 2) If the sensors need to be manipulated by hand, operators should use anti-static finger cots and either a static dissipative rubber tipped vacuum wand (or pen) or static dissipative (conductive filament) plastic tipped tweezers. When using vacuum wands (or pens), ensure that the tip of the metal capillary does not extend beyond the rubber suction cup. When using tweezers, ensure the sensor die surface is not allowed to come in contact with the tweezers' tips. Both tweezers tips and rubber cups should be placed on a regular replacement schedule to prevent wear-out damage.

- 3) Do not stack sensor boards directly on top of each other. Use anti-static foam spacers to separate boards if stacking is absolutely necessary.

- 4) If protective tape is used on the sensor surface, it should be electrically conductive/static dissipative and not leave adhesive residue, such as a Kapton film tape with silicone adhesive.

- 5) When handling sensors and sensor sub-assemblies, operators must be properly grounded by one of the following:

- A wrist strap connected to ground

- A minimum of one heel ground with both feet on a static dissipative floor surface.

- 6) When not being processed, sensors and sensor assemblies must be stored in static shielded boxes or antistatic or static dissipative plastic bags.

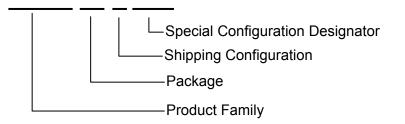

# **PRODUCT CONFIGURATION OPTIONS**

#### $\mathbf{ATW3}XX - YY - Z_1 Z_2 Z_3 Z_4$

#### Where:

ATW3XX indicates the ATRUA Wings Product Family and Surface Color:

ATW310 – Gold-Colored Sensor Surface Border

ATW320 – Silver-Colored Sensor Surface Border

YY indicates PACKAGE:

LA – Land Grid Array (LGA) package

$Z_1$  indicates the SHIPPING CONFIGURATION :

- 0 Standard Trays maximum of 240 units per tray

- 1 Standard Tape & Reel<sup>1</sup> maximum of 3500 units per reel

- Z<sub>2</sub>Z<sub>3</sub>Z<sub>4</sub> is a designator for other SPECIAL CONFIGURATIONS:

000 – Standard Configuration

#### Example:

ATW310-LA-1000 designates an ATW300 family sensor with gold-color sensor surface, LGA package, shipped in Tape & Reel configuration.

Note 1: Please refer to Atrua's LGA Tape and Reel Specification for further detail.

### **IMPORTANT NOTICE**

© 2001-2007 by Atrua Technologies. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Atrua.

This document describes a device currently under development by Atrua, and the information in this document is subject to change without notice. Atrua shall not be responsible for any errors that may appear in this document and makes no commitment to update or keep current the information contained in this document. Atrua advises its customers to obtain the latest version of the device specification to verify, before placing orders, that the information being relied upon by the customer is current.

Devices sold by Atrua are covered by warranty and patent indemnification provisions appearing in Atrua Terms and Conditions of Sale only. Atrua makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Atrua makes no warranty of merchantability or fitness for any purpose.

Atrua's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Atrua prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustain life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Atrua Technologies 1696 Dell Avenue Campbell, CA 95008 USA

Telephone: (408) 370-8000 Fax: (408) 370-8010 Email: sales@atrua.com

www.atrua.com