# SN65LVPE502A/ SN65LVPE502B Application Note

## **Abstract**

The SN65LVPE502A redriver and SN65LVPE502B redriver are dual channel, single lane USB 3.0 redrivers and signal conditioners supporting data rates of 5.0Gbps. All errata for the previous part, SN65LVPE502CP, are fixed in these devices. This application note provides information on implementation of the SN65LVPE502A/SN65LVPE502B devices based on changes from the SN65LVPE502CP device.

## **Table of Contents**

| SN65LVPE502A/ SN65LVPE502B                         | 1 |

|----------------------------------------------------|---|

| APPLICATION NOTE                                   |   |

| APPLICATION NOTE                                   | 1 |

| ABSTRACT                                           | 1 |

| INTRODUCTION                                       | 2 |

| TERMINAL DEFINITION CHANGES                        | 2 |

| ERRATA FIXES                                       | 5 |

| FALSE DETECT                                       | 5 |

| TERMINATION REMAINS ENABLED                        | 5 |

| Figures                                            |   |

| Figure 1 SN65LVPE502A/ SN65LVPE502B Pin-Out        | 2 |

| Figure 2 System Connection SN65LVPE502A            |   |

| Figure 3 System Connection SN65LVPE502B            |   |

| Figure 4 Connection of VBUS Powered Device         |   |

| Figure 5 SN65LVPE502A Successful Disconnect        |   |

| riguie j - jivujev rejuza julicessiui discuiiliect | 0 |

### Introduction

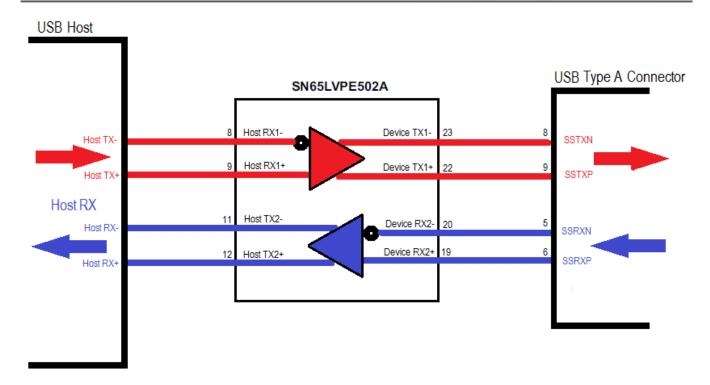

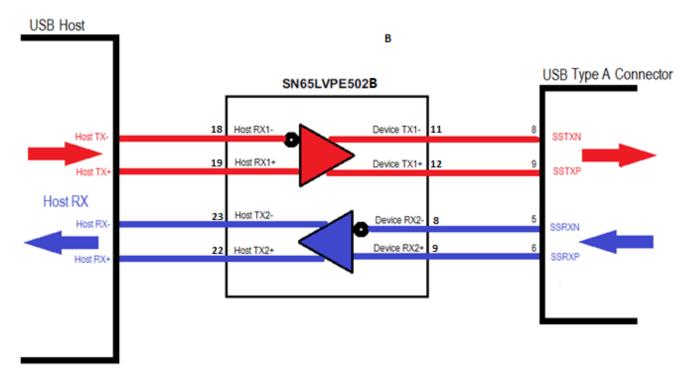

The errata observed on the SN65LVPE502CP device are fixed on the SN65LVPE502A and SN65LVPE502B devices. In addition to the errata fixes, connections are now defined as host side and device side. Connections between the host, redriver, and connector should be verified. The SN65LVPE502A or the SN65LVPE502B should be chosen based on the layout of the board. The errata fixes include the false detect with VBUS powered devices and termination remaining enabled in certain situations.

# **Terminal Definition Changes**

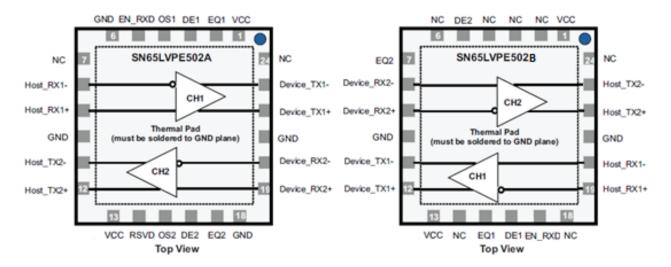

The host side and device side connections are now defined for the SN65LVPE502A and SN65LVPE502B devices. Please reference Table 1 SN65LVPE502A Pin Functions, for a list of pin definition changes.

Figure 1 SN65LVPE502A/ SN65LVPE502B Pin-Out

Table 1 SN65LVPE502A / SN65LVPE502B Pin Functions

|                                  | Pin                    |           |          |                                                                                  |  |  |  |

|----------------------------------|------------------------|-----------|----------|----------------------------------------------------------------------------------|--|--|--|

| SN65LVPE502A<br>Number           | SN65LVPE502B<br>Number | Name      | I/O Type | Description                                                                      |  |  |  |

| HIGH SPEED DIFFERENTIAL I/O PINS |                        |           |          |                                                                                  |  |  |  |

| 8                                | 18                     | Host_RX1- | I, CML   | Non-inverting and inverting CML differential                                     |  |  |  |

| 9                                | 19                     | Host RX1+ | I, CML   | input for CH 1 and CH 2. These pins are tied to an internal voltage bias by dual |  |  |  |

| 20                 | 8               | Device RX2- | I, CML   | termination resistor circuit. All pins labeled                                       |  |  |  |

|--------------------|-----------------|-------------|----------|--------------------------------------------------------------------------------------|--|--|--|

| 20                 |                 | Device_RX2  | I, CIVIL | Host should be connected to the host. Pins labeled Device should be connected to the |  |  |  |

| 19                 | 9               | Device_RX2+ | I, CML   | device or connector.                                                                 |  |  |  |

| 19                 | 9               | Device_RX2+ | i, Civil |                                                                                      |  |  |  |

| 23                 | 11              | Device_TX1- | O, CML   | Non-inverting and inverting CML differential                                         |  |  |  |

|                    |                 |             |          | output for CH 1 and CH 2. These pins are tied to an internal voltage bias by         |  |  |  |

| 22                 | 12              | Device_TX1+ | O, CML   | termination resistors. All pins labeled Host                                         |  |  |  |

|                    |                 |             |          | should be connected to the host. Pins                                                |  |  |  |

| 11                 | 23              | Host_TX2-   | O, CML   | labeled Device should be connected to the                                            |  |  |  |

| 12                 | 22              | Host_TX2+   | O, CML   | device or connector.                                                                 |  |  |  |

| 12                 |                 | HUSL_IAZT   | O, CIVIL | device of confector.                                                                 |  |  |  |

| DEVICE CONTROL PIN |                 |             |          |                                                                                      |  |  |  |

|                    |                 |             | l,       | Sets device operation modes. Internally                                              |  |  |  |

| 5                  | 17              | EN RXD      | LVCMOS   | pulled to VCC                                                                        |  |  |  |

|                    |                 | _           | l,       | RSVD, internally pulled to GND. Can be left                                          |  |  |  |

| 14                 | -               | RSVD        | LVCMOS   | as No-connect.                                                                       |  |  |  |

|                    |                 |             | No-      | Radawa wat into wallu ann antad                                                      |  |  |  |

| 7, 24              | 2, 3, 4, 14, 24 | NC          | connect  | Pads are not internally connected                                                    |  |  |  |

|                    |                 |             |          |                                                                                      |  |  |  |

| EQ CONTROL PINS    |                 |             |          |                                                                                      |  |  |  |

|                    |                 |             | Į,       | Selects de-emphasis settings for CH 1 and                                            |  |  |  |

| 3, 16              | 16, 5           | DE1, DE2    | LVCMOS   | CH 2. Internally tied to Vcc/2                                                       |  |  |  |

|                    |                 |             | l,       | Selects equalization settings for CH 1 and                                           |  |  |  |

| 2, 17              | 15, 7           | EQ1, EQ2    | LVCMOS   | CH 2. Internally tied to Vcc/2                                                       |  |  |  |

|                    |                 |             | l,       | Selects output amplitude for CH 1 and CH 2.                                          |  |  |  |

| 4, 15              | -               | OS1, OS2    | LVCMOS   | Internally tied to Vcc/2                                                             |  |  |  |

| 2014/52 2000       |                 |             |          |                                                                                      |  |  |  |

| POWER PINS         | POWER PINS      |             |          |                                                                                      |  |  |  |

| 1, 13              | 1, 13           | VCC         | Power    | Positive supply should be 3.3V ± 10%                                                 |  |  |  |

| 6, 10, 18, 21      | 10, 21          | GND         | Power    | Supply ground                                                                        |  |  |  |

Figure 2 System Connection SN65LVPE502A

Figure 3 System Connection SN65LVPE502B

### **Errata Fixes**

### **False Detect**

Some VBUS powered devices create noise on plug-in and cause the SN65LVPE502CP to falsely detect the device and enable termination early. After termination is enabled, the host begins polling before the device is ready. Polling will timeout and the host will enter compliance mode. This issue is fixed on the SN65LVPE502A device. Figure 2 Connection of VBUS Powered Device below shows a successful connection after a glitch is observed when the VBUS powered device is attached.

Figure 4 Connection of VBUS Powered Device

#### **Termination Remains Enabled**

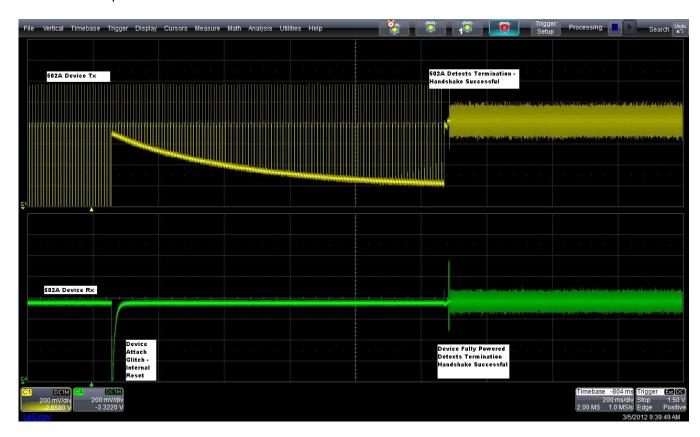

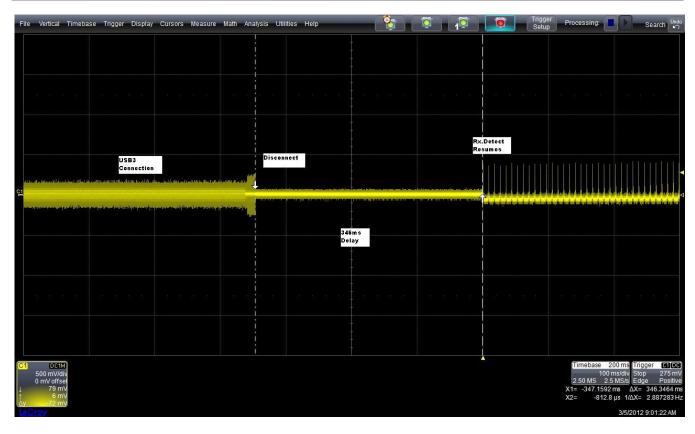

In certain conditions the termination remains enabled after a device is disconnected from the SN65LVPE502CP. This issue is host software driver dependant. If host issues a warm reset within ~300ms of device disconnect the termination will remain enabled. No functional issues are observed, but the power consumption is increased while no devices are connected. This issue is no longer driver dependant and is fixed in the SN65LVPE502A. A successful disconnect may be observed in Figure 3 SN65LVPE502A Successful Disconnect below.

Figure 5 SN65LVPE502A Successful Disconnect

Copyright 2012, Texas Instruments Incorporated