## Recommended SMBus Timing Parameters Date: March 2013

Device ID - DS100RT410, DS100DF410, DS110RT410, DS110DF410, DS125RT410, DS125DF410

## Objective:

The datasheet for the devices do not include SMBus timing parameters, so this document provides the information. The SMBus timing parameters are not tested in production. However, the same design is used on other high speed signal conditioning products and there are no known issues. The table and figure below is the timing parameters for the SMBus interface.

| TABLE: SERIAL MANAGEMENT BUS INTERFACE AC TIMING SPECIFICATIONS |                                                                                                    |                             |     |     |     |       |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------|-----|-----|-----|-------|

| Symbol                                                          | Parameter                                                                                          | Condition                   | Min | Тур | Max | Units |

| FSMB                                                            | Bus Operating Frequency                                                                            | ENSMB = VDD (Slave Mode)    | 100 |     | 400 | kHz   |

|                                                                 |                                                                                                    | ENSMB = FLOAT (Master Mode) | 280 | 400 | 520 | kHz   |

| TBUF                                                            | Bus Free Time Between Stop and Start Condition                                                     |                             | 1.3 |     |     | μs    |

| THD:STA                                                         | Hold time after (Repeated) Start<br>Condition. After this period, the<br>first clock is generated. |                             | 0.6 |     |     | μs    |

| TSU:STA                                                         | Repeated Start Condition Setup Time                                                                |                             | 0.6 |     |     | μs    |

| TSU:STO                                                         | Stop Condition Setup Time                                                                          |                             | 0.6 |     |     | μs    |

| THD:DAT                                                         | Data Hold Time                                                                                     |                             | 0   |     |     | ns    |

| TSU:DAT                                                         | Data Setup Time                                                                                    |                             | 100 |     |     | ns    |

| TLOW                                                            | Clock Low Period                                                                                   |                             | 1.3 |     |     | μs    |

| Thigh                                                           | Clock High Period                                                                                  |                             | 0.6 |     | 50  | μs    |

| tF                                                              | Clock/Data Fall Time                                                                               |                             |     |     | 300 | ns    |

| tr                                                              | Clock/Data Rise Time                                                                               |                             |     |     | 300 | ns    |

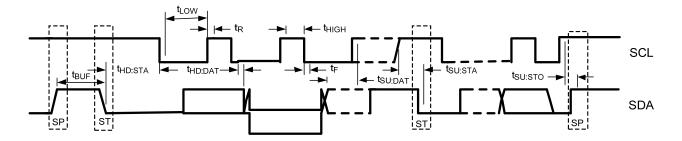

**Figure: SMBUS Timing Parameters**