## 1.lsn't reset negated when the input power source is unstable?

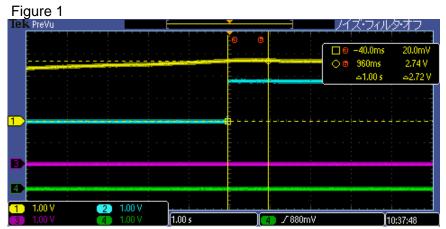

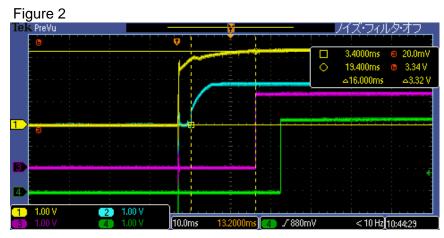

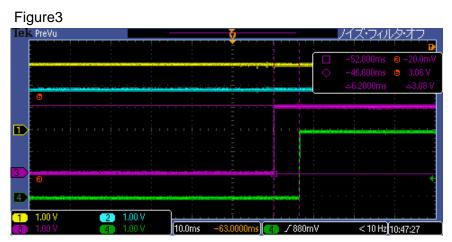

Yellow: VCC1-7 Blue: PWRHOLD Purple: 3.3V\_VAUX Green: PORZ

When raising VCC7 gradually, PWRHOLD is asserted at about 2.74V. Normally, PORX is negate in 20ms, but is not negate in this state

Normal case

PWRHOLD is asserted until 3.3V is outputted stable.

The 3.3V is outputted stable and PORZ is negated after the time of a sequence.

>Is this working correct?

>Is NRESPWRON High in the case of VBAT=2.8V?