PRELIMINARY July 26, 2010

34dB (typ)

19mW (typ)

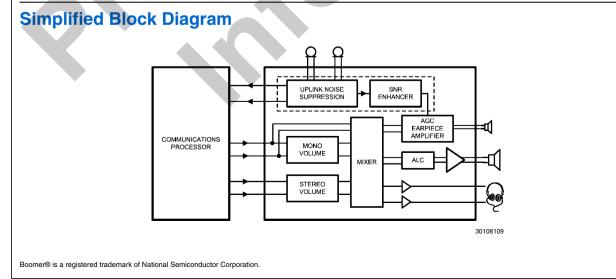

M49155 Uplink Noise Suppression & Downlink SNR

**Enhancement Analog Audio Subsystem**

Boomer<sup>®</sup> Audio Power Amplifier Series

## Uplink Noise Suppression & Downlink SNR Enhancement Analog Audio Subsystem

## **General Description**

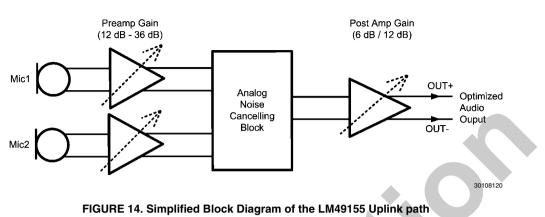

The LM49155 is a fully integrated audio subsystem designed for portable handheld applications such as cellular phones. The LM49155 combines a Noise Suppression microphone amplifier, a 1.35W mono class D amplifier with ALC, class AB earpiece driver with AGC, a high efficiency, stereo, ground referenced headphone amplifier with click pop suppression and I<sup>2</sup>C modes select and volume control.

The LM49155 features analog fully differential input, and differential output microphone amplifier designed to reduce background acoustic noise, while delivering superb speech clarity in voice communication applications. Downlink SNR enhancement utilizes an advanced acoustic AGC technology to adjust output levels.

The LM49155 speaker amplifier features National's unique output limiter that provides both a no-clip feature and speaker protection. The E<sup>2</sup>S class D amplifier features a patented, ultra low EMI PWM architecture that significantly reduces RF emissions while preserving audio quality and efficiency. The headphone drivers feature National's ground referenced architecture that creates a ground-referenced output from a single, low-voltage supply.

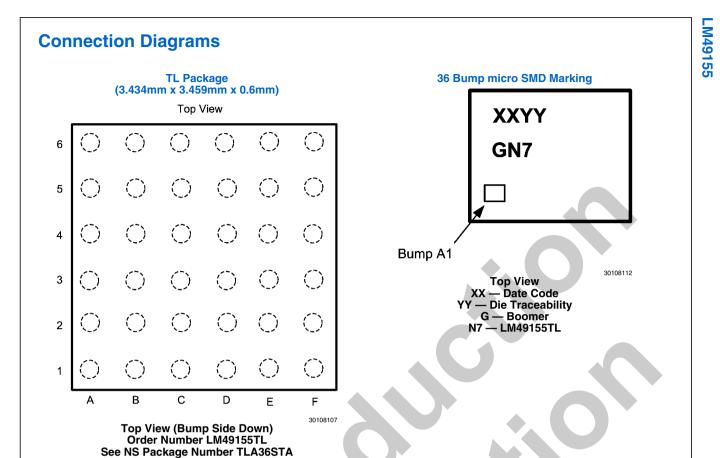

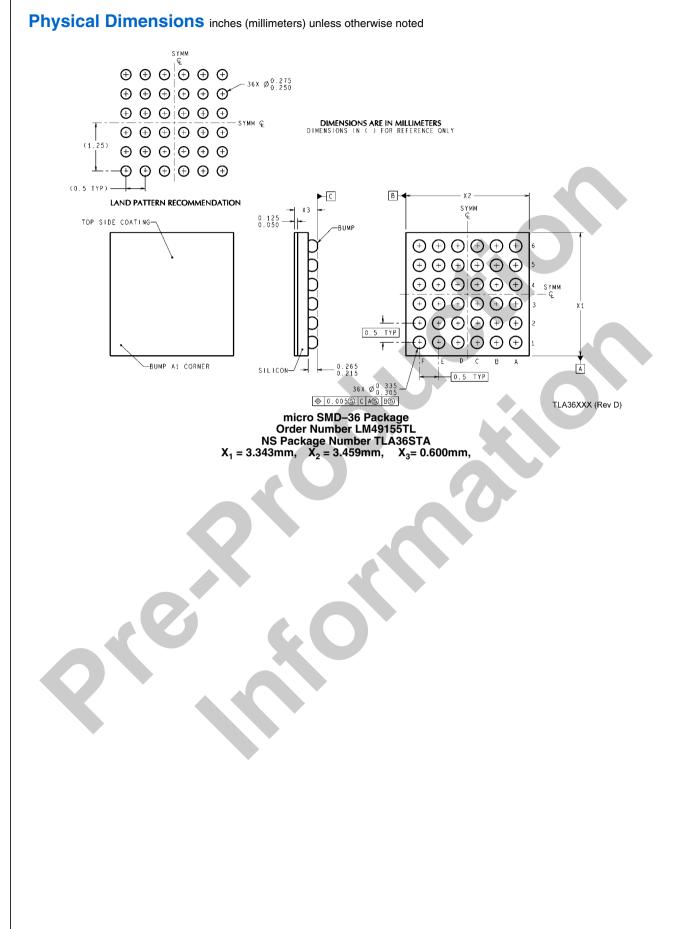

The LM49155 is available in an ultra-small 36-bump micro SMD package.

## **Key Specifications**

- Uplink Far Field Noise Suppression Electrical FFNS<sub>E</sub> at f = 1kHz

- Downlink SNR Enhancement Earpiece Amplifier

Near-Field SNR Enhancement Downlink SNRI<sub>F</sub>

6 to 18dB (typ) 16dB (typ)

- Class D Loudspeaker Amplifier  $R_1 = 15\mu H + 8\Omega + 15\mu H$

| $P_{OUT}$ , THD+N $\leq$ 1%, $V_{DD}$ = 3.6V | 680mW (typ) |

|----------------------------------------------|-------------|

| $P_{OUT}$ , THD+N $\leq$ 1%, $V_{DD}$ = 5.0V | 1.35W (typ) |

| Efficiency                                   | 88% (typ)   |

• Headphone Amplifier  $R_L = 32\Omega$

$P_{OUT}$ , THD+N  $\leq 1\%$ , HPV<sub>DD</sub> = 1.8V

## Features

- Noise cancellation for uplink and downlink without DSPtype artifacts, distortions or delays

- Adapting AGC on ambient noise level & downlink signal strength for earpiece

- Downlink adjustable noise-reducing high pass filter

- E<sup>2</sup>S Class D Amplifier with ALC

- Ground Referenced Headphone Outputs with Advanced Click Pop Suppression

- I<sup>2</sup>C Volume and Mode Control

- Micro-power shutdown

## **Applications**

- Mobile Phones

- Portable Electronic Devices

#### © 2010 National Semiconductor Corporation 301081

www.national.com

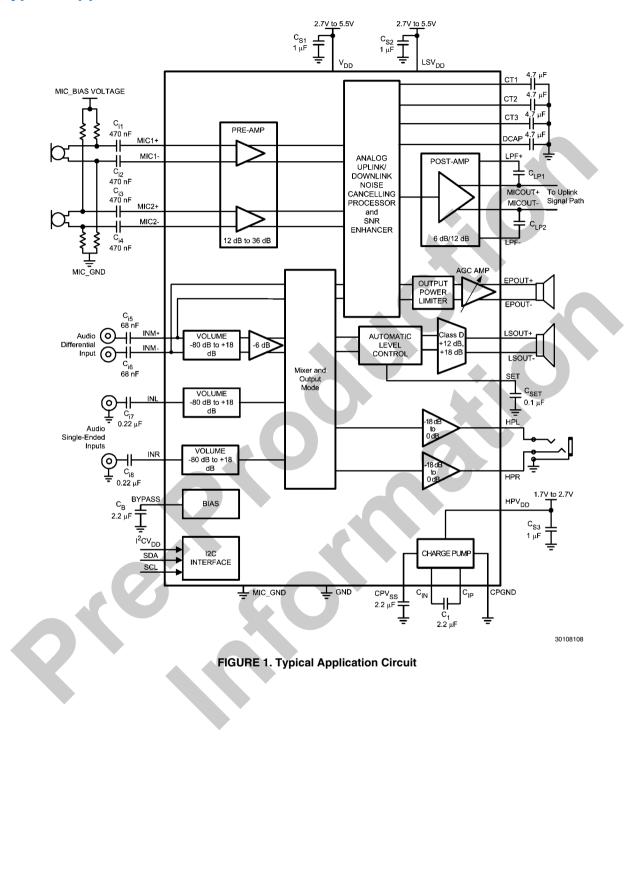

## **Typical Application**

Ordering Information

| Ordering Information |                  |               |                             |           |              |  |  |  |  |

|----------------------|------------------|---------------|-----------------------------|-----------|--------------|--|--|--|--|

| Order Number         | Package          | Package DWG # | Transport Media             | MSL Level | Green Status |  |  |  |  |

| LM49155TL            | 36 Bump microSMD | TLA36STA      | 250 units on tape and reel  | 1         | NOPB         |  |  |  |  |

| LM49155TLX           | 36 Bump microSMD | TLA36STA      | 3000 units on tape and reel | 1         | NOPB         |  |  |  |  |

## TABLE 1. Bump Description

| BUMP | NAME                            | DESCRIPTION                                    |

|------|---------------------------------|------------------------------------------------|

| A1   | SDA                             | I <sup>2</sup> C serial data input             |

| A2   | SCL                             | I <sup>2</sup> C serial clock input            |

| A3   | CT1                             | Control timing capacitor                       |

| A4   | V <sub>DD</sub>                 | Main power supply                              |

| A5   | DCAP                            | Voice signal detection capacitor               |

| A6   | MIC_GND                         | Microphone ground                              |

| B1   | LPF-                            | Low pass filter for negative uplink output     |

| B2   | LPF+                            | Low pass filter for positive uplink output     |

| B3   | CT2                             | Control timing capacitor                       |

| B4   | CT3                             | Control timing capacitor                       |

| B5   | MIC1-                           | Microphone 1 inverting input                   |

| B6   | MIC1+                           | Microphone 1 non-inverting input               |

| C1   | MICOUT-                         | Microphone inverting output                    |

| C2   | MICOUT+                         | Microphone non-inverting output                |

| C3   | INM+                            | Mono channel inverting input                   |

| C4   | INM-                            | Mono channel non-inverting input               |

| C5   | MIC2-                           | Microphone 2 inverting input                   |

| C6   | MIC2+                           | Microphone 2 non-inverting input               |

| D1   | I <sup>2</sup> CV <sub>DD</sub> | I <sup>2</sup> C power supply                  |

| D2   | SET                             | ALC timing set                                 |

| D3   | EPOUT+                          | Earpiece non-inverting output                  |

| D4   | INR                             | Right channel input                            |

| D5   | INL                             | Left channel input                             |

| D6   | CPV <sub>SS</sub>               | Charge pump output                             |

| E1   | LSV <sub>DD</sub>               | Loudspeaker/Earpiece power supply              |

| E2   | BYPASS                          | Mid-Rail bias bypass node                      |

| E3   | EPOUT-                          | Earpiece inverting output                      |

| E4   | C <sub>1P</sub>                 | Charge pump flying capacitor positive terminal |

| E5   | C <sub>1N</sub>                 | Charge pump flying capacitor negative terminal |

| E6   | HPV <sub>DD</sub>               | Headphone power supply                         |

| F1   | LSOUT+                          | Loudspeaker non-inverting output               |

| F2   | LSOUT-                          | Loudspeaker inverting output                   |

| F3   | GND                             | Main Power supply ground                       |

| F4   | CPGND                           | Charge pump ground                             |

| F5   | HPR                             | Right channel headphone output                 |

| F6   | HPL                             | Left channel headphone output                  |

| Absolu<br>2)                                     | te Maximum Ratings (No                                                                                                                                                                                                                                                                       | Junction Temperatur<br>Thermal Resistance<br>θ <sub>JA</sub> (TLA36STA)                                                                                                                         |                                                                                                                                                                                                      |                                                                                                          | 150°C<br>64°C/W                                                                                                                  |                                                                                                                                                          |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| please con                                       | erospace specified devices are requised the National Semiconductor Sals for availability and specifications.                                                                                                                                                                                 |                                                                                                                                                                                                 | Soldering Information<br>See Applications N<br>Level Chip Scale                                                                                                                                      | n<br>Jote AN-111                                                                                         | 2 "Micro SM                                                                                                                      |                                                                                                                                                          |

| Supply Volta                                     | 5                                                                                                                                                                                                                                                                                            | o) (                                                                                                                                                                                            | Operating R                                                                                                                                                                                          | -                                                                                                        |                                                                                                                                  |                                                                                                                                                          |

| V <sub>DD</sub> , I <sup>2</sup> CV <sub>E</sub> | -                                                                                                                                                                                                                                                                                            | 6V                                                                                                                                                                                              |                                                                                                                                                                                                      | atings                                                                                                   |                                                                                                                                  |                                                                                                                                                          |

| Supply Volta<br>HPV <sub>DD</sub> (No            | •                                                                                                                                                                                                                                                                                            | 3V                                                                                                                                                                                              | Temperature Range                                                                                                                                                                                    |                                                                                                          | 100                                                                                                                              |                                                                                                                                                          |

| torage Ter                                       |                                                                                                                                                                                                                                                                                              | to +150°C                                                                                                                                                                                       | $T_{MIN} < T_A < T_{MAX}$                                                                                                                                                                            |                                                                                                          | -40°                                                                                                                             | C ≤ T <sub>A</sub> ≤ +85°C                                                                                                                               |

| nput Voltag                                      | •                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                 | Supply Voltage<br>V <sub>DD</sub> and LSV <sub>DD</sub>                                                                                                                                              |                                                                                                          | 2                                                                                                                                | $2.7V \le to \le 5.5V$                                                                                                                                   |

| ower Dissi                                       |                                                                                                                                                                                                                                                                                              | Ily Limited                                                                                                                                                                                     |                                                                                                                                                                                                      |                                                                                                          | 1                                                                                                                                | $.7V \le to \le 2.7V$                                                                                                                                    |

|                                                  | , Human Body Model                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                 | I <sup>2</sup> CV <sub>DD</sub>                                                                                                                                                                      |                                                                                                          | 1                                                                                                                                | $.7V \le to \le 5.5V$                                                                                                                                    |

| Note 4)                                          | Machina Madal                                                                                                                                                                                                                                                                                | 2000V                                                                                                                                                                                           |                                                                                                                                                                                                      |                                                                                                          |                                                                                                                                  | $I^2CV_{DD} \leq V_{DD}$                                                                                                                                 |

| Note 5)                                          | , Machine Model                                                                                                                                                                                                                                                                              | 150V                                                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                          |                                                                                                                                  |                                                                                                                                                          |

| SD Rating                                        | , Charge Device Model                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                 |                                                                                                                                                                                                      |                                                                                                          |                                                                                                                                  |                                                                                                                                                          |

| lote 6)                                          |                                                                                                                                                                                                                                                                                              | 750V                                                                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                          |                                                                                                                                  |                                                                                                                                                          |

| 8Ω+15µH                                          | ecifications apply for LS and HP VOLU<br>(Loudspeaker), $R_L = 32\Omega$ (Headphone)<br>$V_{P-P}$ , $C_{SET} = 0.1\mu F$ , ALC disabled, f =                                                                                                                                                 | ), R <sub>L</sub> = 32Ω (E                                                                                                                                                                      | arpiece), MIC_PREGAIN                                                                                                                                                                                | I = 20dB, MI<br>s apply for T                                                                            | C_POSTG/                                                                                                                         | AIN = 6dB, MIC<br>Note 8)                                                                                                                                |

| Symbol                                           | Parameter                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                 | Conditions                                                                                                                                                                                           | Typical                                                                                                  | Limit                                                                                                                            | Units                                                                                                                                                    |

| Symbol                                           |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                 |                                                                                                                                                                                                      |                                                                                                          |                                                                                                                                  | (Limits)                                                                                                                                                 |

|                                                  |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                 |                                                                                                                                                                                                      | ( <i>Note 7</i> )                                                                                        | (Note 8)                                                                                                                         |                                                                                                                                                          |

| CHARAC                                           | TERISTICS (V <sub>IN</sub> = 0, No Load)                                                                                                                                                                                                                                                     |                                                                                                                                                                                                 |                                                                                                                                                                                                      | (Note /)                                                                                                 | (Note 8)                                                                                                                         |                                                                                                                                                          |

| CHARAC                                           | TERISTICS (V <sub>IN</sub> = 0, No Load)                                                                                                                                                                                                                                                     | GAMP_SD =                                                                                                                                                                                       |                                                                                                                                                                                                      |                                                                                                          |                                                                                                                                  |                                                                                                                                                          |

| CHARAC                                           | TERISTICS (V <sub>IN</sub> = 0, No Load)                                                                                                                                                                                                                                                     | GAMP_SD =<br>LS Mode, Mo                                                                                                                                                                        |                                                                                                                                                                                                      | ( <i>Note</i> 7)                                                                                         | 4                                                                                                                                | mA (max)                                                                                                                                                 |

| CHARAC                                           | TERISTICS (V <sub>IN</sub> = 0, No Load)                                                                                                                                                                                                                                                     |                                                                                                                                                                                                 | no mode 1                                                                                                                                                                                            |                                                                                                          |                                                                                                                                  | mA (max)<br>mA (max)                                                                                                                                     |

| CHARAC                                           | TERISTICS (V <sub>IN</sub> = 0, No Load)                                                                                                                                                                                                                                                     | LS Mode, Mo                                                                                                                                                                                     | no mode 1<br>ode 8                                                                                                                                                                                   | 3                                                                                                        | 4                                                                                                                                |                                                                                                                                                          |

| CHARAC                                           | TERISTICS (V <sub>IN</sub> = 0, No Load)                                                                                                                                                                                                                                                     | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo                                                                                                                                       | no mode 1<br>ode 8<br>rough mode<br>de 5                                                                                                                                                             | 3                                                                                                        | 4                                                                                                                                | mA (max)                                                                                                                                                 |

|                                                  | Quiescent Power Supply Current                                                                                                                                                                                                                                                               | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>LS + HP, Moo                                                                                                                       | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10                                                                                                                                                    | 3<br>1.3<br>0.6                                                                                          | 4<br>1.6<br>0.8                                                                                                                  | mA (max)<br>mA (max)                                                                                                                                     |

|                                                  |                                                                                                                                                                                                                                                                                              | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Mod<br>GAMP_SD =                                                                                                                          | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0                                                                                                                                               | 3<br>1.3<br>0.6<br>3.1                                                                                   | 4<br>1.6<br>0.8<br>4<br>4.3                                                                                                      | mA (max)<br>mA (max)<br>mA (max)                                                                                                                         |

|                                                  | Quiescent Power Supply Current                                                                                                                                                                                                                                                               | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo                                                                                           | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>ono mode 1                                                                                                                                 | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7                                                                     | 4<br>1.6<br>0.8<br>4<br>4.3<br>5                                                                                                 | mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)                                                                                                 |

|                                                  | Quiescent Power Supply Current                                                                                                                                                                                                                                                               | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo                                                                            | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>ono mode 1<br>ode 8                                                                                                                        | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7                                                              | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1                                                                                          | mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)                                                                                     |

|                                                  | Quiescent Power Supply Current                                                                                                                                                                                                                                                               | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN                                                                             | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>ono mode 1<br>ode 8<br>IR Enhancer Off                                                                                                     | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8                                                       | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3                                                                                   | mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)                                                                         |

|                                                  | Quiescent Power Supply Current                                                                                                                                                                                                                                                               | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN<br>EP Mode, SN                                                              | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>0<br>ono mode 1<br>ode 8<br>IR Enhancer Off<br>IR Enhancer On                                                                              | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8<br>3.8                                                | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3<br>4.5                                                                            | mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)                                                             |

|                                                  | Quiescent Power Supply Current<br>(LSV <sub>DD</sub> + V <sub>DD</sub> )                                                                                                                                                                                                                     | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN                                                                             | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>0<br>ono mode 1<br>ode 8<br>IR Enhancer Off<br>IR Enhancer On                                                                              | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8                                                       | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3                                                                                   | mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)                                                                         |

| 2                                                | Quiescent Power Supply Current<br>(LSV <sub>DD</sub> + V <sub>DD</sub> )<br>Quiescent Power Supply Current<br>(HPV <sub>DD</sub> )                                                                                                                                                           | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN<br>EP Mode, SN                                                              | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>0<br>ono mode 1<br>ode 8<br>IR Enhancer Off<br>IR Enhancer On<br>de 5, 10                                                                  | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8<br>3.8                                                | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3<br>4.5                                                                            | mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)                                                             |

| <b>СНАRAС</b><br>2<br>2<br>(НР)                  | Quiescent Power Supply Current<br>(LSV <sub>DD</sub> + V <sub>DD</sub> )<br>Quiescent Power Supply Current<br>(HPV <sub>DD</sub> )<br>Total Shutdown Current                                                                                                                                 | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN<br>EP Mode, SN<br>LS + HP, Moo                                              | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>0<br>ono mode 1<br>ode 8<br>IR Enhancer Off<br>IR Enhancer On<br>de 5, 10                                                                  | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8<br>3.8<br>3.8<br>3.8                                  | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3<br>4.5<br>5<br>5                                                                  | mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)                                                 |

| 2<br>2(HP)                                       | Quiescent Power Supply Current<br>(LSV <sub>DD</sub> + V <sub>DD</sub> )<br>Quiescent Power Supply Current<br>(HPV <sub>DD</sub> )                                                                                                                                                           | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN<br>EP Mode, SN<br>LS + HP, Moo                                              | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>0<br>ono mode 1<br>ode 8<br>IR Enhancer Off<br>IR Enhancer On<br>de 5, 10                                                                  | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8<br>3.8<br>3.8<br>3.8<br>3.8                           | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3<br>4.5<br>5<br>4                                                                  | mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)<br>mA (max)                                     |

| 2<br>2(HP)<br>2 (I2C)                            | Quiescent Power Supply Current<br>(LSV <sub>DD</sub> + V <sub>DD</sub> )<br>Quiescent Power Supply Current<br>(HPV <sub>DD</sub> )<br>Total Shutdown Current<br>Quiescent I <sup>2</sup> C Power Supply Current                                                                              | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN<br>EP Mode, SN<br>LS + HP, Moo                                              | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>0<br>ono mode 1<br>ode 8<br>IR Enhancer Off<br>IR Enhancer On<br>de 5, 10                                                                  | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8<br>3.8<br>3.8<br>3.8<br>3<br>0.05                     | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3<br>4.5<br>5<br>4                                                                  | mA (max)<br>mA (max)                         |

| 2<br>2(HP)<br>2 (I2C)                            | Quiescent Power Supply Current<br>(LSV <sub>DD</sub> + V <sub>DD</sub> )<br>Quiescent Power Supply Current<br>(HPV <sub>DD</sub> )<br>Total Shutdown Current<br>Quiescent I <sup>2</sup> C Power Supply Current<br>(I <sup>2</sup> CV <sub>DD</sub> )                                        | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN<br>EP Mode, SN<br>LS + HP, Moo                                              | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>0<br>ono mode 1<br>ode 8<br>IR Enhancer Off<br>IR Enhancer On<br>de 5, 10<br>ode 8                                                         | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8<br>3.8<br>3.8<br>3.8<br>3<br>0.05                     | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3<br>4.5<br>5<br>4                                                                  | mA (max)<br>mA (max)                         |

| 2<br>2(HP)<br>2 (I2C)<br><b>JDSPEAK</b>          | Quiescent Power Supply Current<br>(LSV <sub>DD</sub> + V <sub>DD</sub> )<br>Quiescent Power Supply Current<br>(HPV <sub>DD</sub> )<br>Total Shutdown Current<br>Quiescent I <sup>2</sup> C Power Supply Current<br>(I <sup>2</sup> CV <sub>DD</sub> )<br><b>ER AMPLIFIER (Note 9)</b>        | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Mod<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN<br>EP Mode, SN<br>LS + HP, Mod<br>HP Mode, mo                               | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>0<br>ono mode 1<br>ode 8<br>IR Enhancer Off<br>IR Enhancer On<br>de 5, 10<br>ode 8                                                         | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3.0.05<br>0.05  | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3<br>4.5<br>5<br>4                                                                  | mA (max)<br>mA (max) |

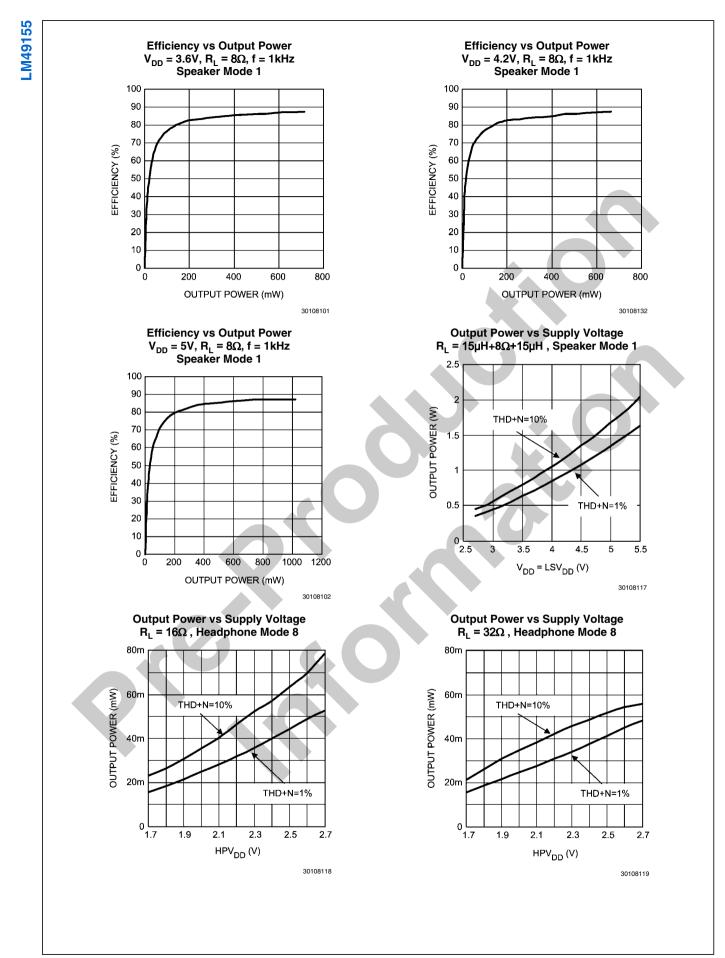

| 2<br>2(HP)<br>2 (I2C)<br>UDSPEAK                 | Quiescent Power Supply Current<br>(LSV <sub>DD</sub> + V <sub>DD</sub> )<br>Quiescent Power Supply Current<br>(HPV <sub>DD</sub> )<br>Total Shutdown Current<br>Quiescent I <sup>2</sup> C Power Supply Current<br>(I <sup>2</sup> CV <sub>DD</sub> )<br>ER AMPLIFIER (Note 9)<br>Efficiency | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN<br>EP Mode, SN<br>LS + HP, Moo<br>HP Mode, mo<br>THD+N = 1%<br>Mono Input S | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>ono mode 1<br>ode 8<br>IR Enhancer Off<br>IR Enhancer On<br>de 5, 10<br>ode 8                                                              | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3 | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3<br>4.5<br>5<br>4                                                                  | mA (max)<br>mA (max)<br>μA (max)             |

| 2)<br>2)(HP)<br>2) (I2C)<br>UDSPEAK              | Quiescent Power Supply Current $(LSV_{DD} + V_{DD})$ Quiescent Power Supply Current $(HPV_{DD})$ Total Shutdown Current      Quiescent I <sup>2</sup> C Power Supply Current $(I^2CV_{DD})$ ER AMPLIFIER (Note 9)      Efficiency      Total Harmonic Distortion + Noise                     | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN<br>EP Mode, SN<br>LS + HP, Moo<br>HP Mode, mo<br>THD+N = 1%<br>Mono Input S | no mode 1<br>ode 8<br>rough mode<br>de 5<br>de 10<br>0<br>0<br>ono mode 1<br>ode 8<br>IR Enhancer Off<br>IR Enhancer On<br>de 5, 10<br>ode 8<br>Signal, P <sub>O</sub> = 250mW<br>Signal, THD+N = 1% | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3 | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3<br>4.5<br>5<br>4                                                                  | mA (max)<br>mA (max)<br>μA (max)             |

| 2<br>2(HP)<br>2 (I2C)                            | Quiescent Power Supply Current<br>(LSV <sub>DD</sub> + V <sub>DD</sub> )<br>Quiescent Power Supply Current<br>(HPV <sub>DD</sub> )<br>Total Shutdown Current<br>Quiescent I <sup>2</sup> C Power Supply Current<br>(I <sup>2</sup> CV <sub>DD</sub> )<br>ER AMPLIFIER (Note 9)<br>Efficiency | LS Mode, Mo<br>HP Mode, mo<br>MIC Pass Th<br>LS + HP, Moo<br>GAMP_SD =<br>LS Mode, Mo<br>HP Mode, mo<br>EP Mode, SN<br>EP Mode, SN<br>LS + HP, Moo<br>HP Mode, mo<br>HP Mode, mo<br>HP Mode, mo | no mode 1<br>pde 8<br>rough mode<br>de 5<br>de 10<br>0<br>on o mode 1<br>pde 8<br>IR Enhancer Off<br>IR Enhancer On<br>de 5, 10<br>pde 8<br>Signal, $P_0 = 250$ mW<br>Signal, THD+N = 1%             | 3<br>1.3<br>0.6<br>3.1<br>3.4<br>3.7<br>1.7<br>0.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3.8<br>3 | 4<br>1.6<br>0.8<br>4<br>4.3<br>5<br>2.1<br>1.3<br>4.5<br>5<br>4<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | mA (max)<br>mA (max)<br>μA (max)<br>μA (max) |

|                   |                                   |                                                                                                | LM4                          |                            |                            |  |  |

|-------------------|-----------------------------------|------------------------------------------------------------------------------------------------|------------------------------|----------------------------|----------------------------|--|--|

| Symbol            | Parameter                         | Conditions                                                                                     | Typical<br>( <i>Note 7</i> ) | Limit<br>( <i>Note 8</i> ) | Units<br>(Limits)          |  |  |

|                   |                                   | f = 217Hz, V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub> , All inpu                               | its terminat                 | ed to AC GN                | ID, C <sub>B</sub> = 2.2µl |  |  |

|                   |                                   | Output Referred                                                                                |                              |                            |                            |  |  |

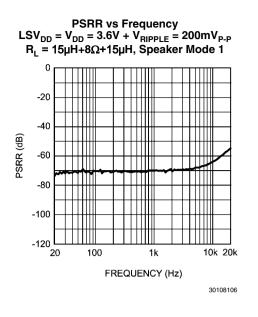

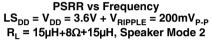

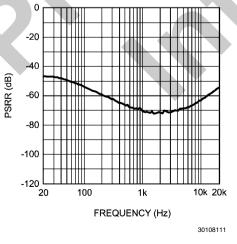

| PSRR              | Power Supply Rejection Ratio      | LS Mode 1, Mono Input                                                                          | 72                           |                            | dB                         |  |  |

|                   |                                   | LS Mode 2, Stereo Input                                                                        | 60                           |                            | dB                         |  |  |

|                   |                                   | LS Mode 3, Mono + Stereo Input                                                                 | 60                           |                            | dB                         |  |  |

| SNR               | Signal To Noise Ratio             | $P_{O} = 680 \text{mW}, \text{ A-weighted}$                                                    | 94                           |                            | dB                         |  |  |

|                   |                                   | A-weighted, All inputs terminated to AC                                                        | GND                          |                            |                            |  |  |

|                   |                                   | LS Mode 1, Mono Input                                                                          | 46                           |                            | μV                         |  |  |

| ∈ <sub>OS</sub>   | Output Noise                      | LS Mode 2, Stereo Input                                                                        | 55                           |                            | μV                         |  |  |

|                   |                                   | LS Mode 3, Mono + Stereo Input                                                                 | 60                           |                            | μV                         |  |  |

| CMRR              | Common Mode Rejection Ratio       | V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub> , f <sub>RIPPLE</sub> = 217Hz,<br>Mono Input Signal | 55                           |                            | dB                         |  |  |

|                   |                                   | LS Mode 1, Mono Input                                                                          | 10                           | 40                         | mV (max)                   |  |  |

| V <sub>os</sub>   | Output Offset Voltage             | LS Mode 2, Stereo Input                                                                        | 10                           |                            | mV (max)                   |  |  |

| •OS               | Culput Choct Voltage              | LS Mode 3, Mono + Stereo Input                                                                 | 10                           |                            | mV                         |  |  |

|                   |                                   |                                                                                                |                              |                            | kΩ                         |  |  |

| Z <sub>IN</sub>   | Input Impedance                   | Maximum Gain Setting (MONO input)<br>Minimum Gain Setting (MONO input)                         | 12.5<br>99                   |                            | kΩ                         |  |  |

| HEADPHON          | E AMPLIFIER                       |                                                                                                | 00                           |                            | 1132                       |  |  |

| THD+N             | Total Harmonic Distortion + Noise | Stereo Input Signal, P <sub>O</sub> = 12mW                                                     | 0.01                         |                            | %                          |  |  |

|                   |                                   | Stereo Input Signal, THD+N = 1%                                                                |                              |                            |                            |  |  |

| Po                | Output Power                      | $R_{\rm I} = 16\Omega$                                                                         |                              |                            |                            |  |  |

| 0                 |                                   | $R_L = 32\Omega$                                                                               | 19<br>19                     | 15                         | mW<br>mW (min)             |  |  |

|                   |                                   |                                                                                                |                              |                            | mW (min)                   |  |  |

|                   |                                   | $f = 217Hz$ , $V_{RIPPLE} = 200mV_{P.P}$ , All inputs terminated to AC GND, $C_B = 2.2\mu F$   |                              |                            |                            |  |  |

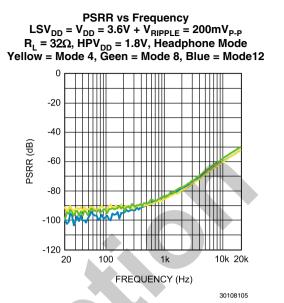

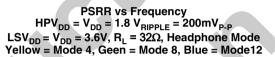

|                   |                                   | Ripple on HPV <sub>DD</sub>                                                                    | 04                           |                            | dD                         |  |  |

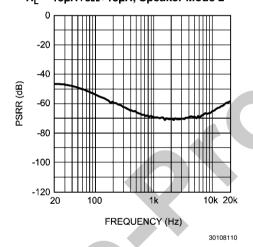

|                   |                                   | HP Mode 4, Mono Input<br>HP Mode 8, Stereo Input                                               | 94<br>90                     |                            | dB<br>dB                   |  |  |

| PSRR              | Power Supply Rejection Ration     | HP Mode 12, Mono + Stereo Input                                                                | 90                           |                            | dB                         |  |  |

| -                 |                                   | Ripple on V <sub>DD</sub>                                                                      |                              |                            |                            |  |  |

|                   |                                   | HP Mode 4, Mono Input                                                                          | 94                           |                            | dB                         |  |  |

|                   |                                   | HP Mode 8, Stereo Input                                                                        | 78                           |                            | dB                         |  |  |

|                   |                                   | HP Mode 12, Mono + Stereo Input                                                                | 78                           |                            | dB                         |  |  |

| SNR               | Signal-to-Noise Ratio             | P <sub>O</sub> = 20mW, A-weighted                                                              | 95                           |                            | dB                         |  |  |

|                   |                                   | A-weighted, All inputs terminated to AC                                                        | GND                          | · · · ·                    |                            |  |  |

|                   |                                   | HP Mode 4, Mono Input                                                                          | 9                            |                            | μV                         |  |  |

| €os               | Output Noise                      | HP Mode 8, Stereo Input                                                                        | 10                           |                            | μV                         |  |  |

|                   |                                   | HP Mode 12, Mono + Stereo Input                                                                | 12                           |                            | μV                         |  |  |

| X <sub>TALK</sub> | Crosstalk                         | $P_0 = 12mW$                                                                                   | 85                           |                            | dB                         |  |  |

|                   |                                   | HP Mode 4, Mono Input HP                                                                       | 1.2                          |                            | mV                         |  |  |

| V <sub>OS</sub>   | Output Offset Voltage             | Mode 8, Stereo Input                                                                           | 1.2                          |                            | mV                         |  |  |

|                   |                                   | HP Mode 12, Mono + Stereo Input                                                                | 1.5                          |                            | mV                         |  |  |

|                   |                                   | HP Mode 8, $C_B = 2.2 \mu F$                                                                   |                              |                            |                            |  |  |

| Τ <sub>WU</sub>   | Turn-On Time                      | Normal turn on time                                                                            | 27                           |                            | ms                         |  |  |

|                   |                                   | Fast turn on time                                                                              | 15                           |                            | ms                         |  |  |

|                      |                                             |                                                    | LM4                          | Units<br>(Limits) |                            |

|----------------------|---------------------------------------------|----------------------------------------------------|------------------------------|-------------------|----------------------------|

| Symbol               | Parameter                                   | Conditions                                         | TypicalLimit(Note 7)(Note 8) |                   |                            |

|                      |                                             | Minimum Gain Setting (MONO input)                  | -80                          |                   | dB<br>dB                   |

|                      |                                             | Maximum Gain Setting (MONO input)                  | 18                           |                   | dB<br>dB                   |

| A <sub>VOL</sub>     | Volume Control                              | Minimum Gain Setting (Stereo input)                | -80                          |                   | dB<br>dB                   |

|                      |                                             | Maximum Gain Setting (Stereo input)                | 18                           |                   | dB<br>dB                   |

|                      | Volume Control Gain Error                   |                                                    | ±0.5                         |                   | dB                         |

|                      |                                             | LS Mode<br>Gain 0<br>Gain 1                        | 12<br>18                     |                   | dB<br>dB                   |

| A <sub>V</sub>       | Gain                                        | HP Mode<br>Gain 0<br>Gain 1<br>Gain 2<br>Gain 3    | 0<br>-1.5<br>-3<br>-6<br>-9  |                   | dB<br>dB<br>dB<br>dB<br>dB |

|                      |                                             | Gain 4<br>Gain 5<br>Gain 6<br>Gain 7               | -12<br>-15<br>-18            |                   | dB<br>dB<br>dB             |

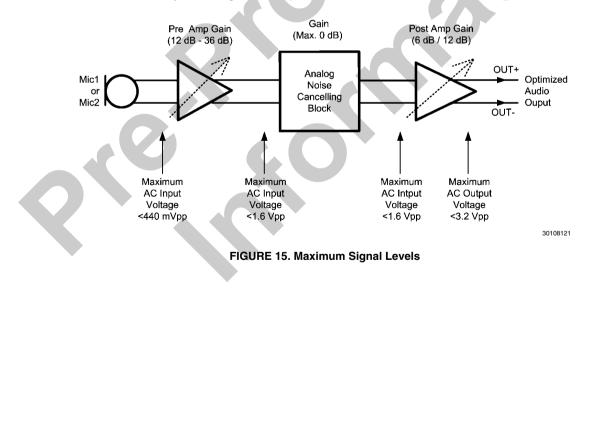

| A <sub>M</sub>       | Microphone Pre Amplifier Gain<br>Range      | Minimum setting<br>Maximum setting                 | 12<br>36                     |                   | dB<br>dB                   |

| A <sub>MR</sub>      | Microphone Pre Amplifier Gain<br>Resolution |                                                    | 2                            | 1.7<br>2.3        | dB (min)<br>dB (max)       |

| A <sub>P</sub>       | Post Amplifier Gain Range                   | Minimum setting<br>Maximum setting                 | 6<br>12                      |                   | dB<br>dB                   |

| A <sub>PR</sub>      | Post Amplifier Gain Resolution              |                                                    | 6                            | 5.5<br>6.5        | dB (min)<br>dB (max)       |

| AUTOMATIC            | LEVEL CONTROL (ALC)                         |                                                    |                              |                   |                            |

| t <sub>A</sub>       | Attack Time                                 | ATTACK_TIME = 00                                   | 0.75                         |                   | ms                         |

| t <sub>R</sub>       | Release Time                                | RELEASE_TIME = 00                                  | 1                            |                   | S                          |

|                      |                                             | LS Mode, THD+N ≤1%, Note 10                        |                              |                   |                            |

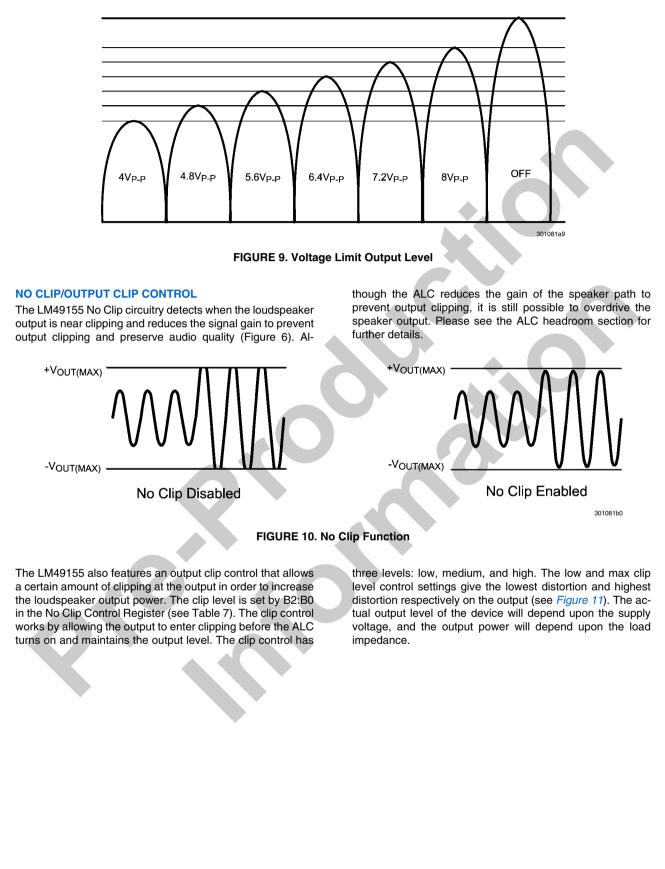

|                      |                                             | VOLTAGE_LEVEL = 001                                | 4                            |                   | V <sub>P-P</sub>           |

| V <sub>LIMIT</sub>   | Output Voltage Limit                        | VOLTAGE_LEVEL = 010                                | 4.8                          |                   | V <sub>P-P</sub>           |

|                      |                                             | VOLTAGE_LEVEL = 011                                | 5.6                          |                   | V <sub>P-P</sub>           |

|                      |                                             | VOLTAGE_LEVEL = 100                                | 6.4                          |                   | V <sub>P-P</sub>           |

| UPLINK SPE           | CIFICATIONS (Mic Pass Through mo            |                                                    | 1                            | II                | F-F                        |

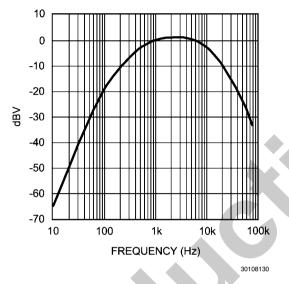

|                      | Far Field Noise Suppression                 | f = 1kHz (See <i>Test Methods</i> )                | 34                           | 26                | dB (min)                   |

| FFNSE <sub>ADC</sub> | (Electrical)                                | f = 300Hz (See <i>Test Methods</i> )               | 42                           |                   | dB (min)                   |

|                      | Signal-to-Noise Ratio Improvement           | f = 1kHz (See <i>Test Methods</i> )                | 26                           | 18                | dB (min)                   |

| SNRI <sub>E</sub>    | (Electrical)                                | f = 300Hz (See <i>Test Methods</i> )               | 33                           |                   | dB (min)                   |

| V <sub>IN</sub>      | Maximum Input Signal                        | THD+N < 1%, Pre Amp<br>Gain = 12dB                 |                              | 440               | mV <sub>P-P</sub> (max     |

| V <sub>OUT</sub>     | Maximum AC Output Voltage                   | Differential Output, f = 1kHz,<br>THD+N < 1%       | 1.2                          | 1.1               | V <sub>RMS</sub> (min)     |

|                      | DC Level at Outputs                         | V <sub>IN</sub> = GND                              | 820                          |                   | mV                         |

| THD+N                | Total Harmonic Distortion + Noise           | Differential Output                                | 0.1                          | 0.2               | % (max)                    |

|                      |                                             | $V_{IN} = 18mV_{P-P}$                              | 63                           |                   | dB                         |

| SNR                  | Signal-to-Noise Ratio                       | V <sub>IN</sub> = 18mV <sub>P-P</sub> , A-Weighted | 65                           |                   | dB                         |

| Symbol              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                        | LM4           | 9155              |                             |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------|-------------------|-----------------------------|--|

|                     | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Conditions                                                                                             | Typical Limit |                   | Units                       |  |

| -                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                        | (Note 7)      | ( <i>Note 8</i> ) | (Limits)                    |  |

| e <sub>N</sub>      | Input Referred Noise level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A-Weighted                                                                                             | 5             |                   | μV <sub>RMS</sub>           |  |

| 7                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                        |               | 103               | kΩ (min)                    |  |

| Z <sub>IN</sub>     | Input Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                        | 142           | 220               | kΩ (max)                    |  |

| Z <sub>OUT</sub>    | Output Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                        | 200           |                   | Ω                           |  |

|                     | Allowable Load Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R <sub>LOAD</sub>                                                                                      |               | 10                | kΩ (min)                    |  |

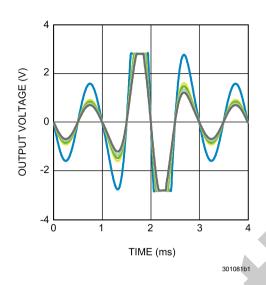

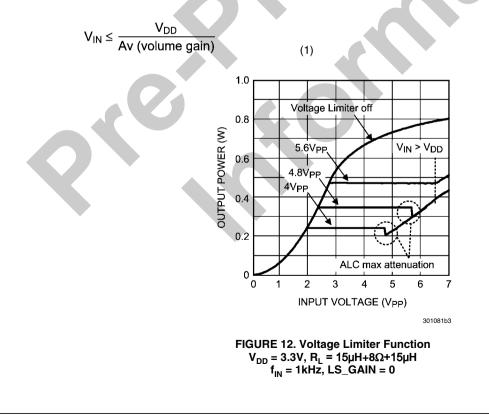

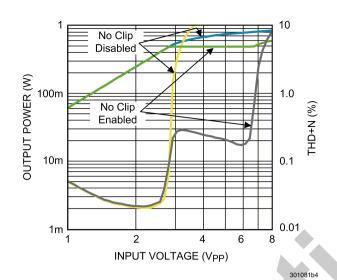

| Z <sub>LOAD</sub>   | Allowable Load Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | C <sub>LOAD</sub>                                                                                      |               | 100               | pF (max)                    |  |