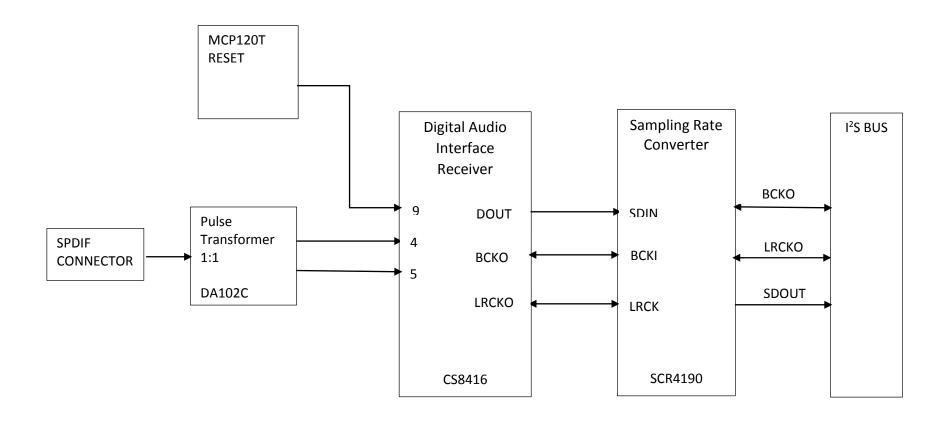

# ARCHITECTURE FOR 192 KHz, 24Bits, S/PDIF TO I2S CONVERTER

#### **TOBU 2 SOCKET**

It is used to connect the S/PDIF input for digital audio

#### **TRANSFORMER**

This is used for isolation to avoid ground loop problem

#### **BUS TRANSCEIVER**

It serves as a Voltage level converter. Used to convert the input voltage from the transformer to TTL since Pin RXIN20 of the Digital Audio Interface chip (DIR9001) accepts only level voltages of 3.3 V or 5 V.

#### DIGITAL AUDIO INTERFACE

It accepts the output of the transceiver and converts it to I<sup>2</sup>S format. It has maximum sample rate of 96 KHz

### SAMPLING RATE CONVERTER

It is used to convert the sample rate from 96 KHz to 192 KHz to match up with the Sampling frequency of the input ADC converter.

## I<sup>2</sup>S BUS

Allows for connection of this module to the Digital Signal Processor.