## Driving the GSPS ADCs in Singleor Dual-Channel Mode for High Bandwidth Applications

Marjorie Plisch

**Applications Engineer, Signal Path Solutions**

November 2012

#### **Outline**

- Overview of the problem

- Solutions evaluation criteria

- Designs tested and key features

- Results summary

- Summary and recommendations

# AN OVERVIEW OF THE PROBLEM

#### **Products covered**

- Which products does the presentation pertain to?

- -ADC12D2000/1800/1600/1000/800/500RF

- -ADC12D1800/1600/1000

- -ADC10D1500/1000

- Actual product evaluated is the ADC12D1600RF

## Dual-channel ADCs may be interleaved to achieve 2x sampling rate

There are a number of options for driving the ADC in interleaved mode, which flexibility also presents a design challenge.

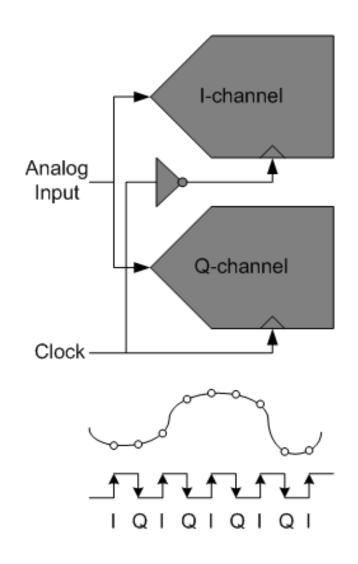

#### What is DES Mode?

- DES is "Dual-Edge Sampling" Mode.

- This describes how the interleaved mode is clocked.

- One channel samples on the rising edge of the clock while the other channel samples on the falling edge of the clock.

- Both channels sample the same analog input.

#### What are the various DES Modes?

|          | Input<br>Driven | Interleaved |

|----------|-----------------|-------------|

| Non-DES  | I, Q            | No          |

| DESI     | I               | Yes         |

| DESQ     | Q               | Yes         |

| DESIQ    | I and Q         | Yes         |

| DESCLKIQ | I and Q         | Yes         |

Note: Inputs are differential, e.g.  $V_{IN}Q+/-$ , but they are represented here as single-ended.

## What is the difference between DESIQ and DESCLKIQ Mode?

#### **DESIQ Mode**

- Pros

- Less insertion loss than DESI, DESQ

- Shorted analog inputs to ensure same signal sampled

- Cons

- More insertion loss than DESCLKIQ Mode

#### **DESCLKIQ Mode**

- Pros

- Minimum insertion loss

- Cons

- Driving the non-shorted inputs requires careful design to ensure the signal fidelity at each point

## Which product has which mode available?

|                        | Non-DES | DESI,<br>DESQ | DESIQ        | DESCLKIQ |

|------------------------|---------|---------------|--------------|----------|

| ADC12D1800/1600/1000RF | ✓       | ✓             | ✓            | ✓        |

| ADC12D800/500RF        | ✓       | $\checkmark$  | $\checkmark$ | ✓        |

| ADC12D1800/1600/1000   | ✓       | ✓             | ✓            |          |

| ADC10D1500/1000        | ✓       | $\checkmark$  | $\checkmark$ |          |

#### **Problem statement**

What is a recommended topology, layout, and type of balun to effectively drive each mode?

# SOLUTIONS EVALUATION CRITERIA

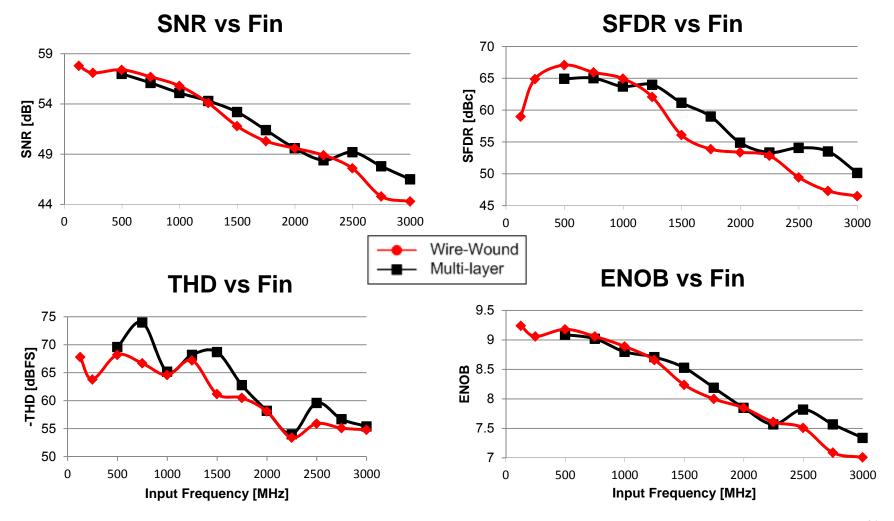

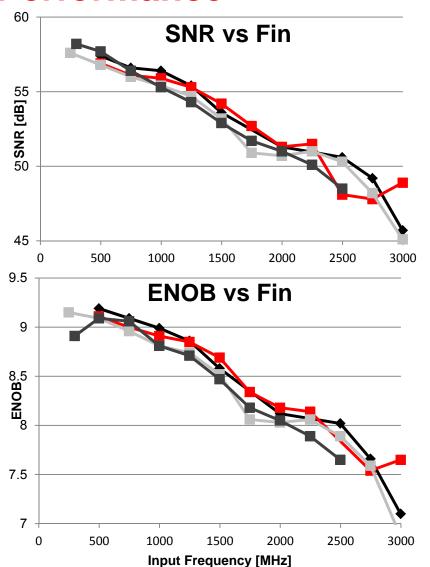

## **Dynamic Performance**

- Signal-to-Noise Ratio (SNR)

- Spurious Free Dynamic Range (SFDR)

- Total Harmonic Distortion (THD)

- Effective Number of Bits (ENOB)

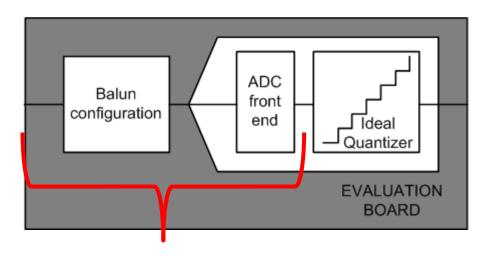

#### **Insertion Loss**

System insertion loss

- The system insertion loss, in dB, includes effects from:

- Evaluation board

- Balun configuration

- ADC front-end

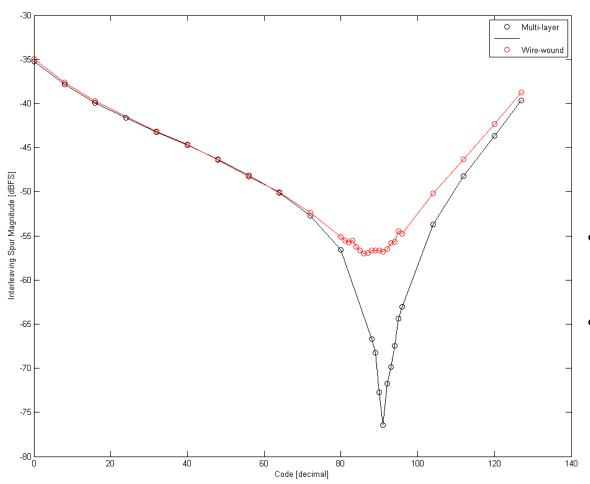

## **Ability to Minimize DES Timing Spur**

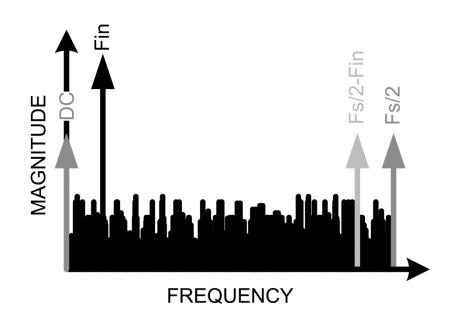

- Gain mismatch and timing skew create an interleaving spur, located at Fs/2 – Fin.

- This spur can be minimized by the Channel Full-Scale Range and DES Timing Adjust features.

- The solution should allow for the magnitude of the interleaving spur to be adjusted below the level of other spurs, so that it is not the SFDR-limiting spur.

Spurious content generated from offset and gain mismatch and timing skew.

## **Multi-mode applications**

- Some applications require the flexibility to configure the ADC into multiple interleaved modes.

- Can the topology accommodate that?

## **DESIGNS TESTED**

## **Design Planning**

#### Things to Consider

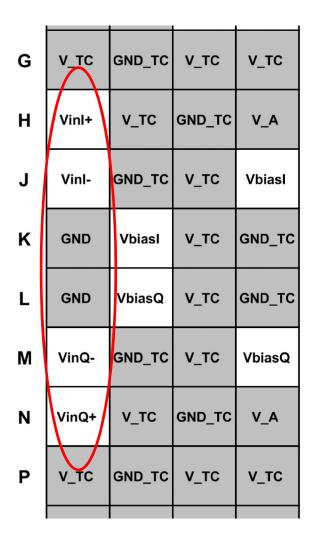

- Topology: I and Q inputs are differential and mirrored

- Input impedance: changes when inputs are driven in parallel

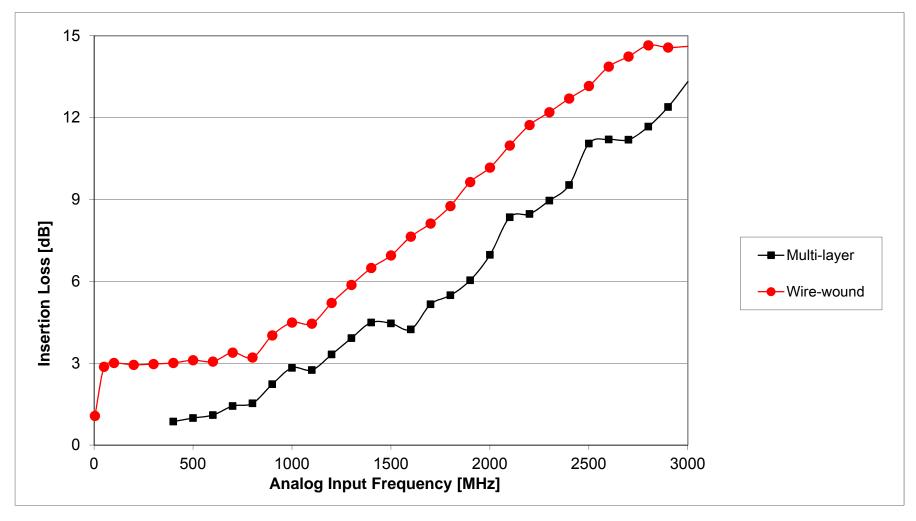

- Balun selection: test a wire-wound and a multi-layer balun

#### **Designs Tested**

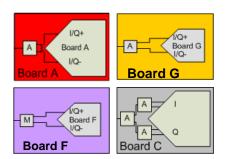

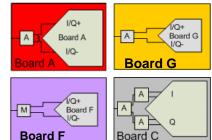

- Board A: Multi-layer balun with power splitter to I- and Q-channel input

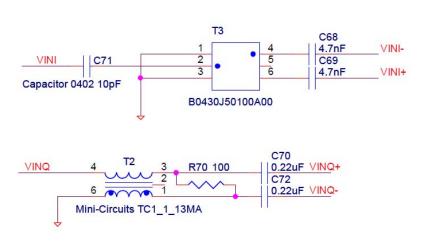

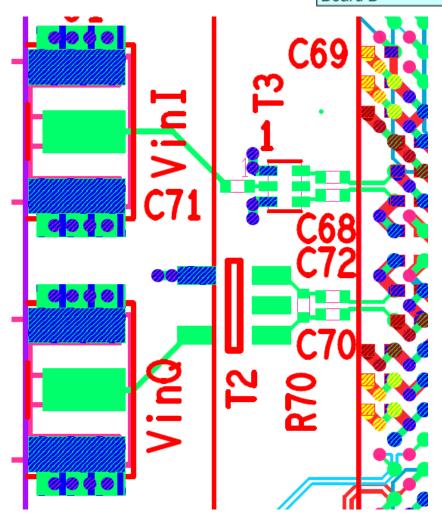

- Board B: Multi-layer balun on I-channel input; wire-wound balun on Q-channel input

- Board C: Cascaded Multi-layer balun to I- and Q-channel input

- Board F: Wire-wound balun to I- and Qchannel input

- Board G: Multi-layer balun to I- and Qchannel input

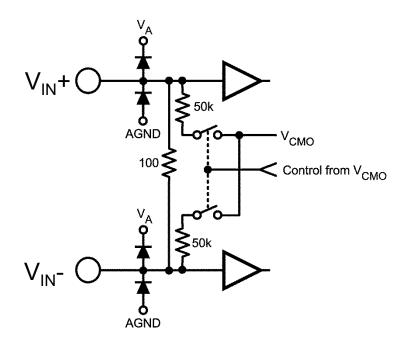

## Topological challenge

- Driving the I- and Q-channels externally at the same time is challenging because I+ and Q+ are not adjacent to one another. (Also, not I- and Q-).

- For a solution which is directly driven, this requires that at least one signal must cross over two of the others. It is challenging to design this layout to be symmetrical.

## **Impedance Considerations**

- When driving one I or Q input, the input impedance is  $100\Omega$  differential:

- Non-DES

- DESI

- DESQ

- When driving both I and Q inputs, the combined input impedance is

50Ω differential:

- DESIQ

- DESCLKIQ

### **Baluns Evaluated**

| Manufacturer    | Anaren                                                             | Anaren                                                             | Mini-Circuits                |

|-----------------|--------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------|

| Model           | B0430J50100                                                        | B0322J5050                                                         | TC1-1-13MA+                  |

| Frequency Range | {400MHz,<br>3000MHz}                                               | {300MHz,<br>2200MHz}                                               | {4.5MHz,<br>3000MHz}         |

| Impedance Ratio | 1:2                                                                | 1:1                                                                | 1:1                          |

| Description     | Multi-layer:<br>coupled strip-line<br>with softboard<br>dielectric | Multi-layer:<br>coupled strip-line<br>with softboard<br>dielectric | Wire-wound with ferrite core |

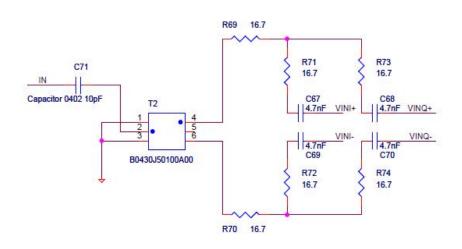

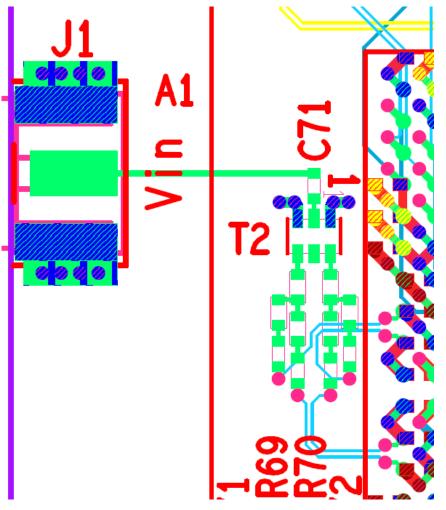

## Board A: Multi-layer balun with power splitter to I- and Q-channel input

- Testing DESIQ and DESCLKIQ Modes

- Single Multi-layer balun

- Resistors are used to split the power and maintain impedance matching

- Routing in multiple layers

## **Board B: Multi-layer balun on I-input;** wire-wound balun on Q-input

- Testing Non-DES, DESI, DESQ Modes

- •One of each Multi-layer and wirewound balun

- All routing accomplished in one layer

- Compact, balanced layout for best dynamic performance

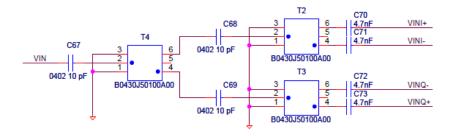

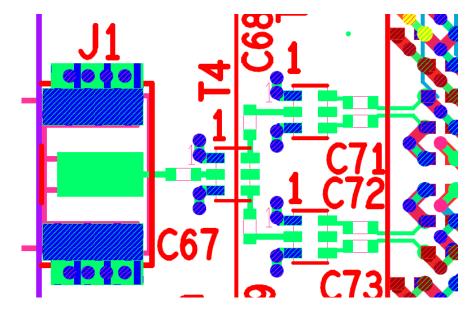

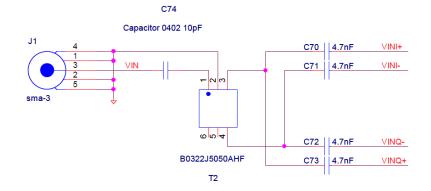

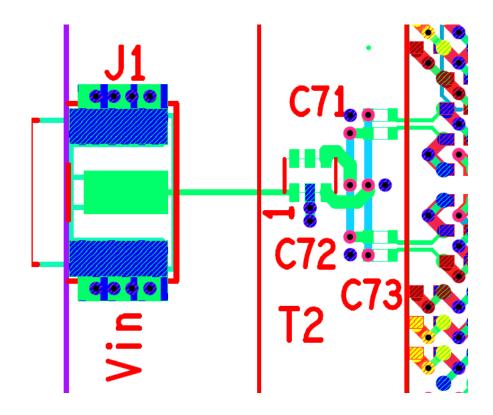

## Board C: Cascaded Multi-layer balun to I- and Q-channel input

- Testing DESIQ, DESCLKIQ Modes

- Adding a selectable input to Pin 2 of T2 and Pin 2 of T3 can enable driving the part in DESI, DESQ, and Non-DES Modes, in addition to DESIQ Mode

- Cascaded Multi-layer balun design achieves impedance matching correct phase at each output, so that all routing may be accomplished in one layer

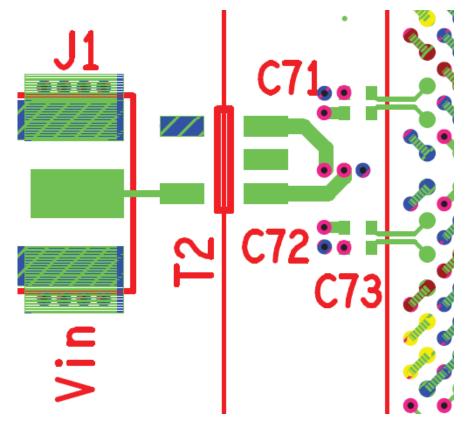

## **Board F: Wire-wound balun to I- and Q-channel input**

- Testing DESIQ and DESCLKIQ Modes

- Single wire-wound balun

- Routing in multiple layers

- Similar to TC1-DESIQ-SBB, external balun board for driving GSPS ADC reference boards

## Board G: Multi-layer balun to I- and Q-channel input

- Testing DESIQ and DESCLKIQ Modes

- Single multi-layer balun

- Routing in multiple layers

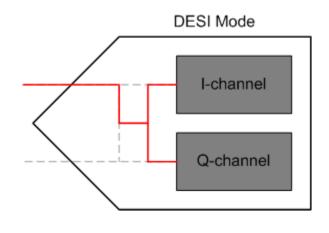

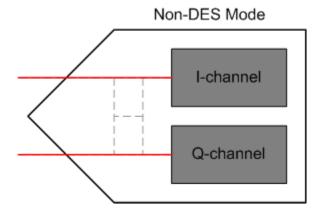

Non-DES Mode

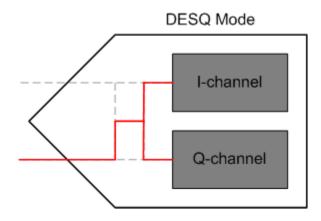

**DESI** and **DESQ** Mode

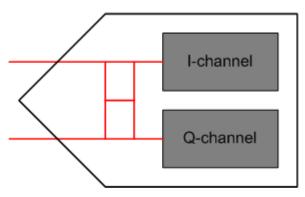

**DESIQ** and **DESCLKIQ** Mode

## **RESULTS SUMMARY**

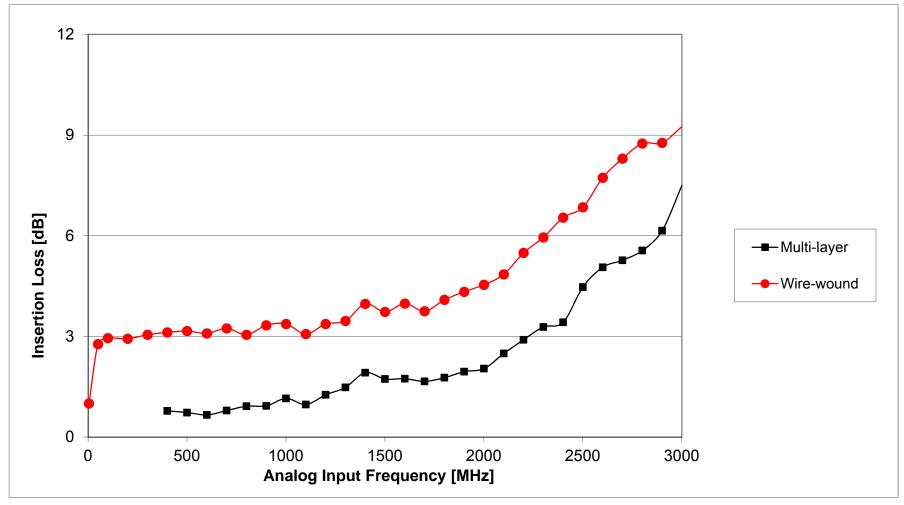

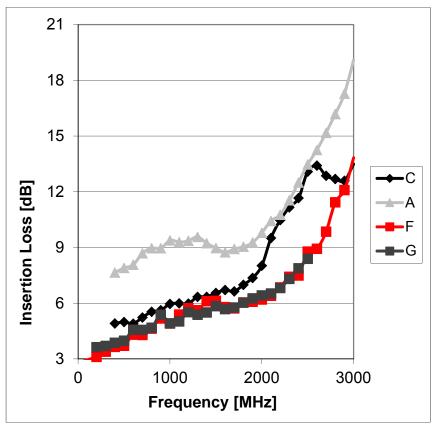

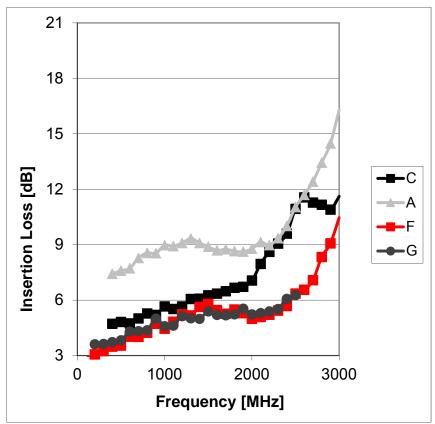

#### **Non-DES Mode Insertion Loss**

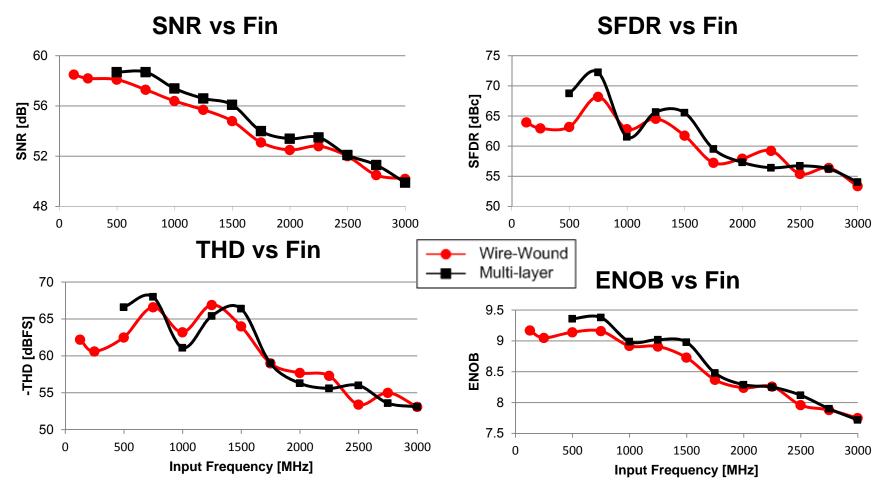

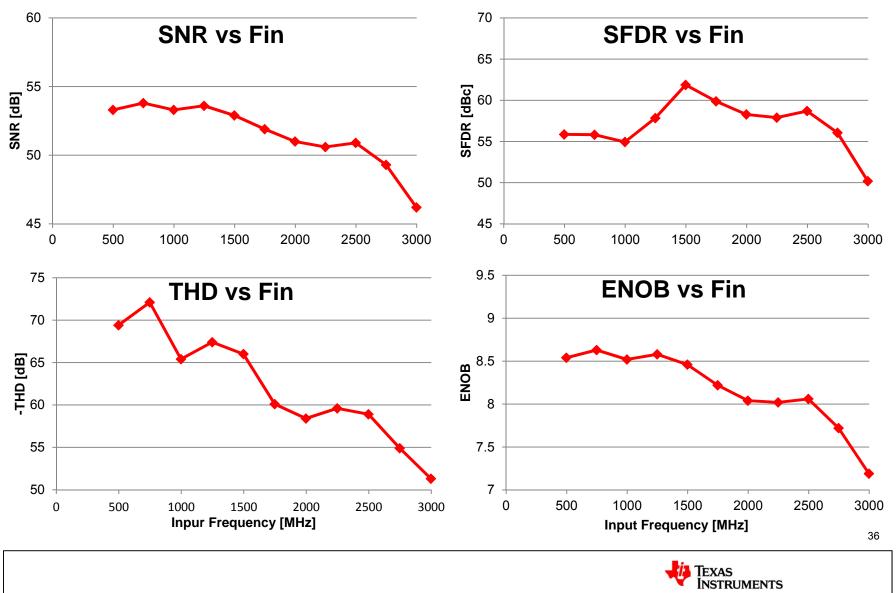

### **Non-DES Mode Dynamic Performance**

### **DESI & DESQ Mode Insertion Loss**

## **DESI & DESQ Mode DES Timing Adjust**

| Balun          | Unadjusted<br>Gain Mismatch |

|----------------|-----------------------------|

| Multi<br>layer | 0.14%                       |

| Wire<br>wound  | 0.33%                       |

- Fin = 1300MHz @-1dBFS

- Achieving a null in the interleaving spur is dependent upon I/Qchannel gain mismatch and timing skew.

### **DESI & DESQ Mode Dynamic Performance**

## **DESIQ and DESCLKIQ Mode Insertion Loss**

#### **DESIQ Mode**

#### **DESCLKIQ Mode**

**Board F**

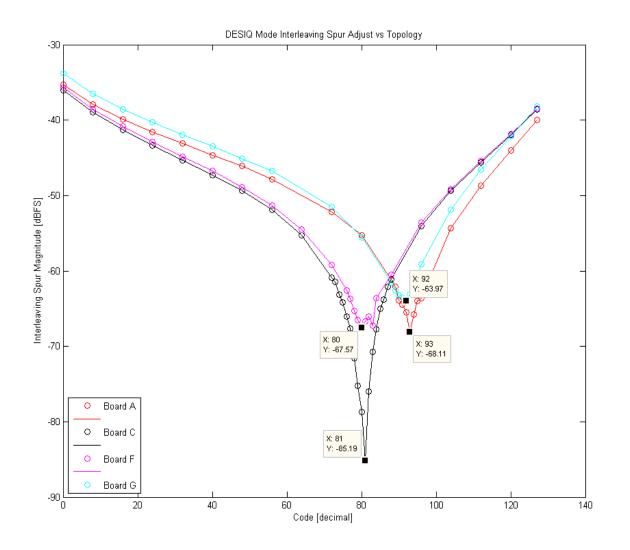

### **DESIQ Mode DES Timing Adjust**

- DESIQ Mode allows for a relative minimum to be achieve relatively easily

- This is due to the internal connection which minimizes gain mismatch

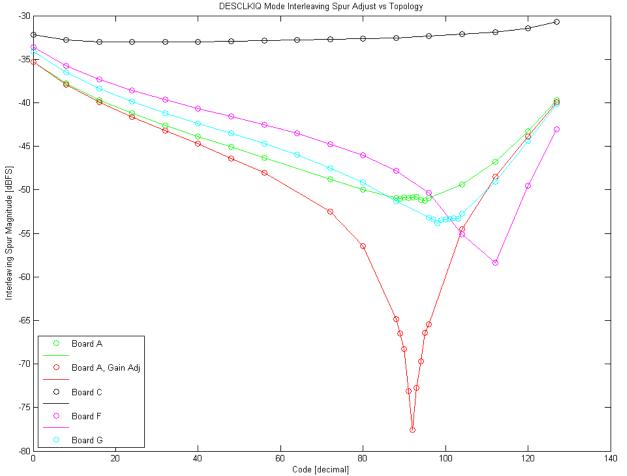

### **DESCLKIQ Mode DES Timing Adjust**

| Board | Gain<br>Adjust | Mis-<br>match |

|-------|----------------|---------------|

| Α     | No             | 5.4%          |

| A     | Yes            | 0.06%         |

Timing skew and gain mismatch may be adjusted independently to achieve best performance

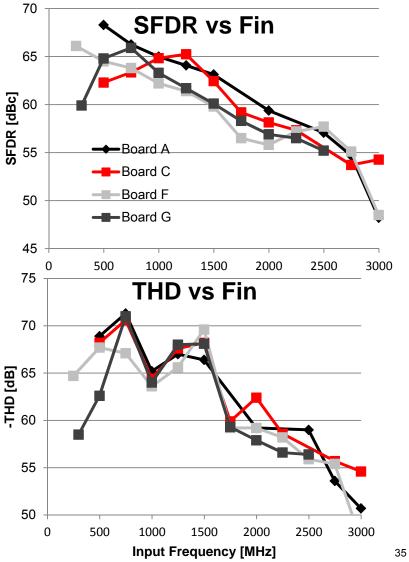

#### **DESIQ Mode Dynamic Performance**

### **DESCLKIQ Mode Dynamic Performance**

# SUMMARY AND RECOMMENDATIONS

## **Non-DES Mode Summary**

| Criteria               | Multi-layer | Wire-wound |

|------------------------|-------------|------------|

| Dynamic Performance    | Excellent   | Average    |

| Insertion Loss         | Excellent   | Average    |

| Frequency Range        | Good        | Excellent  |

| Multi-mode Application | Average     | Average    |

- The multi-layer balun excels in the areas of dynamic performance and insertion loss while the wire-wound balun is excellent for frequency range.

- Both baluns can easily drive both Non-DES Mode and DESI (or DESQ) Mode.

## **DESI and DESQ Mode Summary**

| Criteria                 | Multi-layer | Wire-wound |

|--------------------------|-------------|------------|

| Dynamic Performance      | Good        | Average    |

| Insertion Loss           | Excellent   | Average    |

| Frequency Range          | Good        | Excellent  |

| Multi-mode Application   | Average     | Average    |

| Interleaving Spur Adjust | Excellent   | Poor       |

- The multi-layer balun is a good all-round choice for multiple criteria.

- The wire-wound balun is excellent for frequency range, but poor for adjusting the interleaving spur.

## **DESIQ and DESCLKIQ Mode Summary**

| <b>DESIQ Criteria</b>       | Board A       | Board C   | Board F | Board G   |

|-----------------------------|---------------|-----------|---------|-----------|

| Dynamic Performance         | Average       | Good      | Average | Good      |

| Insertion Loss              | Below Average | Average   | Good    | Excellent |

| Interleaving Spur<br>Adjust | Average       | Good      | Average | Average   |

| Multi-mode Application      | Average       | Excellent | Average | Average   |

| <b>DESCLKIQ Criteria</b>    | Board A       | Board C            | Board F   | Board G   |

|-----------------------------|---------------|--------------------|-----------|-----------|

| Dynamic Performance         | Below Average | Not<br>Recommended | Average   | Average   |

| Insertion Loss              | Below Average | Good               | Excellent | Excellent |

| Interleaving Spur<br>Adjust | Good          | Poor               | Average   | Average   |

| Multi-mode Application      | Average       | Excellent          | Average   | Average   |

#### **Solutions Recommendation**

- Non-DES Mode: The multi-layer balun is the better solution for driving Non-DES Mode. This is true except for applications which require a large input frequency range, especially at low frequencies.

- DESI and DESQ Mode: Similarly, the multi-layer balun is better for driving DESI and DESQ Mode. It is also easier to adjust the DES timing spur using the multi-layer balun.

- DESIQ and DESCLKIQ Mode: In general, it is recommended to use DESIQ Mode instead of DESCLKIQ Mode because the timing spur is so difficult to adjust in DESCLKIQ Mode. The insertion loss is slightly better in DESCLKIQ Mode, but the DESIQ Mode insertion loss is quite comparable.

## **GSPS ADC SOLUTIONS**

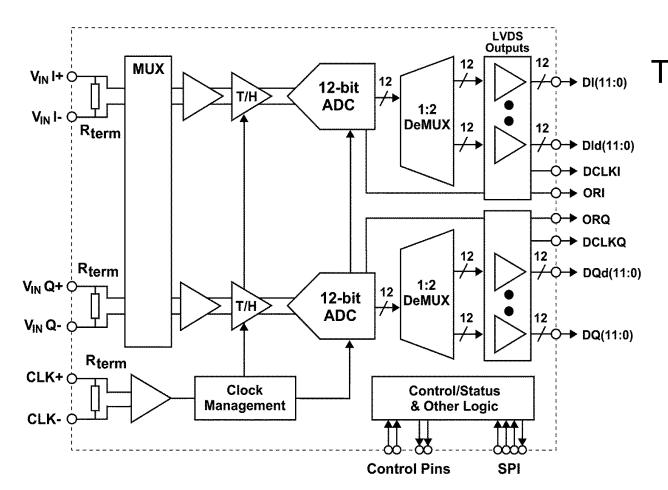

#### ADC12D2000/1800/1600/1000/800/500RF

#### RF Sampling ADCs w/ Industry's Largest Nyquist Zone

#### **Features**

- Configurable:

- 4.0/3.6/3.2/2.0/1.6/1.0 GSPS interleaved

- 2.0/1.8/1.6/1/0.8/0.5 GSPS dual ADC

- Excellent performance beyond 2.7 GHz

- Excellent performance beyond 11<sup>th</sup> Nyquist zone

- Noise floor:

- TBD/-155/-154.6/-154/-152.2/-150.5dBm/Hz

- IMD3@2.7GHz:

- TBD/-64/-70/-69/-71/-69 dBFS

- Power: 4.6/4.4/4.0/3.5/2.5/2.0W

- Autosync function for multi-ADC applications\*

- Pin-compatible w/ ADC12D1x00 & ADC10D1x00

#### **Applications**

- 3G/4G basestation receive & DPD

- Microwave backhaul

- RF-Sampling, wideband SDR

- T&M (scopes, data acquisition, analyzers)

#### **Benefits**

- RF-Sampling capability replaces entire IF- and ZIF-sampling subsystems of mixers, LO synthesizers, filters, amplifiers, and ADCs

- Industry's widest Nyquist zone of 2 GHz enables wideband software-defined radio (SDR) and allows combining multiple channels into one

- Reduction in board area, cost, and complexity

- Pin-compatible family allows range of resolution and speed-grade end-products

EVM: ADC12D2000RFRB, ADC12D1800RFRB, ADC12D1600RFRB, ADC12D800RFRB

\*Not available on ADC12D2000RF

#### Evaluation Boards ADC12D2000/1800/1600/1000RF

#### **FMC Connector allows**

- Full data rate streaming

- Connection to Xilinx dev boards

| NSID         | Eval Board     |

|--------------|----------------|

| ADC12D1000RF | ADC12D1600RFRB |

| ADC12D1600RF | ADC12D1600RFRB |

| ADC12D1800RF | ADC12D1800RFRB |

| ADC12D2000RF | ADC12D2000RFRB |

Optional board for driving DESIQ modes NSID: TC1-DESIQ-SBB

## **THANK YOU!**