## -About RX ER-

About RX\_ER, the datasheet shows following;

- •RX\_ER indicates that an invalid symbol has been detected within a re-ceived packet in 100 Mb/s mode.

- ·Assert high synchronously to X1 when-ever it detects a media error and RXDV is asserted in 100 Mb/s mode.

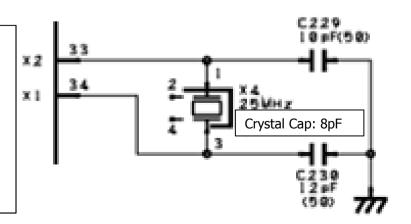

The Left wave form is what our customer measured.

## <Q1>

When RX\_CLK stops oscillating, does RX\_ER assert high?

As my recognition, regardless of RX\_ER high or low, RX\_CLK always oscillates.

Is my recognition correct or not? Please let know us.

## -Clock In (X1) Requirements-

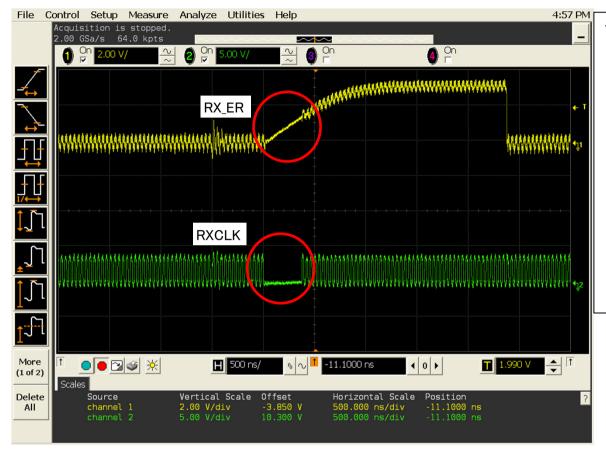

<02>

Our customer is designed like as right value of capacitances, C229=10pF, c230=12pF. CL=  $2 \times \text{Crystal}$  load spec - 7 pF = 16 - 7 = 9pF So, does it have to be used 9pF capacitance for C229, and c230?

<Q3>

AT cut crystal with a minimum drive level of  $100\mu W$  and a maximum of  $500\mu W$ . So, the crystal excitation level is  $10\mu W$  (Max.  $200\mu W$ ), a crystal is specified for a lower drive , should level a current limiting resistor be placed in series between X2 and the crystal?