アナログ/デジタル・コンバータ(ADC)を使用するシステム設計者と話している際に最も多く聞かれるのが、

「16 ビット ADC は 16 ビットの精度があるのですか?」という質問です。

この質問に対する答えは、分解能と精度の違いを根本的に理解することによって得られます。

分解能と精度のコンセプトはまったく異なるにもかかわらず、この 2 つの用語は多くの場合、混同されています。

このブログ・シリーズでは、今回は 2 つのコンセプトの違いを詳細に説明し、次回以降で、ADC の精度を低下させる要因について掘り下げていきます。

ADC の分解能はデジタル出力値を 1 カウント変化させる入力信号値の最小変化と定義できます。理想的な ADC では、この伝達関数は分解能と等しいステップ幅を持つ階段の形をしています。しかし、16 ビット以上の高分解能のシステムでは、伝達関数の応答が理想的な応答から大きく逸脱するようになります。ADC や駆動回路によってもたらされるノイズが ADC の分解能の低下を引き起こすからです。

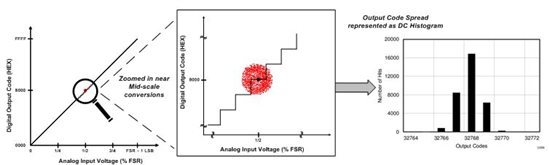

さらに、図 1 に黒いドットで示したように、DC 電圧が最適な ADC の入力に印加され、複数の変換が実行された場合には、デジタル出力は常に同じコード値でなければなりません。実際には、下図の赤いドットのクラスタで示されているように、電圧リファレンスと駆動回路を含む総システム・ノイズに基づき、出力コードが複数のコードにわたって分散します。システム中のノイズが増えれば増えるほど、データ・ポイントのクラスタは広くなります。また、その逆も同じです。図 1 に示したのが、中スケール DC 入力の一例です。ADC 伝達関数上の出力ポイントのこうしたクラスタは、ADC データシートでは DC ヒストグラムとして表されています。

図 1:ADC 伝達曲線における ADC 分解能と実効分解能

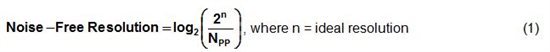

図 1 は興味深い疑問を提起します。もし同じアナログ入力が複数のデジタル出力となるならば、それでも ADC 分解能の定義は正しいと言えるのか?という疑問です。ADC の量子化ノイズしか考慮しない場合、答えはイエスとなります。しかし、シグナルチェーンにおけるすべてのノイズと歪みを考慮に入れる場合、ADC の実効ノイズフリー分解能は、式(1)で示されているように、出力コードスプレッド(NPP)により決定されます。

代表的な ADC データシートで実効ビット数(ENOB)は AC パラメータと信号対ノイズ+歪み比(SINAD)によって間接的に規定されており、式(2)によって計算できます。

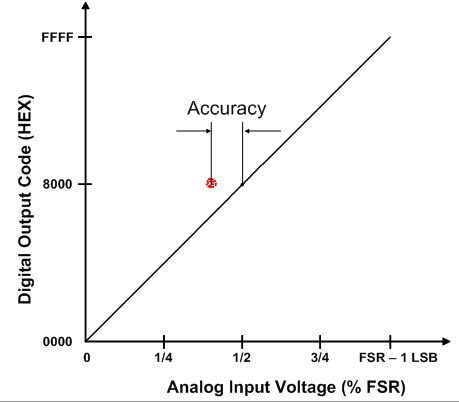

次に、図 1 の出力コードのクラスタ(赤いドット)が理想的な出力コード上の中心位置になく、黒いドットから離れたADC伝達曲線上のどこかに位置する場合(図 2)を検討してみます。この距離がデータ・アクイジション・システムの精度を示します。ADC だけでなく、フロントエンド駆動回路、リファレンス、リファレンス・バッファもすべて総システム精度に対する寄与要因となります。

図 2:ADC 伝達曲線上の精度

特に注意しなければならない重要な点は、ADC の精度と分解能は相互に一致しない可能性のある、2 つの異なるパラメータであるということです。システム設計上の観点からは、精度がシステムの総エラー・バジェットを決定するのに対し、分解能がシステム・ソフトウェア・アルゴリズムの整合性、制御、監視能力を決定します。

次回のブログでは、データ・アクイジション・システムの「トータル」精度を決定する主な要因について解説します。

関連ブログ:

- SAR ADC 性能の考慮事項とその他の SAR ADC 関連ブログ(英語)

- 「高精度のデータ・アクイジションとは?すべてが相対的です」

上記の記事は下記 URL より翻訳転載されました。

*ご質問は E2E 日本語コミュニティにお願い致します。