モーター制御は、30V~100VのディスクリートMOSFETのマーケットにおいて、大規模かつ急速に拡大している市場であり、特にDCモーターを駆動する多数のトポロジに利用されています。この記事では、エンド・アプリケーションでモーターを駆動するために使用されるFETをはじめとした、特定のエンド・アプリケーションで考慮すべき具体的な検討事項を紹介します。ここでは、ブラシ付きモーター、ブラシレス・モーター、ステッピング・モーターを駆動するFETを正しく選択することに重点を置いて説明していきます。厳格なルールはほとんどなく、選択手法は場合によっては無数にありますが、エンド・アプリケーションを考慮した場合にどこから始めるべきか、という点で、ヒントを提供できればと考えています。

最初に説明する、おそらく最も簡単に判断できる選択肢が、必要な降伏電圧です。モーター制御は低周波数になる傾向があり、結果として電源アプリケーションに比べて低リンギングになることから、より低抵抗のFETを得るため、入力電源レールとFETの降伏電圧との間のマージンを(通常はスナバを使用して)少し強気に確保しがちです。しかし、一般にBVDSSと最大入力電圧VINの間のマージンは40%にしておけば問題はありません。(予想されるリンギングの程度と、そのリンギングを外部の受動部品でどれくらい抑制しようとしているかによって、10%の増減幅があります。)

パッケージの種類を選択することが、おそらく最も重要な決断であり、どれを選択するかは、設計の電力密度要件(図1を参照)によって決まります。2A未満では、ほとんどの場合にFETがドライバICに内蔵されますが、そうでない場合もあります。10A未満のステッピング・モーターや低電流ブラシ付きおよびブラシレス・アプリケーションでは、小型のPQFNタイプのデバイス(SON 2mm×2mm、SON 3.3mm×3.3mm)で最大の電力密度が得られます。高電力密度よりも低コストを優先するという場合は、旧型のSOICタイプのパッケージでも役割は果たせるかもしれませんが、必然的にプリント基板(PCB)スペースに占める面積が大きくなります。

図1:異なるモーター電流を駆動するための各種パッケージ・オプション

図1:異なるモーター電流を駆動するための各種パッケージ・オプション

(写真の大きさ比は実際とは異なります)

小型のバッテリ駆動工具や家電製品が占める10A~30Aの領域が、5mm×6mmのQFNを最適に活用できるスイート・スポットです。それより上の領域では、大電流の電動工具や園芸用具に複数のFETが並列に使用されたり、D2PAKなどの大型パッケージのデバイスやTO-220などのスルーホール・パッケージが実装されたりする傾向があります。これらのパッケージはシリコンをより多く格納できるので、抵抗を低減し、電流能力を高め、熱特性を向上させることが可能です。スルーホール・パッケージを大型のヒートシンクに搭載すれば、損失を増やすことができるようになり、より多くの電力を消費できます。

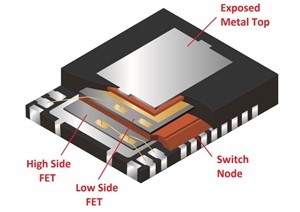

デバイスで消費できる電力量は、FETのパッケージと同じくらい、エンド・アプリケーションの熱環境にも左右されます。表面実装デバイスでは、一般にほとんどの熱がPCBを介して放散されますが、前述したTO-220やTIのDualCool™パワー・ブロック・デバイス(以下の図2)のような他のパッケージをヒートシンクに取り付ければ、基板から熱を取り除いてFETの消費可能な最大電力を引き上げることができます。

最後に確認するのは、目標とすべき抵抗値です。モーターを駆動するためのFETの選択は、ある意味、電源用のFETを選択することよりも簡単ですが、その理由は、低いスイッチング周波数の影響で、導通損失が熱特性の支配的要因となるからです。ただし、PLOSSの推定値を求める際に、スイッチング損失を完全に無視できるわけではありません。それどころか、スイッチング損失が最大でシステムの合計PLOSSの30%を占めるようなワーストケースのシナリオも、過去に例があります。しかし、これらは導通損失に比べれば二次的な損失なので、最初に検討すべきものではありません。極めて大きなストール電流を中心に設計する電動工具では、一般にFETが最大耐熱温度まで発熱する傾向があるため、最初は選択したパッケージで最も低抵抗のデバイスを使用してみるのがよいでしょう。

結論の前に、前述したパワー・ブロック・デバイスをもう一度見てみましょう。40Vの『CSD88584Q 5DC』と60Vの『CSD88599Q 5DC』は、単一の5mm×6mm QFN DualCoolパッケージ(図2を参照)に格納された、2つの垂直統合型ハーフブリッジ・ソリューションです。従来型の5mm×6mmディスクリート・デバイスによるフットプリント面積あたりの抵抗をさらに低減しながら、上面にはヒートシンクに活用できる露出した金属面を備えたこれらのデバイスは、特にスペースに制約のあるアプリケーションで大電流(40A以上)を扱うのに適しています。

より大型のTOパッケージを設計に用いるのは最後の手段にして、その前に、ここで紹介したパワー・ブロックのいずれか1つで試算を行い、PCBフットプリント上の貴重なスペースとヒートシンク・サイズを節減できるかどうか確認することをお勧めします。

参考ブログ:

参考ブログ(英語):

- “Protect your BLDC motor drive with cycle-by-cycle current limit control – part 1”

- “Protect your BLDC motor drive with cycle-by-cycle current limit control – part 2”

- “How to minimize MOSFET conduction loss in battery-powered motor drives”

※DualCoolはTexas Instrumentsの商標です。その他すべての商標はそれぞれの所有者に帰属します。

※上記の記事はこちらのBlog記事(2018年1月24日)より翻訳転載されました。

*ご質問はE2E Support Forumにお願い致します。