Part 1をまだお読みでない方はこちらから。

- ブラシレスDCモーターは素晴らしい!しかも友達作りにも役立つ。

- 実際のハードウェアについては誰も話したがらないが、ここでは言及をする。

- ディスクリート型ゲート・ドライバと統合型ゲート・ドライバには、それぞれ長所と短所がある。

機能やメリットについて一日中話していてもいいのですが、エンジニアが本当に知りたいのは実際の回路です。この記事では、ディスクリート型と統合型のゲート・ドライバ・アーキテクチャを直接比較し、両者の基板レベルでの違いを示します。

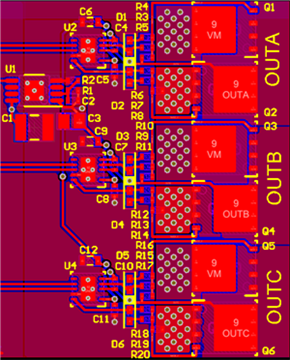

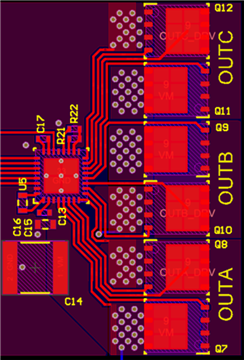

回路図とレイアウトを比較するうえで重要な2つの指標が、部品数とソリューション・サイズです。1つ目の指標である部品数は、回路図が完成すると比較的簡単に確認できます。しかし、ソリューション・サイズを見積もる方法は、はるかに複雑です。ソリューション・サイズとして集積回路部品のサイズが記載されているのをよく見かけますが、これには外部部品や部品間に必要とされる間隔、基板上の配線が考慮されていないため、極めて不正確です。

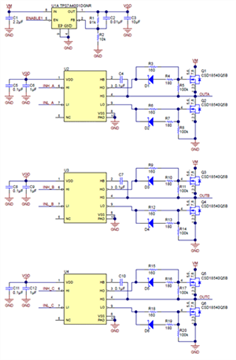

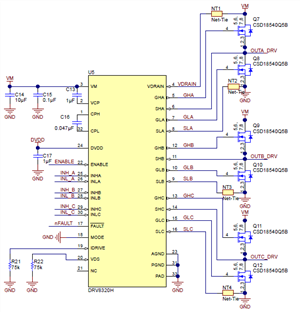

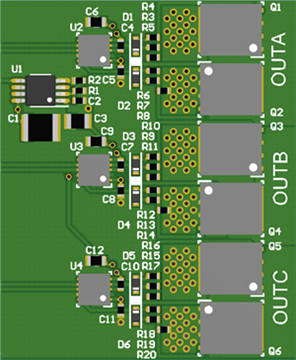

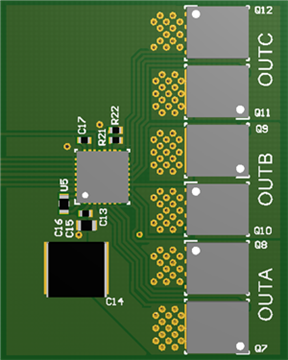

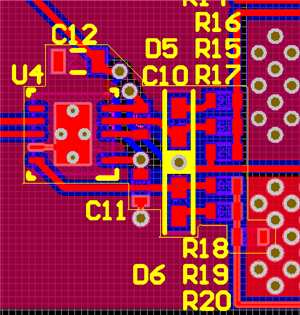

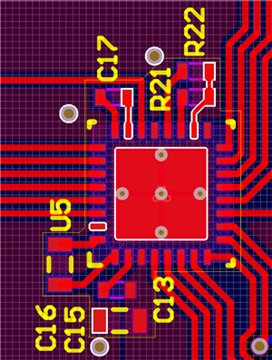

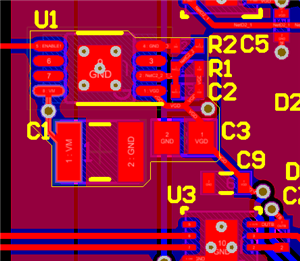

では、具体的に説明していきます。設計ソフトウェアを駆使し、ブラシレスDCモーター・ドライバ用のゲート・ドライバ・アーキテクチャについて、ディスクリート型と統合型を比較するための回路図、レイアウトを作成しました。デバイスについては、TIの多数のディスクリート・ゲート・ドライバから1つと、統合型ゲート・ドライバとして『DRV 8320』を選びました。さらに、TI NexFET™パワーMOSFETの標準QFNパッケージ版を使用しました。この設計ではたまたま標準ディスクリートFETを使用していますが、このアプリケーションには、TIがつい先日発表した2つの垂直統合型ハーフ・ブリッジ・パワー・ブロックを使用することもでき、より省スペースの設計が実現できます。この回路図およびレイアウト作成は、私の乏しいスキルでは荷の重い作業でしたが、2つのブラシレスDCアーキテクチャを比較したい場合に、これらの図を活用していただければと思います。より詳細な画像は、画像をクリックしていただければ拡大表示されます。

表1:ディスクリート型ゲート・ドライバと統合型ゲート・ドライバの比較

一見簡単に見える本プロジェクトですが、実際には数多くの設計やアイデアが投入されています。上記からわかるように、見やすさに配慮して内部レイヤーがない2層の基板を作成しました。ただし、その分レイアウトはより慎重に検討する必要がありました。また、ディスクリート型ゲート・ドライバのゲート駆動設定部と統合型ゲート・ドライバのIDRIVEピン部は、外部FETからの入力信号の立ち上がり/立ち下がり時間が許容可能な値になるように調整する必要があります。各ソリューションのレイアウト部分にも、サイズを最小限に抑えるために微調整が必要な箇所が多数あります。すべてを詳細に説明しようとすれば、この記事はブログ記事というよりアプリケーション・ノートになってしまったことでしょう(そして、集中できなくなるか寝てしまう読者が増えます)。

最後までお読みいただき、ありがとうございます。ここで紹介した情報を、今後のブラシレスDCモーター・ドライバの設計にお役立ていただければ幸いです。

DCモーターで友達を増やす計画はまだあきらめていません。皆さんはどのように取り組んでいますか?ここで紹介した設計について不明な点はありますか?モーター駆動について詳しく知りたい場合は、このブログを引き続きお読みください。

参考情報

- ブログ「革新的な電動工具ソリューションの開発を促進する高電力密度の需要」

- リファレンス・デザイン「18V / 1kW、160Aピーク、効率98%超、高電力密度ブラシレス・モーター・ドライブ」

- 製品資料(英語)「Understanding IDRIVE and TDRIVE in TI Smart Gate Drivers」

- ブログ(英語)「The story of motor-drive integration」

※すべての商標はそれぞれの所有者に帰属します。

※上記の記事はこちらのBlog記事(2017年7月19日)より翻訳転載されました。

*ご質問はE2E Support Forumにお願い致します。