Dear all,

I have 2 qestions,especially in TAS5766 register setting,need your support ,thanks~

1.after read TAS576x technique document(TAS576xM 2x50W/4Ω PurePath Smart Amp) ,except

Analog gain can controlled by Ra(to GND) and Rb(to GVDD) ;

DAC gain controlled by Page 1/Register2(HEX 0x2) and Page 1/Register 7(Hex 0x7) ,

Does any actual register exist for volume control ?

2.I got TAS5766 parameter file (TAS5766.h) from Learning Board and PurePath GUI ,

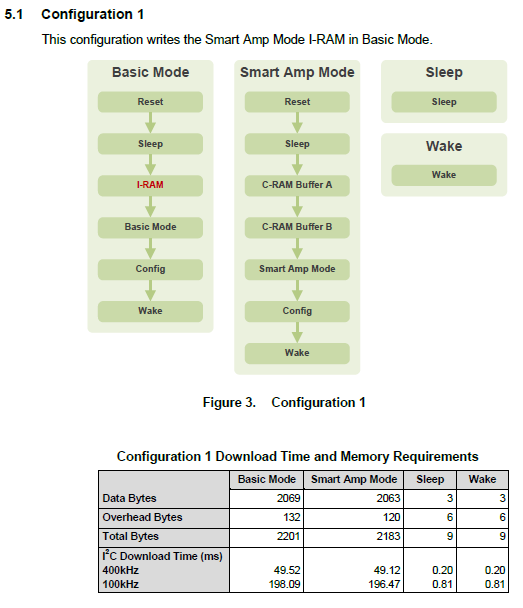

there are almost 4 thousand I2C commands which I need to write to TAS5766,I prepare to send

the 4 thousand I2C commands at system initialize stage ,but I think sending 4 thousand of I2C commands

will take a little of time ;

the 4 thousand commands includes :

page 44 ~ 52

page 62 (Coefficient Memory B)

page 63 ~ 70

page 152 (Instruction Memory)

page 153 ~ 169

page 0

page 1

In order to saving system booting up time,

Does all upper pages I need to program at system initial stage ?