Hi team,

Our customer have two questions about TPA3251

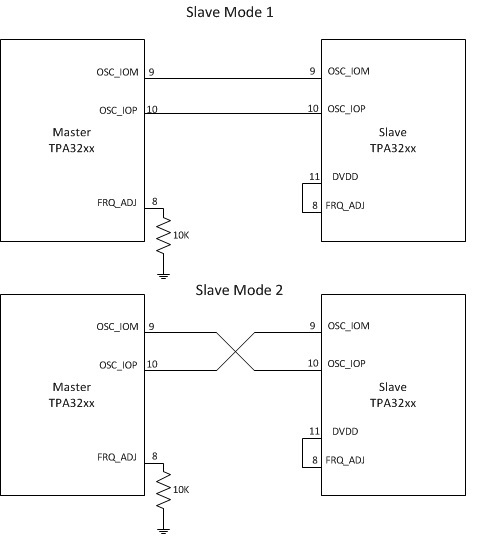

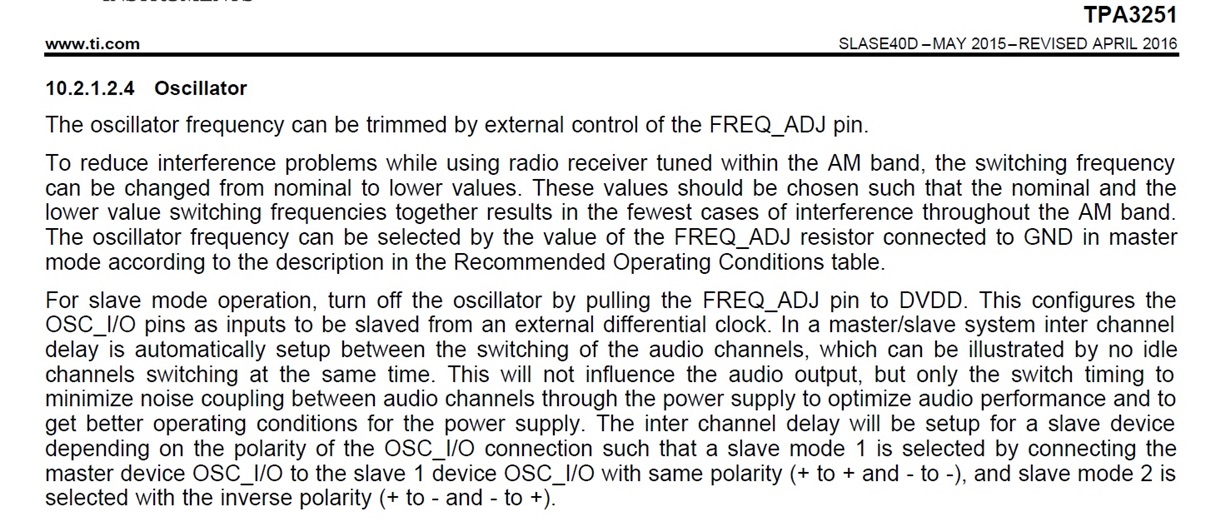

- How to sync two TPA3251? If using TPA3251 as a slave device, pull up pin9/10 to VDD and input clock as a PWM clock? Could you send me a simple current connection block diagram to me?

- In our EVM user’s guide description ,it is the AD mode, But from the LC filter connection of EVM SCH, It is BD mode,Why?