Hi,

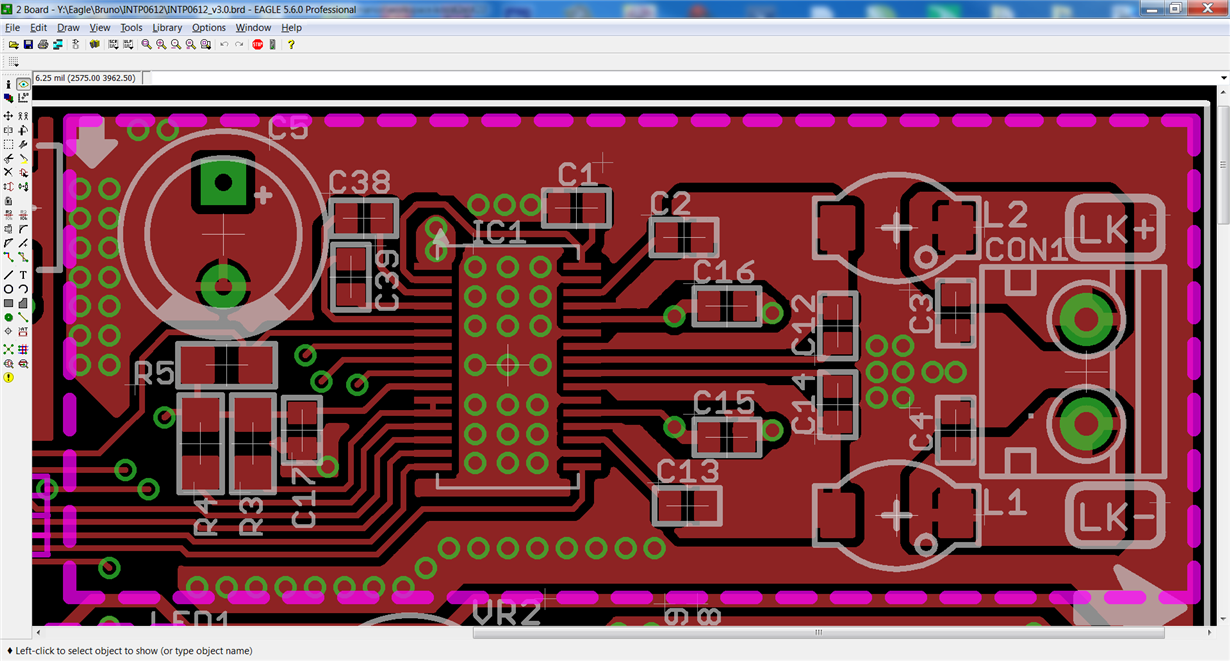

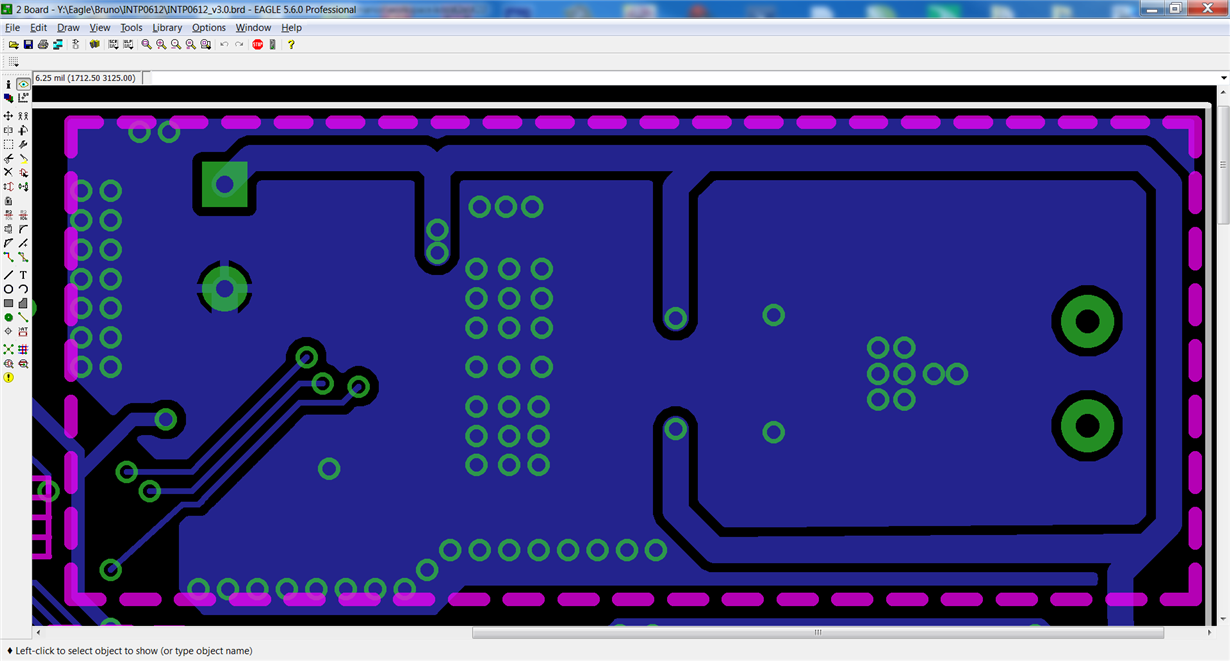

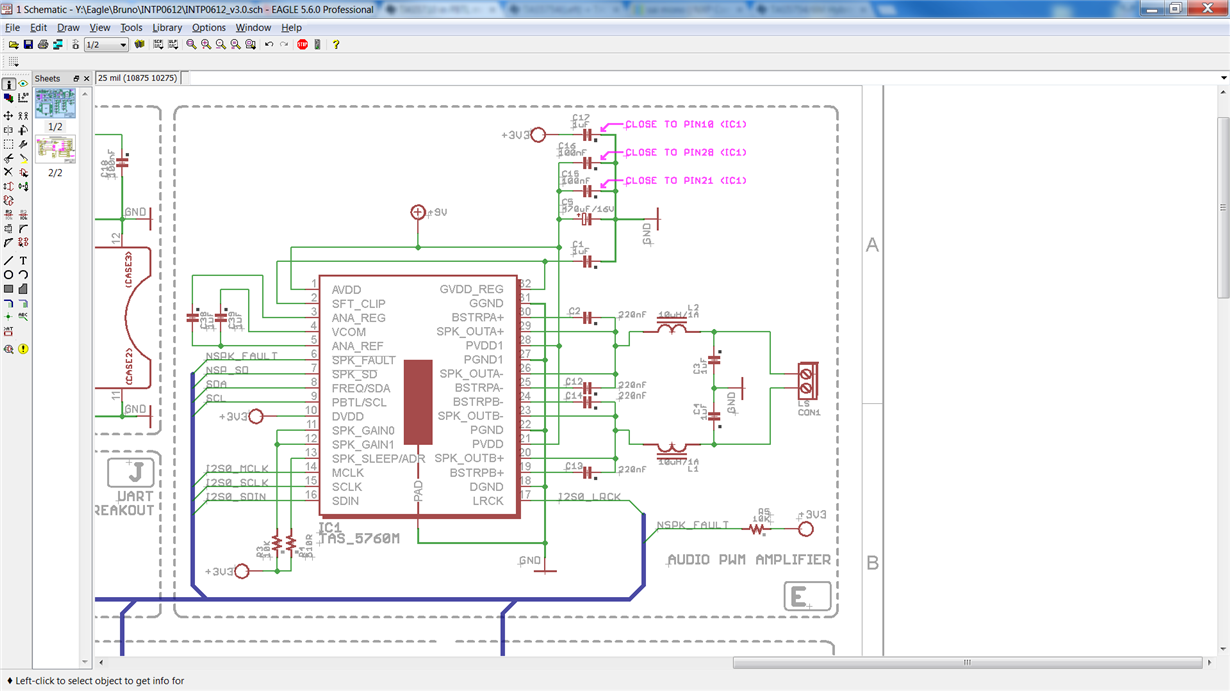

We developed a board using TAS5760M designed in PBTL mode MONO ,software control, working with the 32-Pin DAP package.

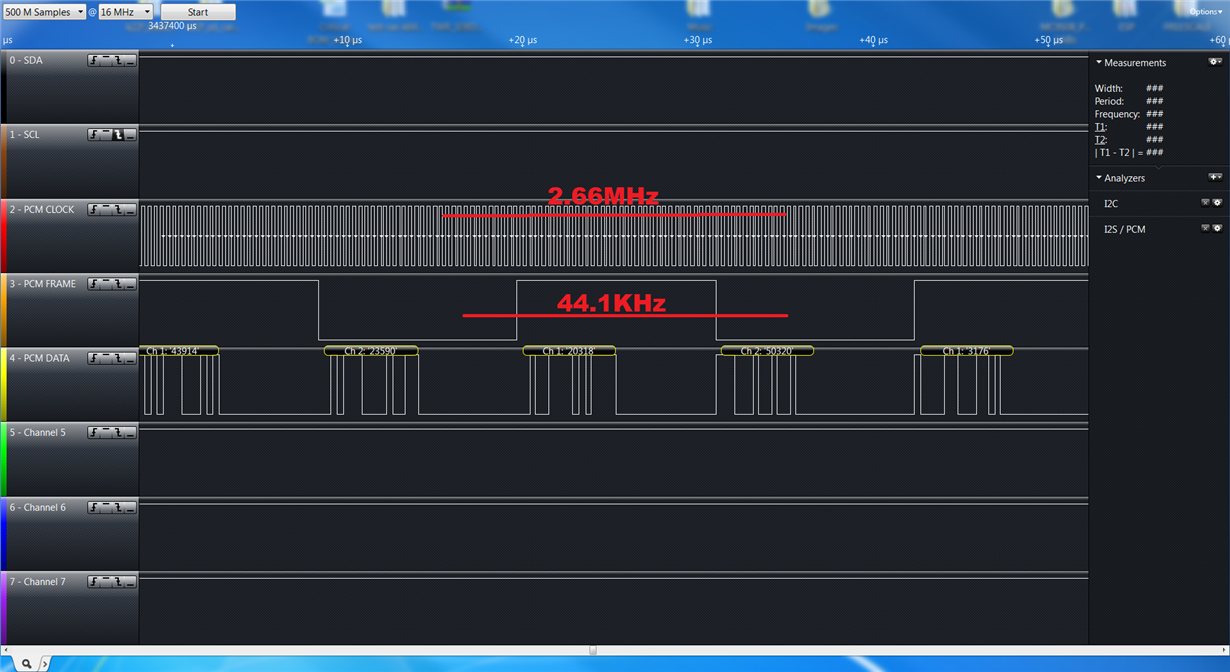

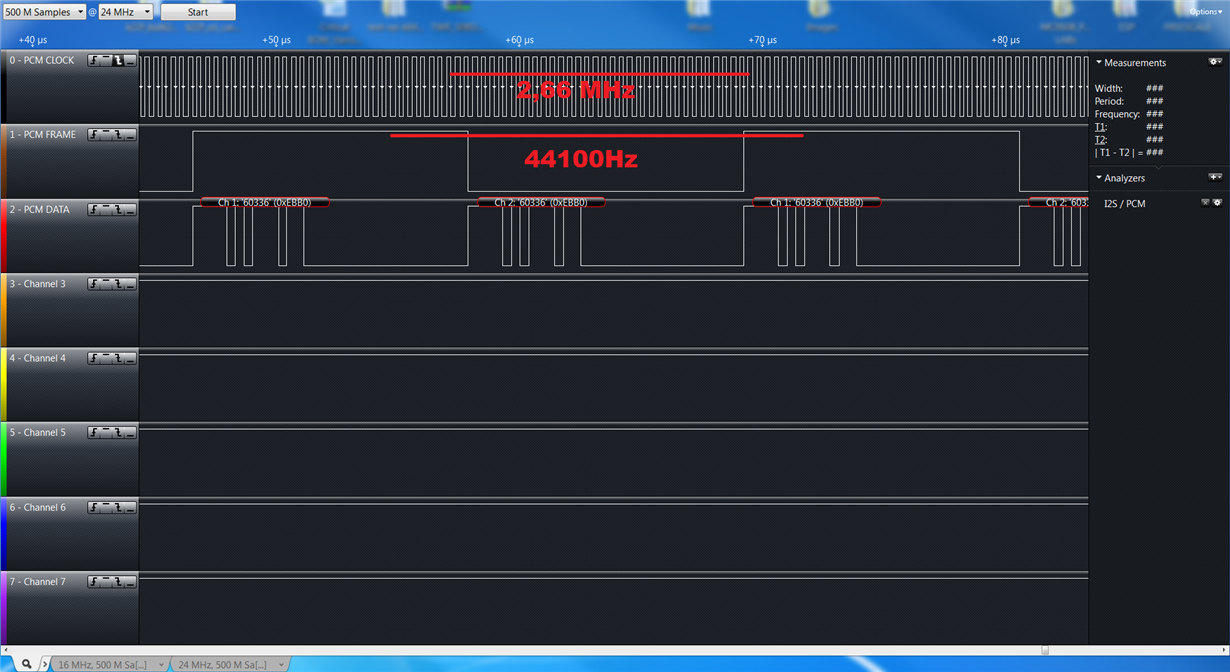

Unfortunately we get an error response on the I2C channel on Fault Configuration and Error Status Register, which is 0x08 (CLKE bit is toggled) .

This happens during initialization and also during playback.

We searched the entire datasheet, but we did not found any information about the I2S bus configuration in order to work in PBTL MONO software control mode, for example we can't resolve the following issue:

1. Is it neccecarry to configure the I2S bus from microcontroller side in mono channel (Left or Right) or just send Stereo (Left and Right) and the TAS automatically reconfigured to one channel?

2. Which is the recommended I2S format?

Also please check the attached images of the ".brd" and ".sch" of our PCB and mention if any problem occurs from wrong in its design.

Thanks in advance,

Intelco Team