I finally got my TAS5754M up and running. It's ACK my commands and takes I2S input.

Problem is that sound is cracking up. I suspect it has something to do with the I2S clock settings.

Input is a Microchip BM64 BT module:

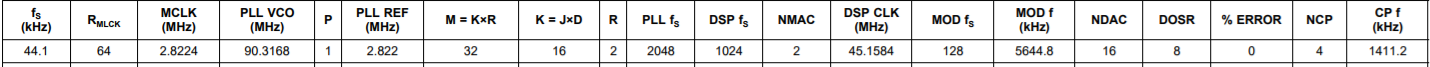

-LRCK/FS=44.1Khz

-SCLK=2.82Mhz

Currently using 3-wire mode with auto clock set which doesnt seem to work right.

I'm not sure on which settings to use (i.e. which registers to write to), can somebody help please.