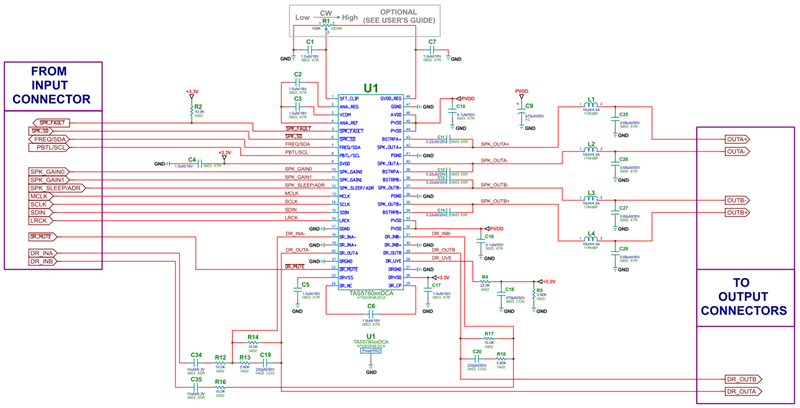

Other Parts Discussed in Thread: TAS5760XXEVM

Hi,

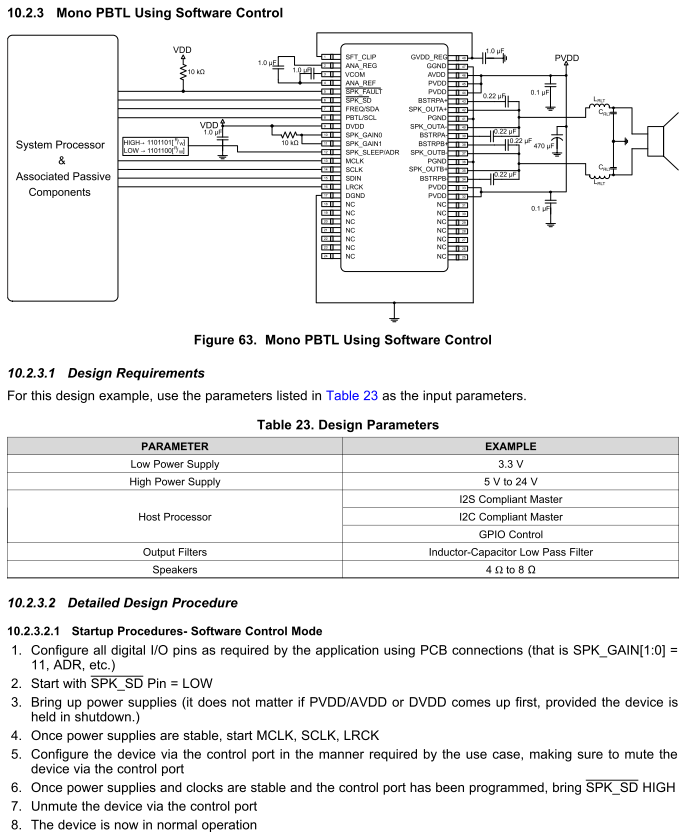

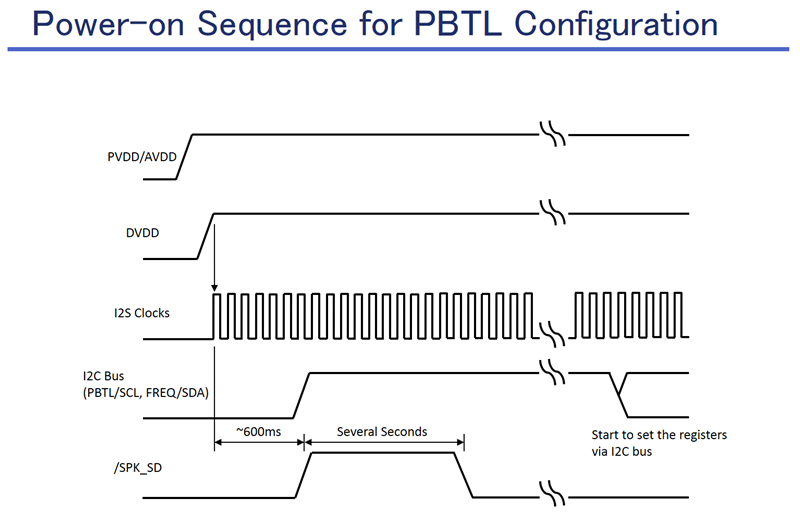

There is the point that doesn't obey the power-on sequence which is mentioned for PBTL configuration in TAS5760M data sheet as below.

Do you have any concerns when /SPK_SD pin is de-asserted to "high" for several seconds if the external components are set in PBTL configuration before setting the registers via I2C bus after the power-on ?

At this time, I2C clocks have already been applied to TAS5760M but the zero data is input to TAS5760M as the audio source.

Best regards,

Kato