How is magnetic immunity of INA if placed half footprint pins-1-4 bottom of PCB yet centered under one shunt pad located on top PCB? So TSSOP package aligns center in only one of the shunt pads. It seems the long width of the TSSOP package was designed for tight layout situations described below.

Monitoring low side PWM where one half TSSOP package pins 5-8 may sometimes lie directly under the shunt ground feeds top side of 0.094" thick PCB.

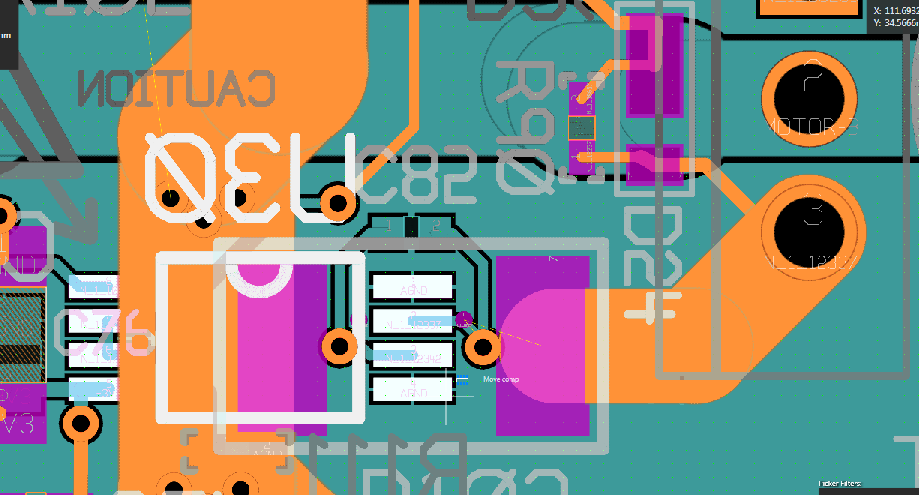

Very short leads roughly 0.5mm from shunt to pins-2,3 and require 1 via from Kelvin on each side of shunt pads similar to 11.2 layout example.

Like this: