Hi,

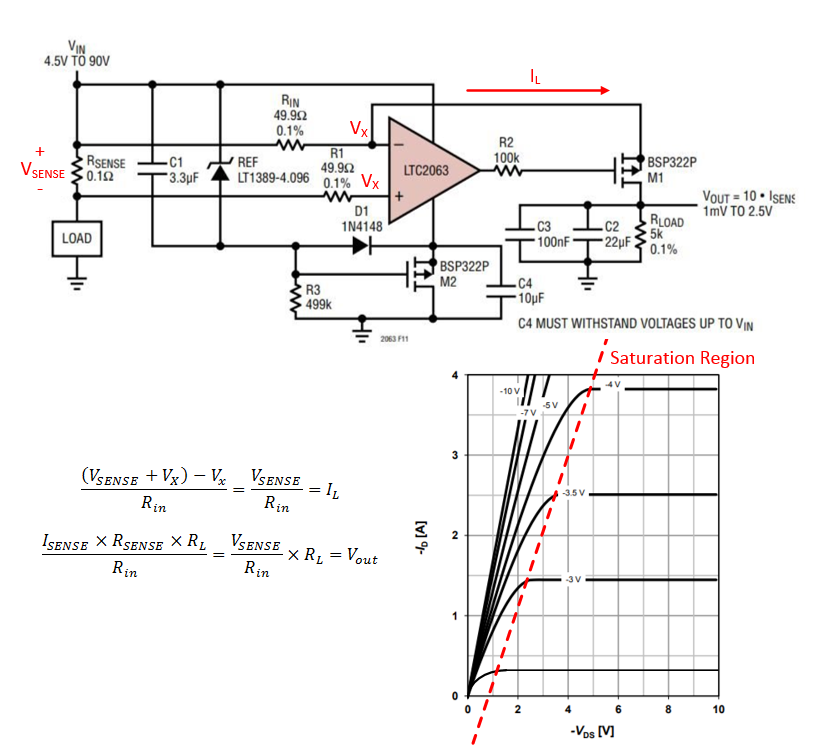

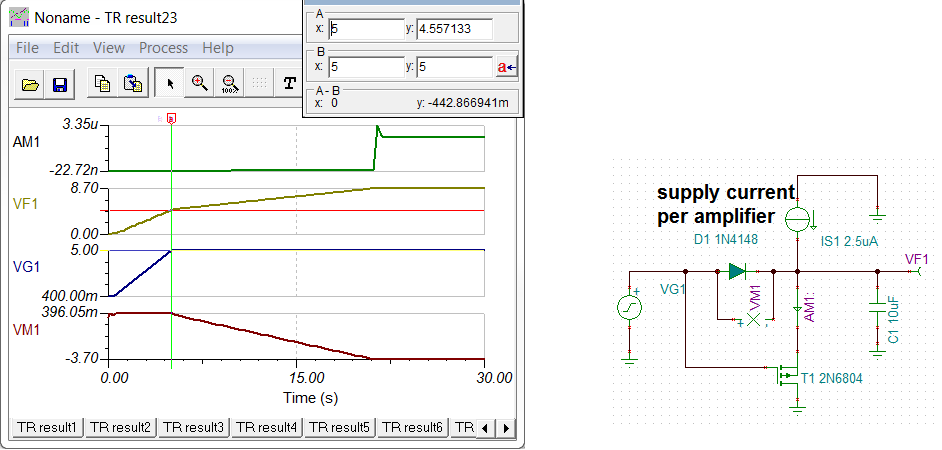

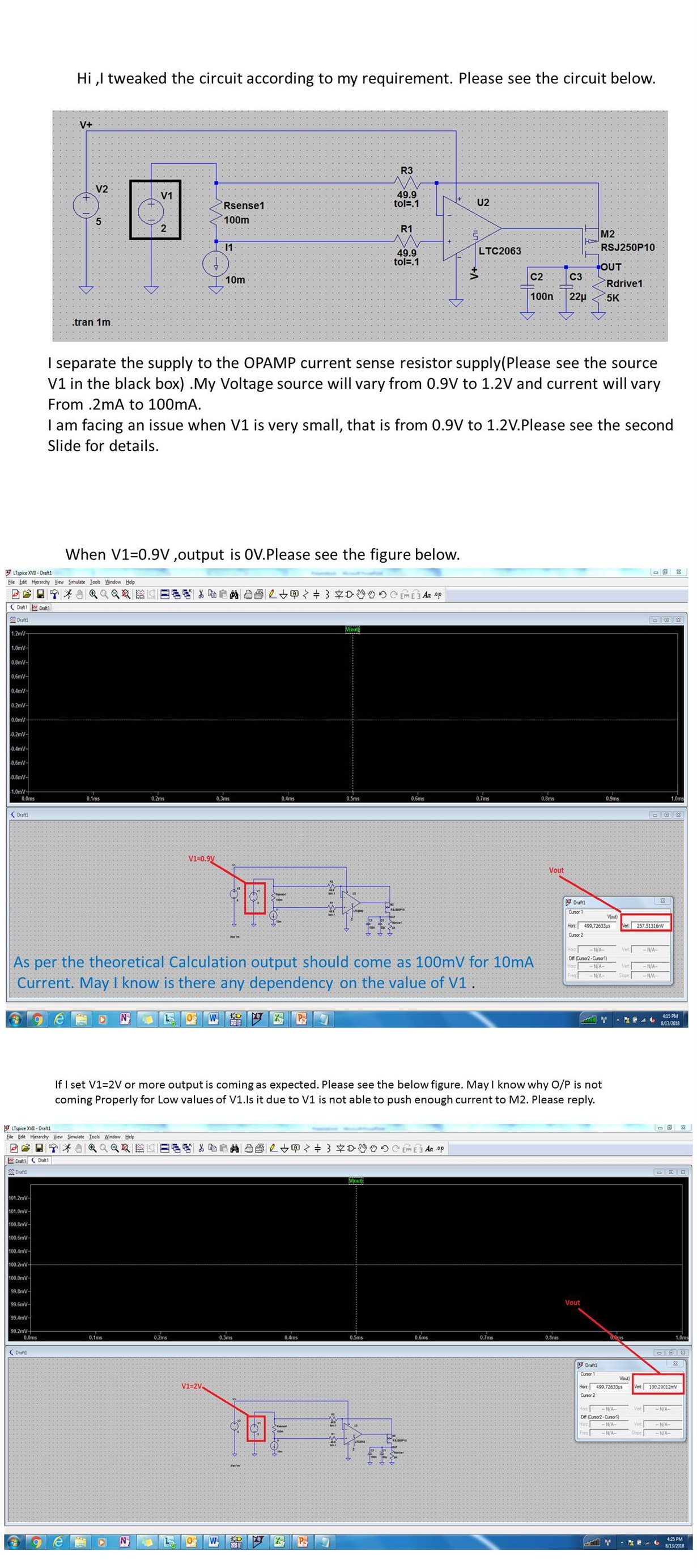

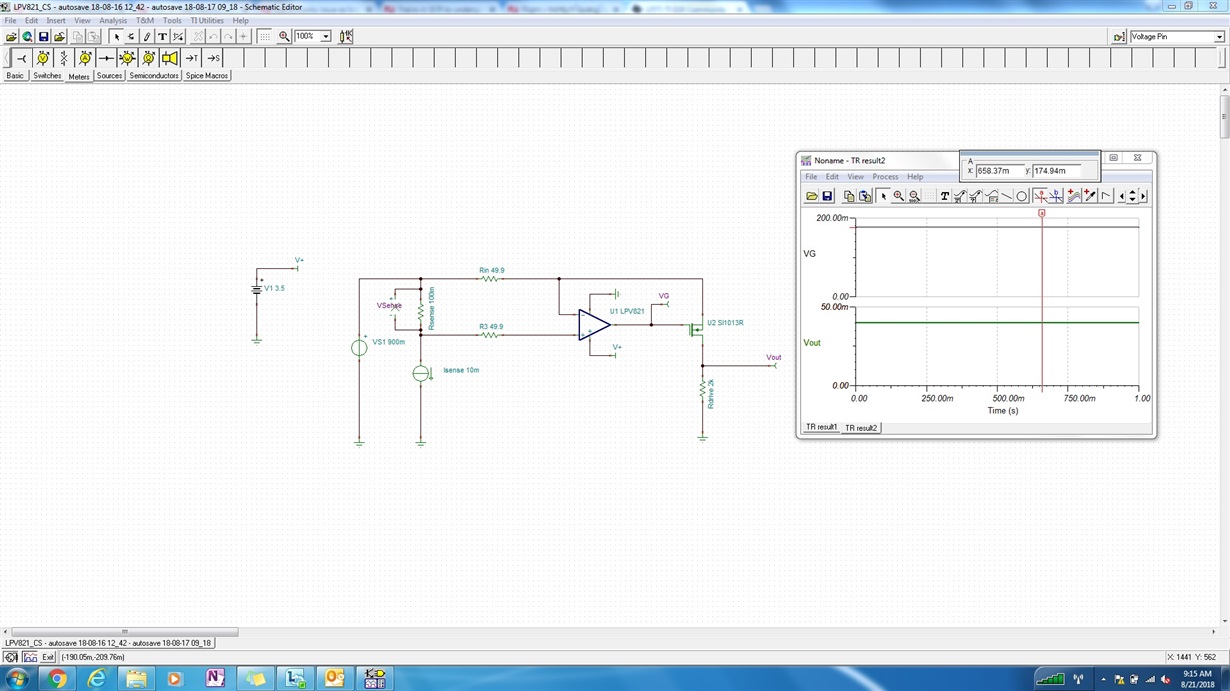

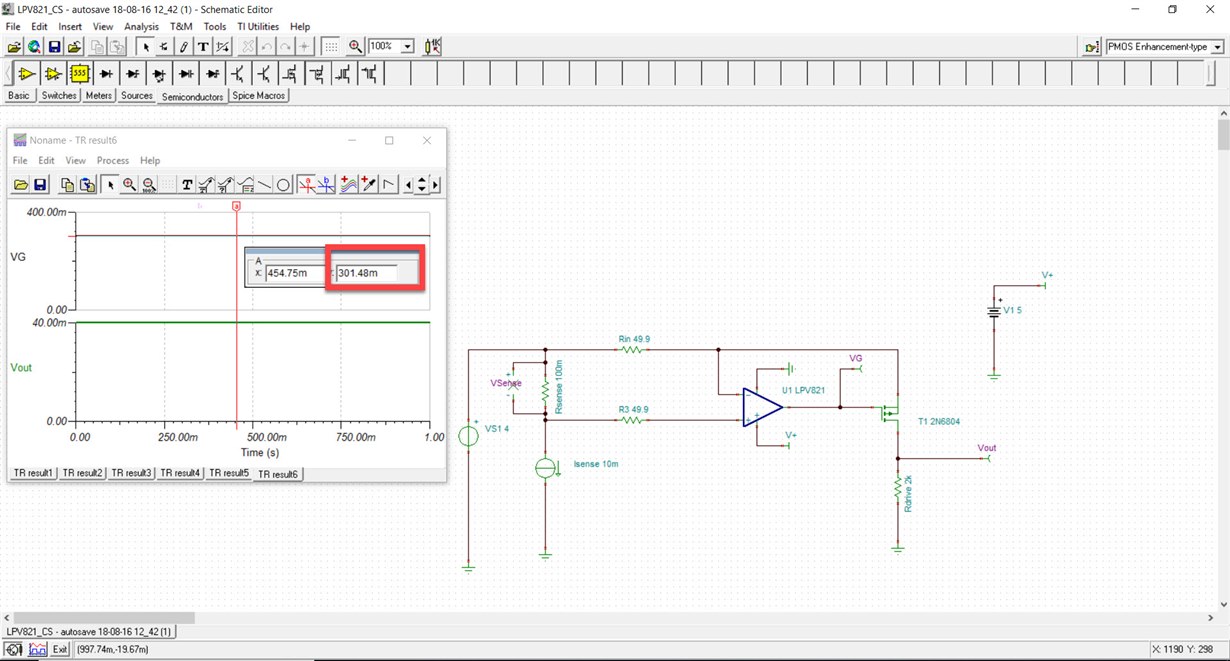

Please find the attached current sensing circuit.

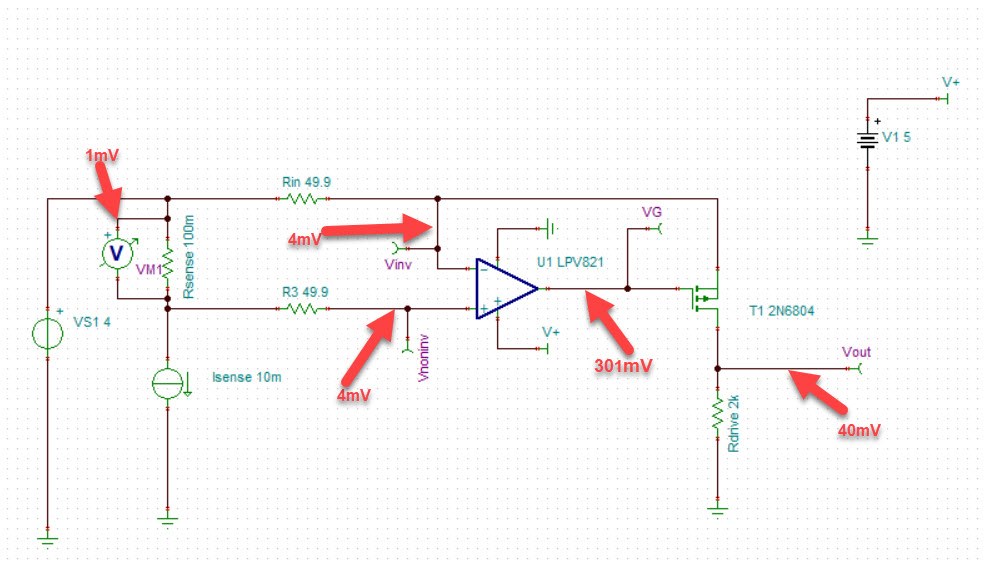

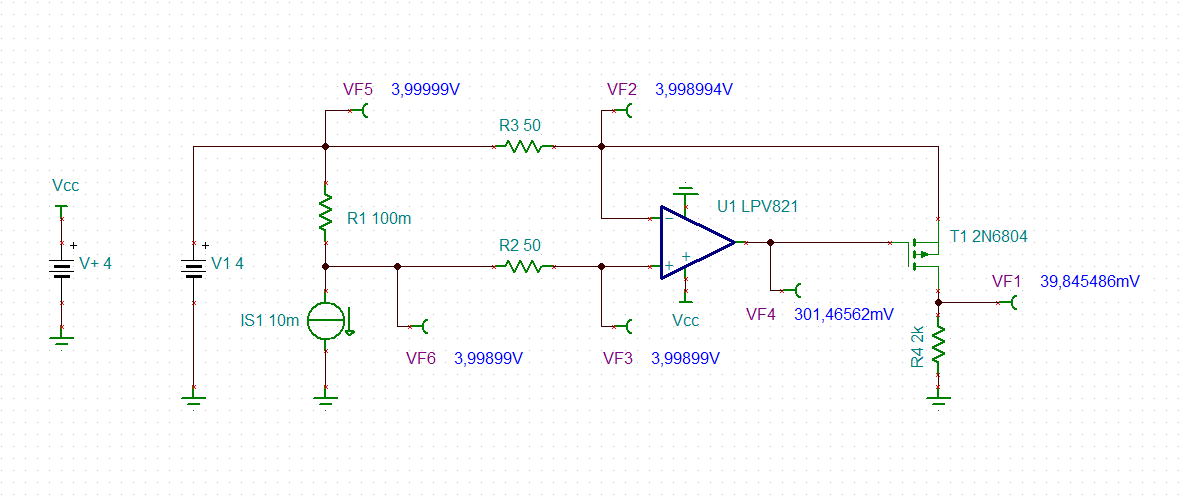

It's output voltage equation is given by VOUT =( RLOAD *RSENSE* I SENSE)/RIN.

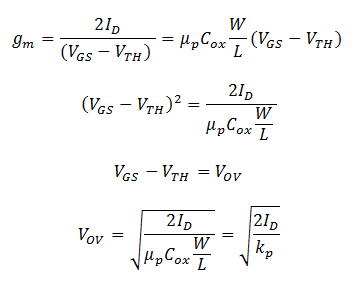

As per my knowledge the equation is derived as given below

Current flowing through RIN =(RSENSE*ISENSE)/RIN

The same current flow through RLOAD,multiplying this current with RLOAD will give Vout.

My confusion is to derive like as shown above voltage at the inverting pin should be zero .As per my knowledge it is not zero in this case because

non-inverting terminal is not connected to ground.Please correct me if I am wrong.

May I know how the Equation of Output voltage is derived.

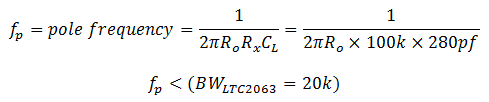

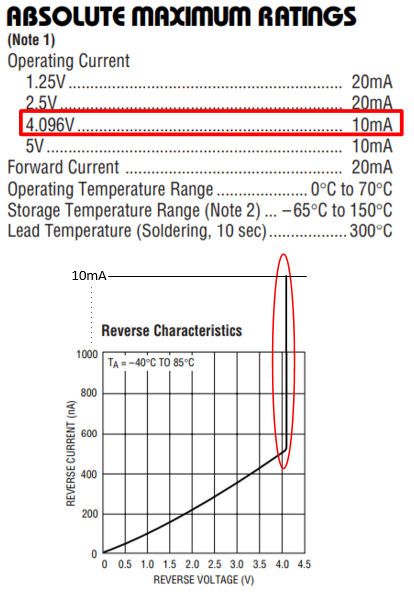

May I know the use of mosfet's M1,M2,D1 and Ref.

Regards

Hari