Other Parts Discussed in Thread: UCC27714,

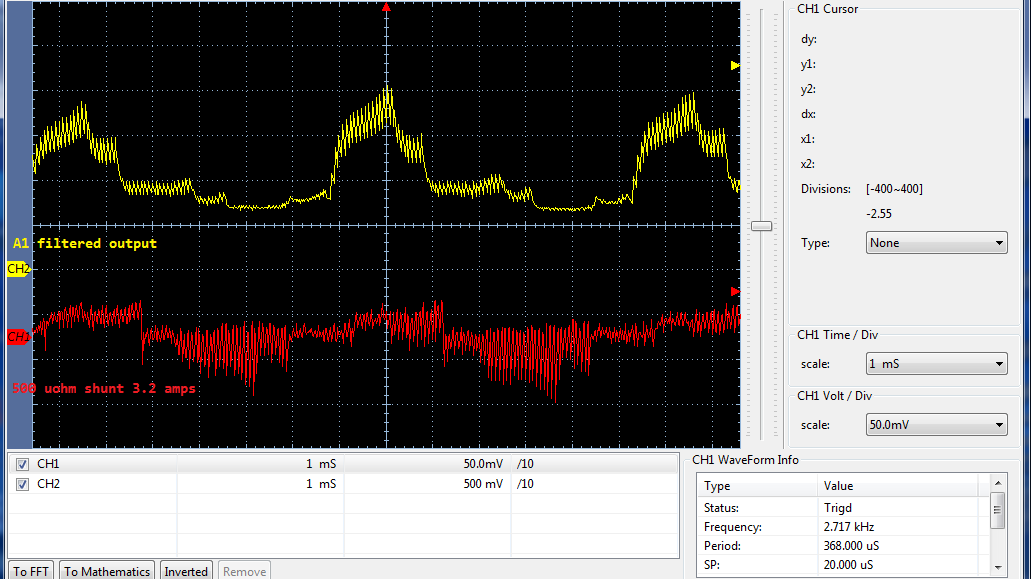

Seemingly low side monitor of idle inverter leakage current prior to PWM being applied might be pre-biasing the already internally biased INA amplifier.

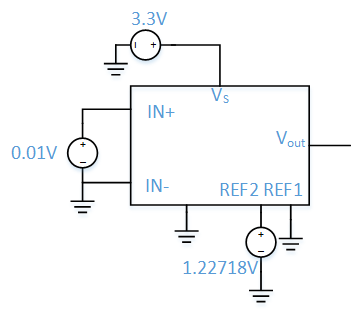

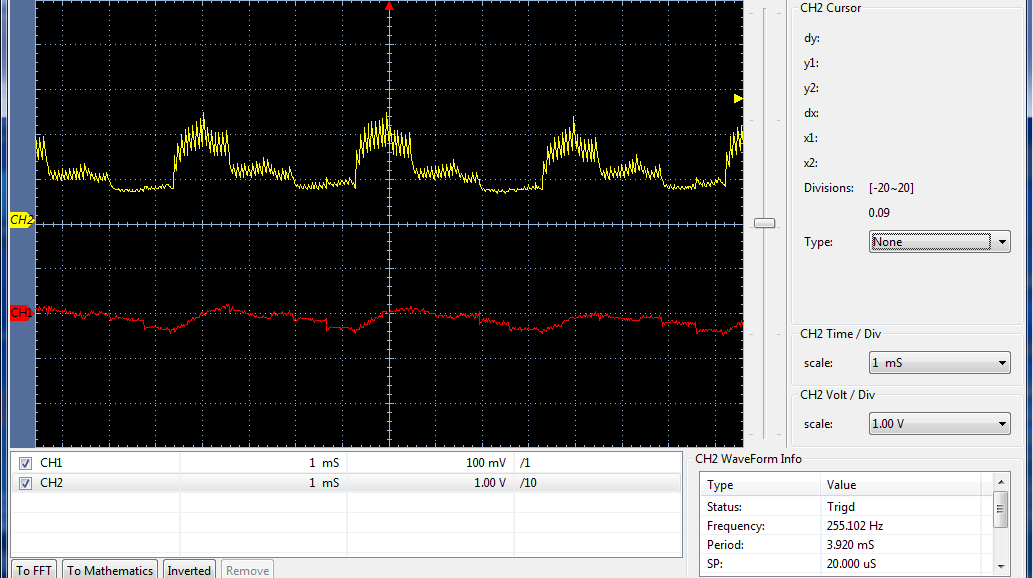

Data sheet show VOS=5uv typical (IB) bias 90ua typical (IB+/- Vsence=0mv) yet typical inverter idle INA output noise when driven from UCC27714 gate drivers nears 680mv @20mv leakage across any low side shunt. Lower resistance value shunts do not seem to lower proportionately the internal pre bias from over driving INA output when PWM actually initiates real time inverter current flow. REF1=GND, REF2=+1.225v

Seemingly in series phase monitor would not have the same impact from low side NFET leakage current at higher inverter DC potentials nearing or exceeding VCM. Seemingly in phase monitor idle CMMV measured across a shunt would be far less and not impact INA internal bias circuit as does low side monitoring where inverter bias is always present prior to each and every PWM cycle. Does it not seem possible INA pre biasing the input of the PWM rejection circuit can produce excessive output measure overshoot when placed as low side current monitors?

Idle mode leakage across shunt, INA output signal inverter via clean linear 80V source filtered 28000uf DC. The INA feeds from 3v3 LDO after 5v buck switcher via isolated linear 24vdc.