Other Parts Discussed in Thread: TINA-TI

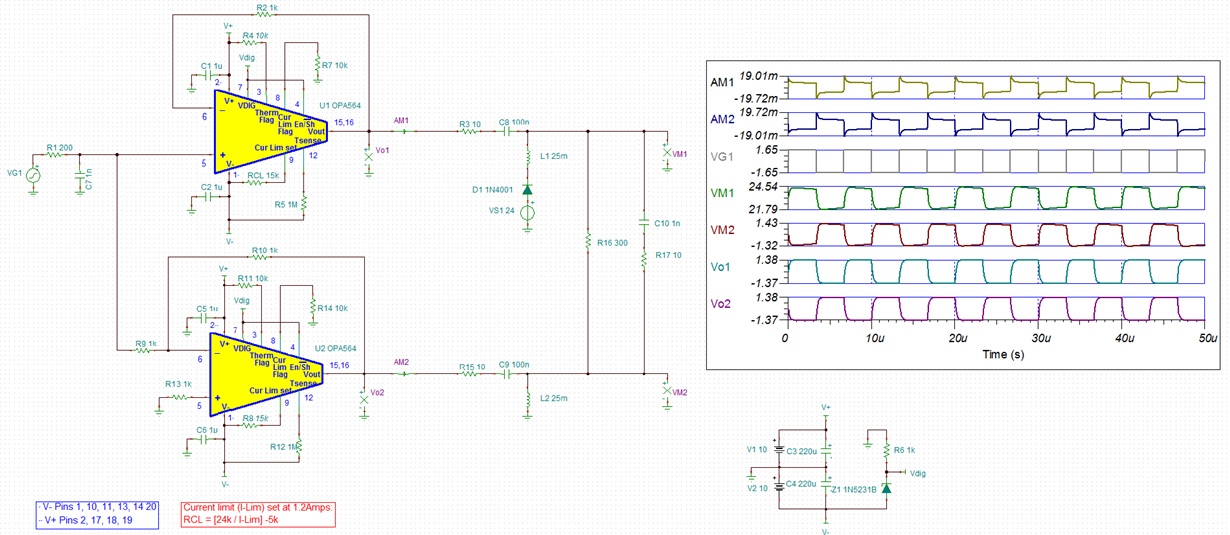

I am breadboarding a prototype which is in great hurry, and I am using two OPA564 devices.

I'm trying to achieve a PLC differential output on top of a 24V power line.

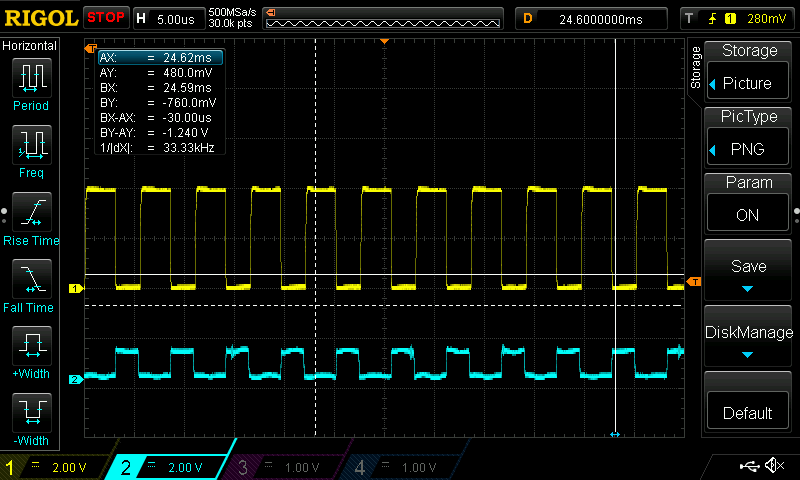

I have an input signal square wave of 100-200 kHz with 3.3V amplitude.

One of the OPA564 is configured as a buffer (for the +24V side) and is working great!

The other device is configured as a simple inverterand I cannot get this one to work at all.

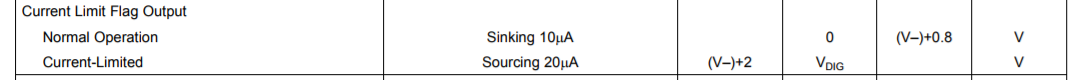

I am seeing pulses on the OC flag but it is mostly high. even if I don't have anything connected to the output, or input.

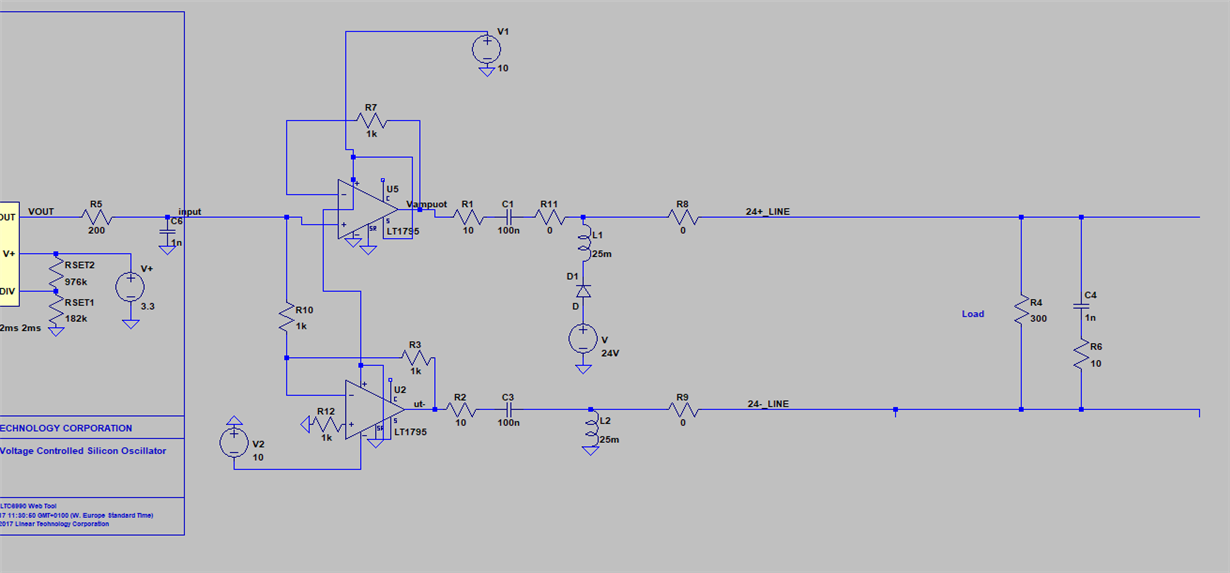

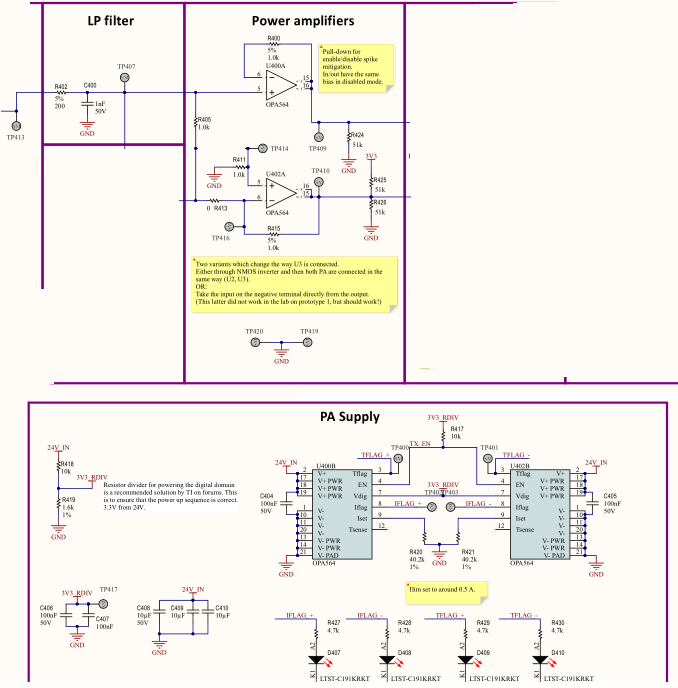

I've hooked it up as my LTspice simulation (ignore the strange parts and really poor job in making a readable schematic, sorry!)

but with a single 10V supply. (and haven't connected any output to it yet because I couldn't get it working)