Other Parts Discussed in Thread: LMP7715

Hi all,

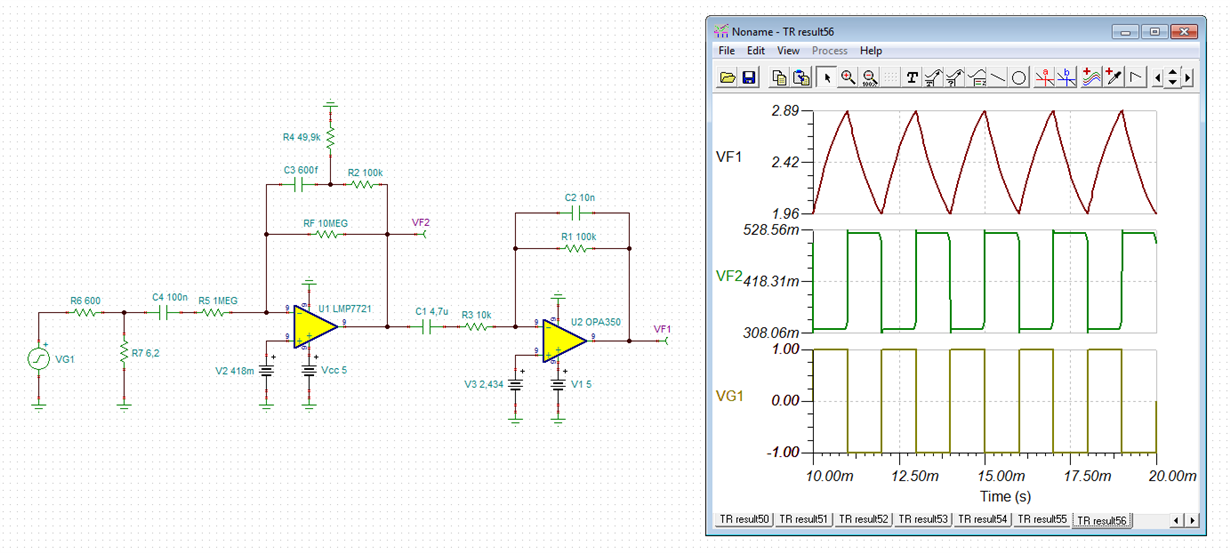

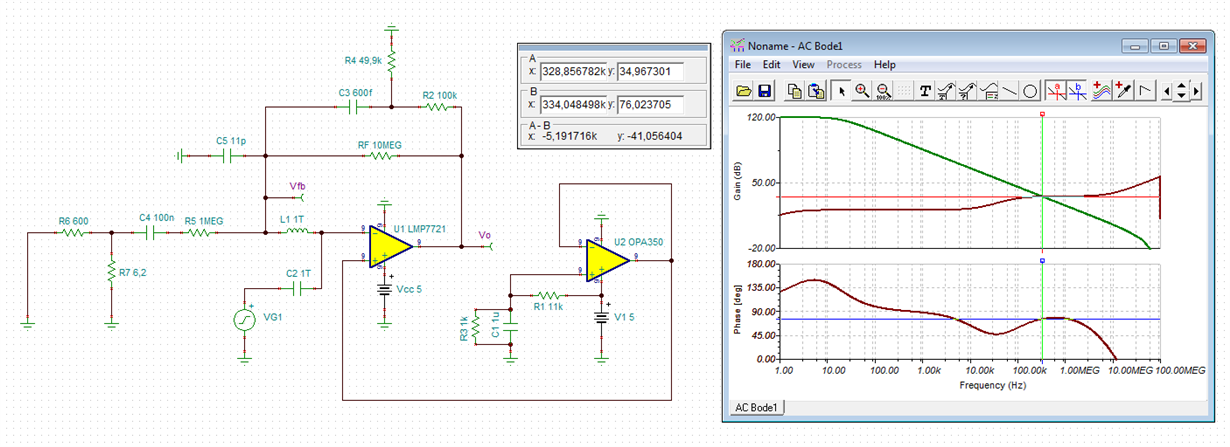

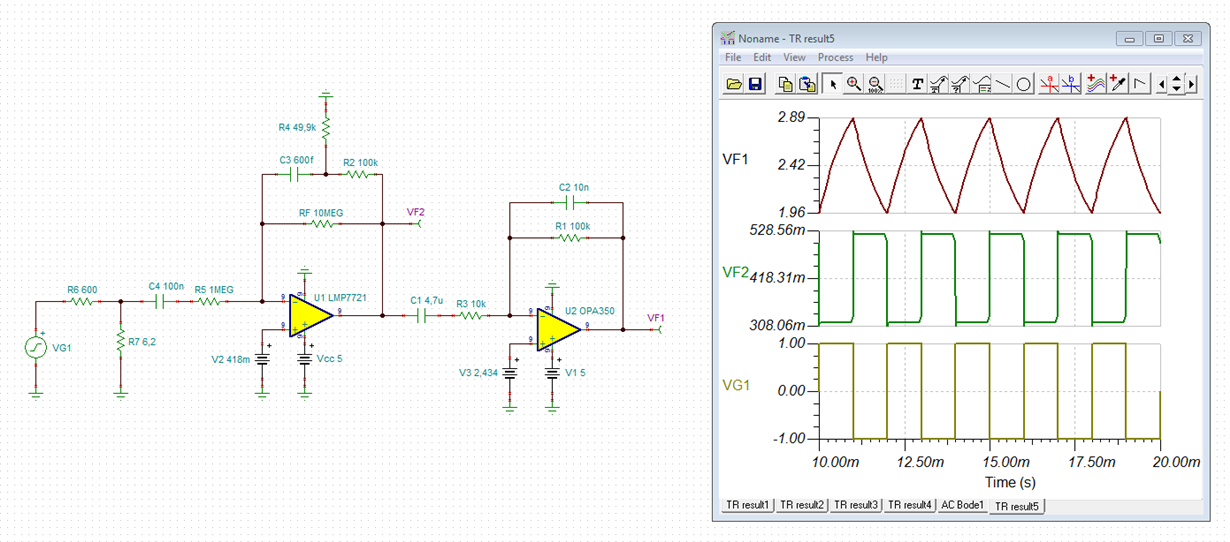

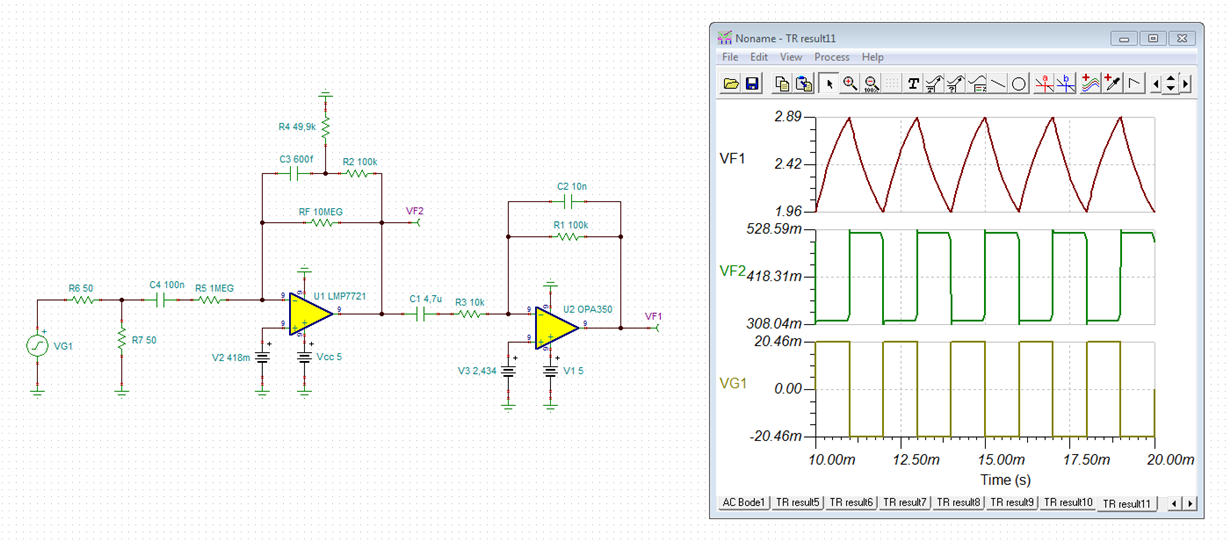

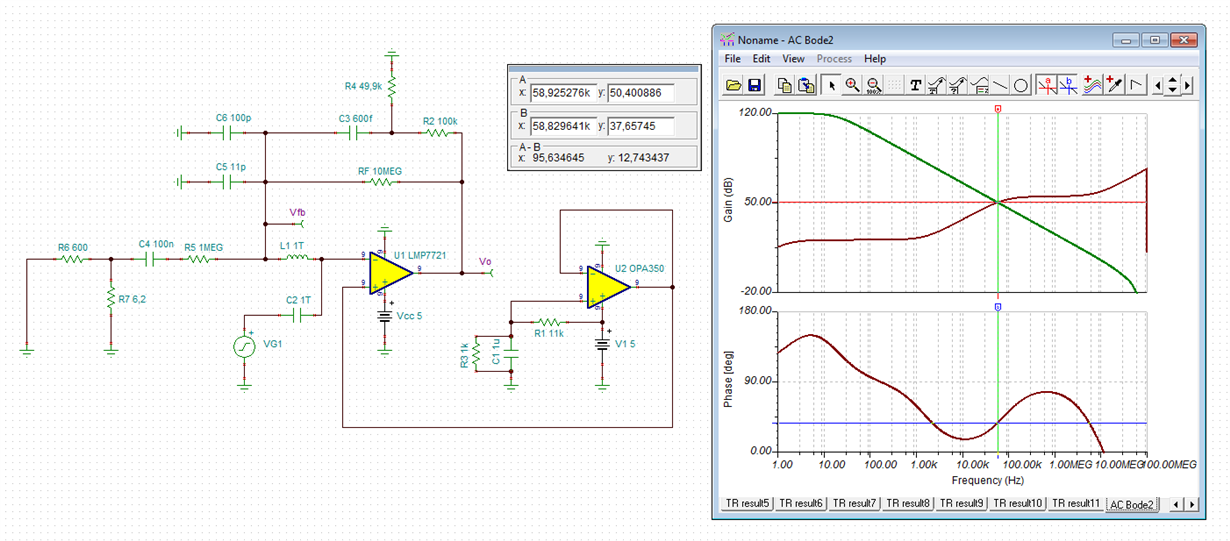

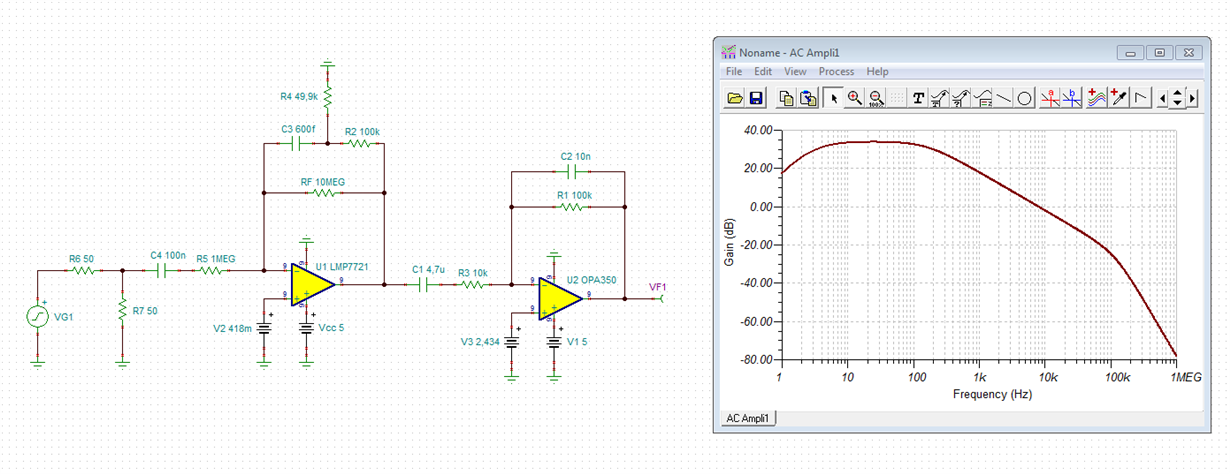

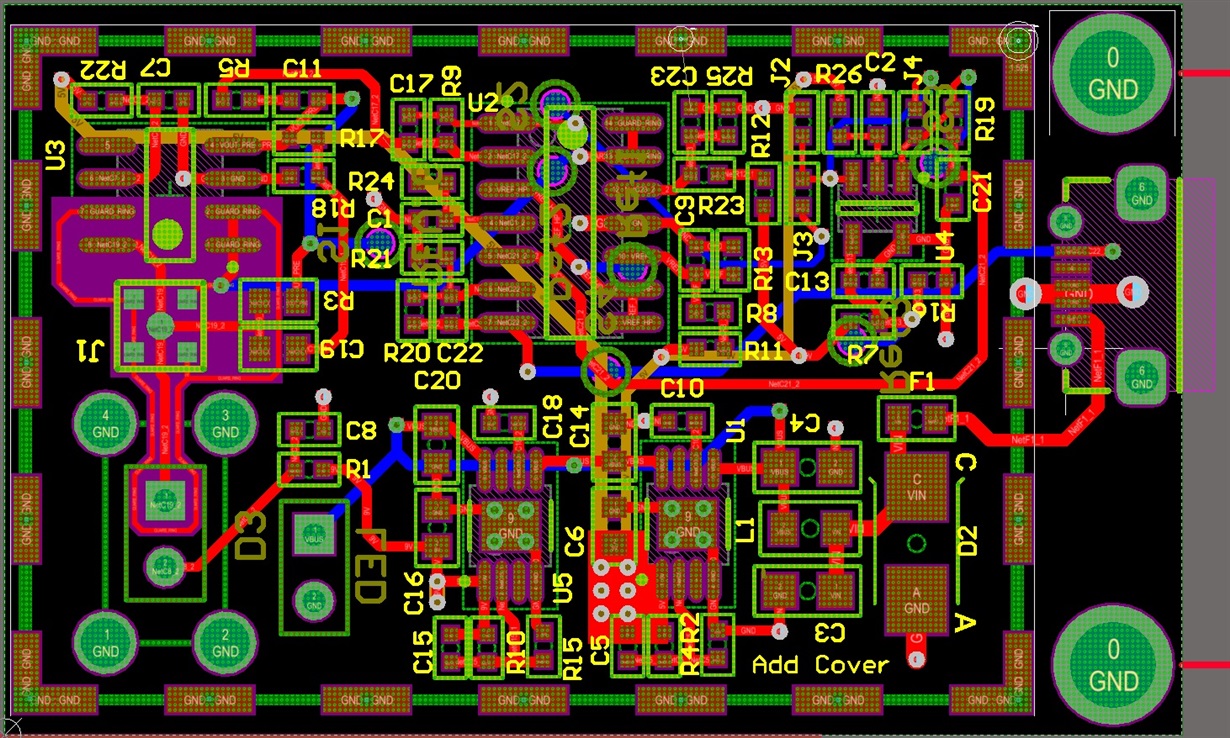

I am modifying the circuit for a gamma radiation sensor used in our radio-synthesizer. Original design is attached. SOF-1861031106 - radAFERevG_HI.PDF As part of modification for noise and stability, I have decided to add a guard ring as recommended in the datasheet and LMP7721 multi-function evaluation board user's guide. In one part the datasheet states: "A cover or shield connected to the guard should protect the circuitry above (or below) the PC board". And in another part it says: "The guard trace should not be relied upon as the only method of shielding. A ground plane or shield should surround and protect the guard from large external leakages and noise, as the guard trace has the potential to couple noise back into the input".

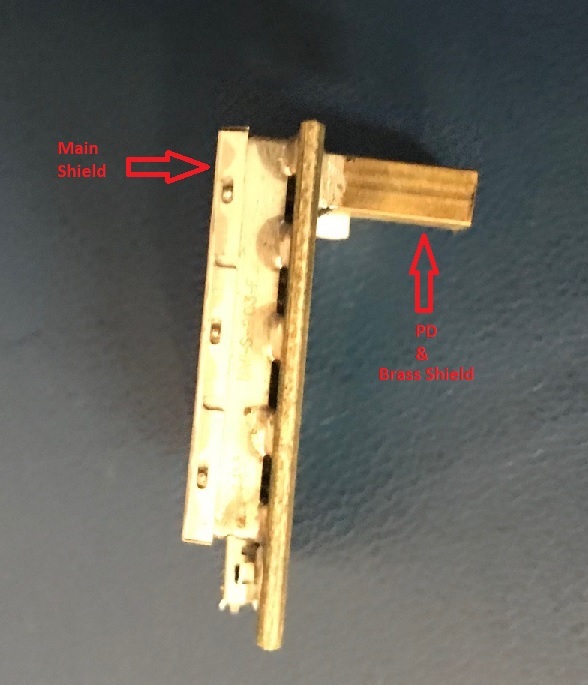

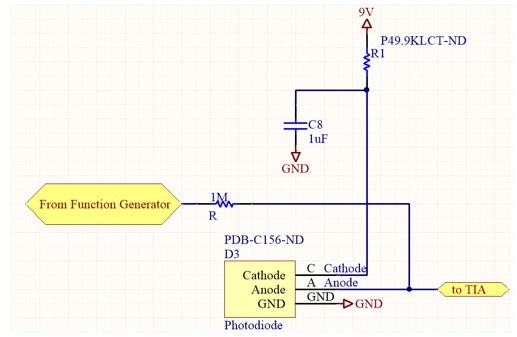

As you can see on the schematic, there is a grounded shield that covers the whole circuit, and there is a second grounded shield that covers the PD which is mounted on the back of the board. Now the question is that;

1- Should I connect the main shield to the guard rind or shall I leave it connected to GND just the way it is?

2- Shall I connect the shield for PD to the guard ring or GND?

Thanks