Good morning,

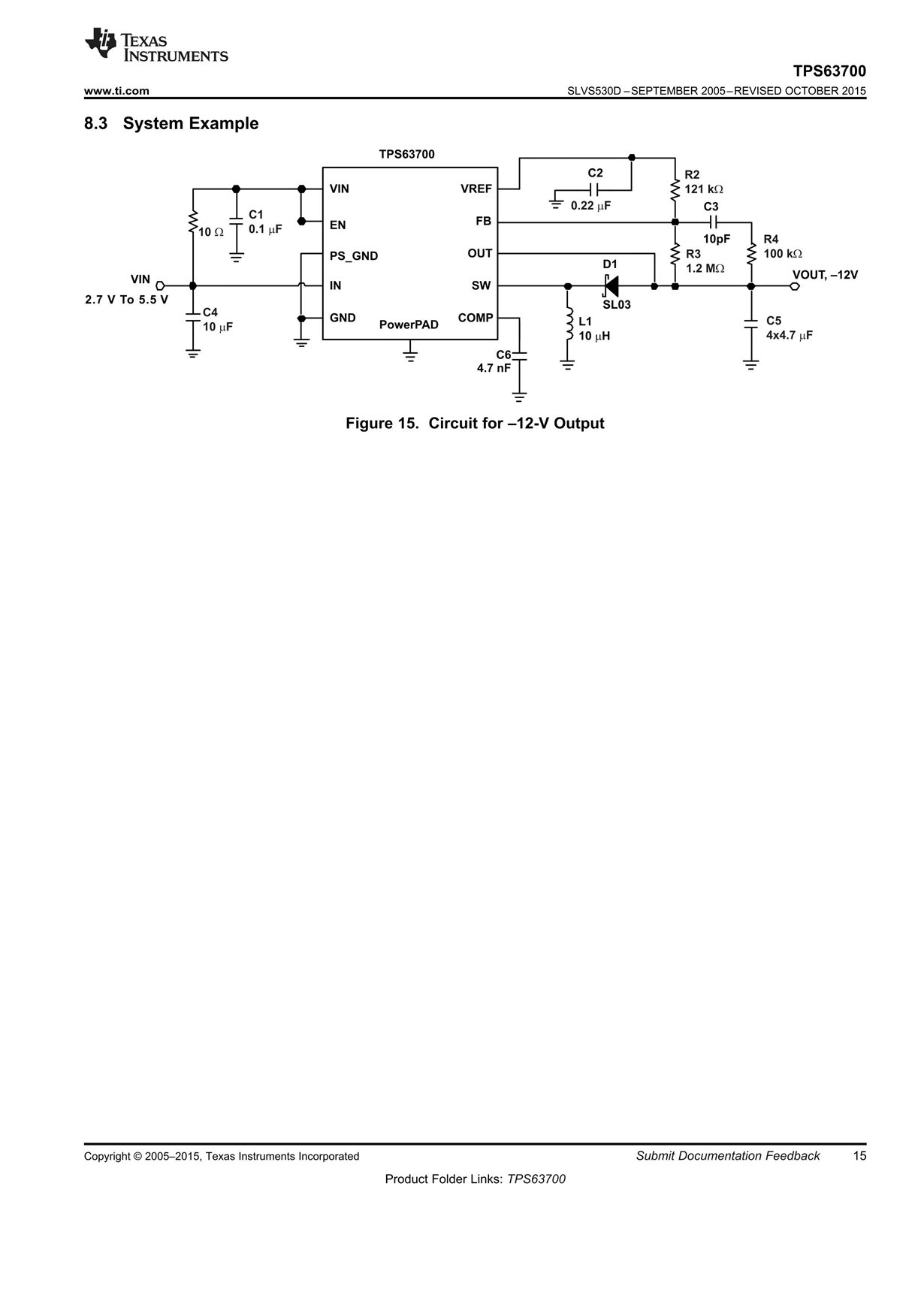

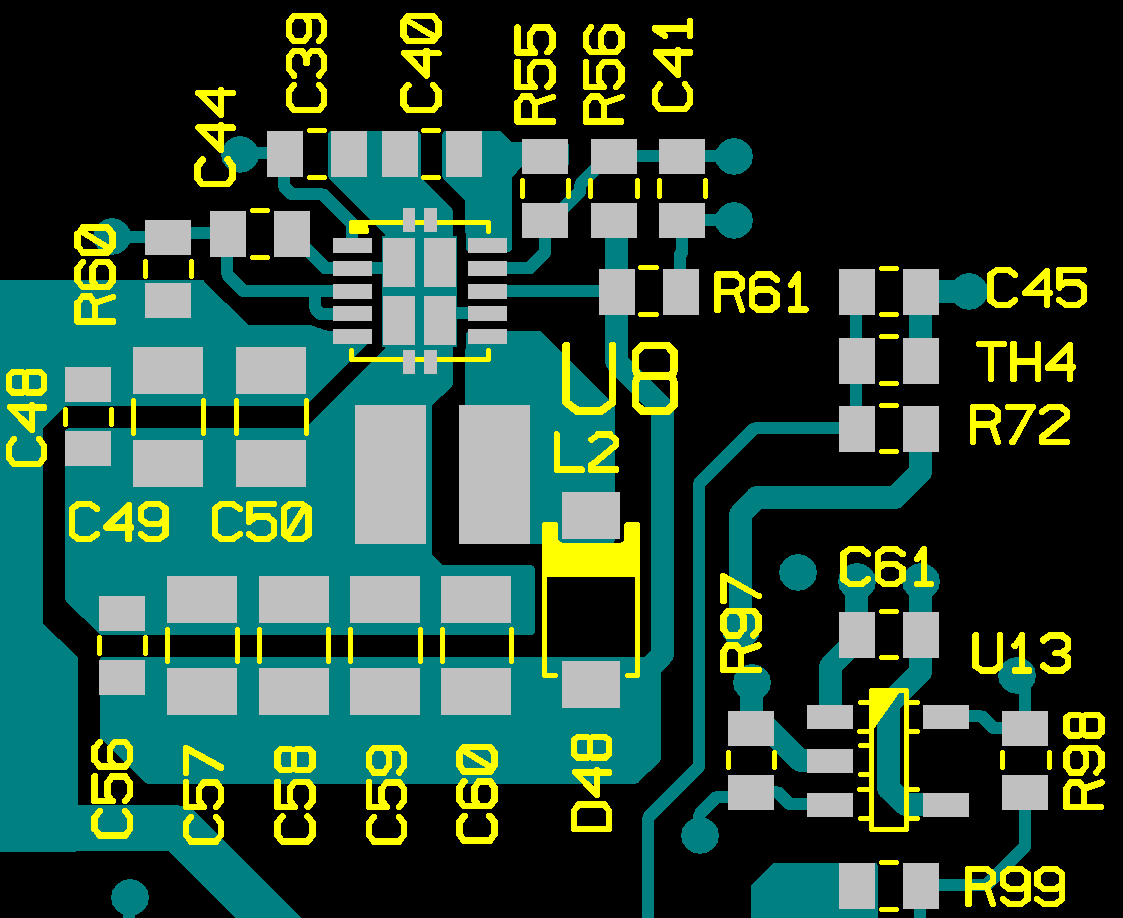

I'm using the component with 5V input and output -12V implemented with the wiring diagram of the attached datasheet. The circuit is part of a board where there are power switches that inhibit the output of the TPS.

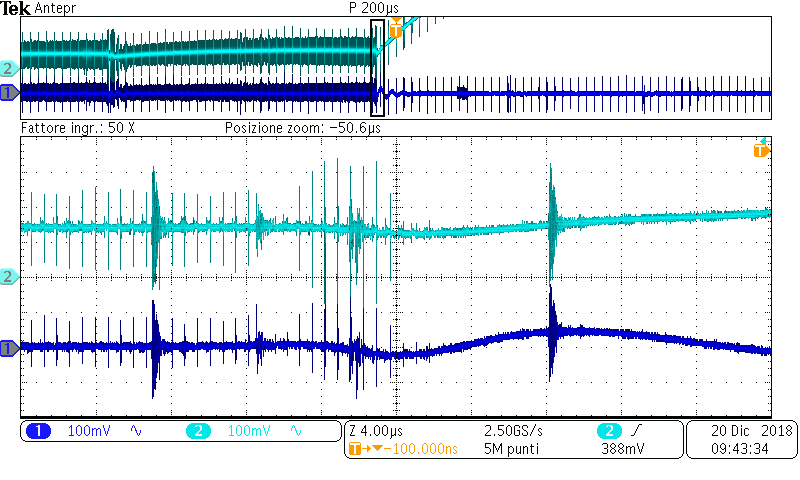

To solve the problem, since I could not modify the layout, I reduced the impedance of the external resistor divider connected to the FB pin, with 30K2 between Vref and FB and 300K between FB and Vout. The operation is regular and the stability is good when the load changes, but in this way the current coming out of the Vref pin is about 40µA. I would like to know what is the maximum current that can be supplied by the Vref pin so as not to compromise its operation. Thank you

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.