Other Parts Discussed in Thread: TINA-TI

Hi,

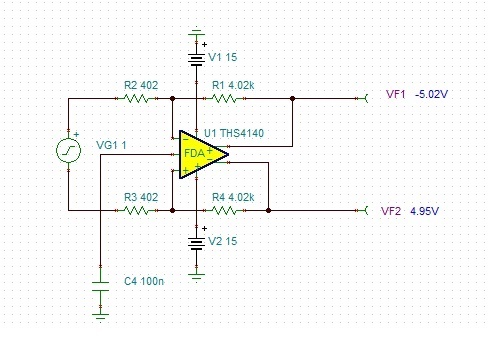

While simulating with TINA circuit with THS4140 for gain = 10, we see that result is not as expected and furthermore, the values of the positive and negative terminals not symmetric.

Rf and Rg are as recommended by datasheet.

As shown in diagram, for the 1V input, the gain is 9.97 instead of 10, and output differential terminals are 50 and 20 mV off (and not symmetrical).

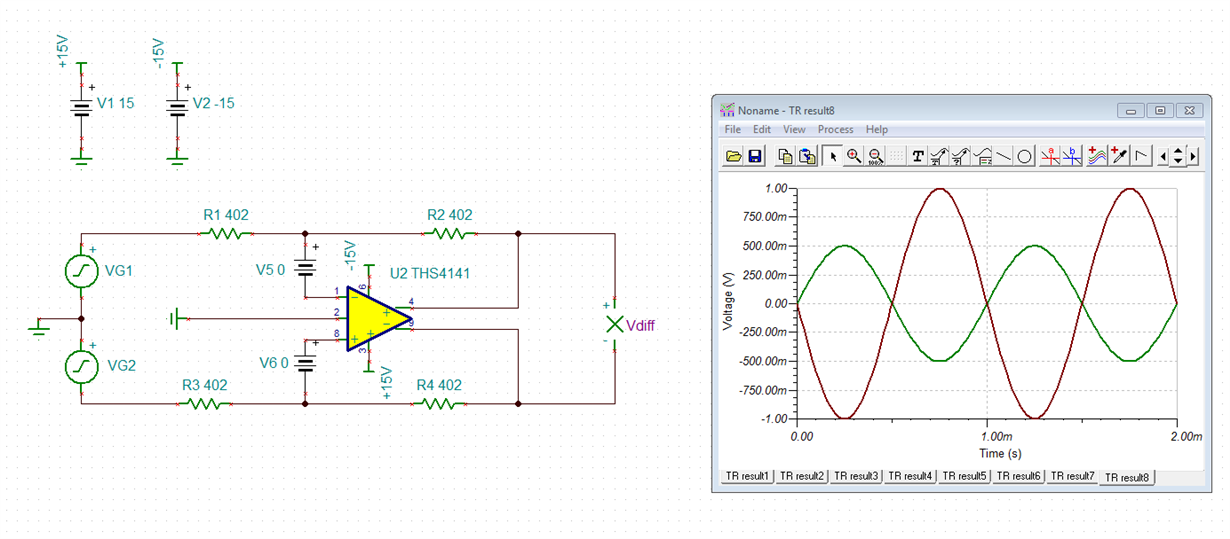

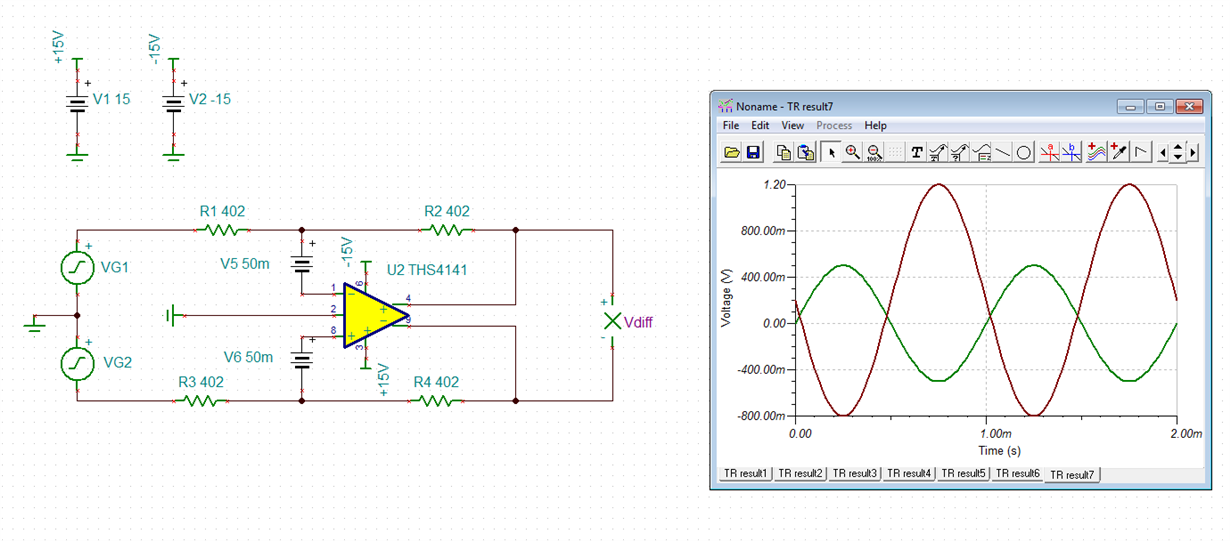

Assumption was that we should be able to see gain = 10, as per recommendations, and symmetrical differential output, in the simulation.

Is the problem in the simulation environment or does it reflect "accurate" device behavior? (can we rely on simulation results in this case?)

Thanks,

Arie