Other Parts Discussed in Thread: ADS5294, THS4541, THS4551

Hi,

I am experiencing stability issue with the THS4520.

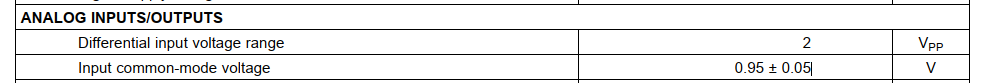

I use it as to drive an ADC (ADS5294) with a gain of 0.95, and some filtering across the feedback resistor (see attached file).

If I remove C9 and C10, the circuit is stable. Howewer, if I add them, which is what I need, the circuit oscillates, and it oscillates even more if I heat up the amp. I don't understand what is happening, because I thought these capacitors were suppose to help stabilize the op amp. Do you have an idea of what can cause this oscillation ?

I also simulated the circuit phase margin, and it was very stable, both with and without the caps: I have 50 degree phase margin without the caps, and 70 degree with the caps.

I followed TI instructions for the simulation: https://www.youtube.com/watch?v=-cWYHAHhBmM

I am attaching the simulation file, can you please tell me if the simulation is correct?