Other Parts Discussed in Thread: VCA810, VCA820, VCA2612

Hello,

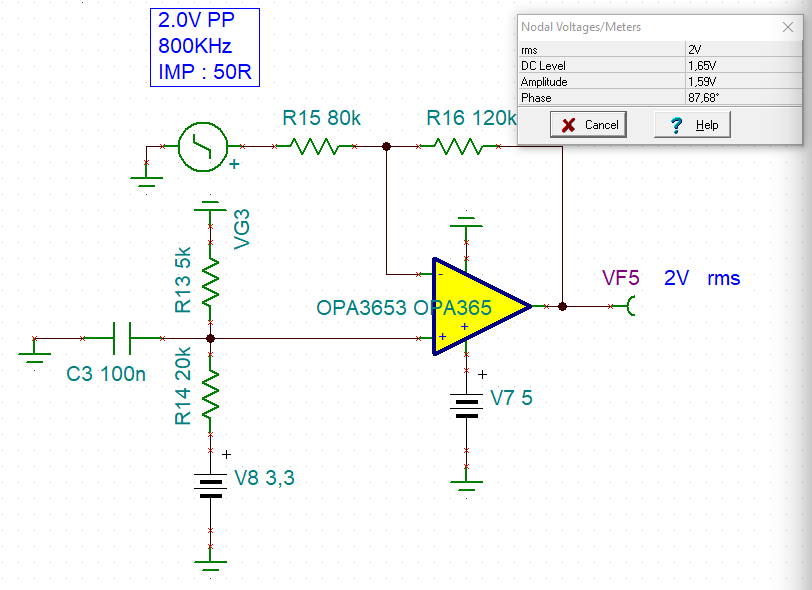

As a follow up to previous quoestion, i am using an OPA365 to drive the ADC of an STM32F411CEU6 (12bit, single end)from the output of a tuner providing an IF which is between ±640KHz and 800KHz.

Currently there is a 4:1 balanced-unbalanced impedance transformer at the tuner output (which is differential, with a max amplitude of 2.0V PP).

The OPA365 is used to offset by 1.65V and provide the gain to reach (close to) full scale of the ADC. This setup is working but there is a number of problems and it is probably suboptimal, first of course the output is not exactly rail to rail, which mean some codes are lost at the bottom of the ADC range, however it is not the most major issue, a more conerning problem is that the OPA is prone to saturation and as soon as the tuner VGA gain is too high it will saturate by "folding" on top and clipping at bottom. Screenshot attached.

The major problem i have is that the digital processing chain behind the ADC can only compensate for a loss of 3bits in resolution, so as soon as the absolute value out of the adc is less then ±512 it will not demodulate correctly, i already set the tuner LNA and VGA gain to highest settings, and the tuner AGC is also enabled.

This lead me to the question :

-Is there a better way to do what is currently done by the combo impedance transformer + OPA365?

-Is there a way to either add a control loop to the OPA365 or add another OPA after it to act as an AGC? i would like to keep feeding the ADC and the processing chain within it ideal range (that is over 9bit resolution), as long as possible( until the SNR is too low anyway).

Thanks.