Other Parts Discussed in Thread: ADS131E08, OPA627, OPA191, OPA378, OPA2210, OPA192, LM7705

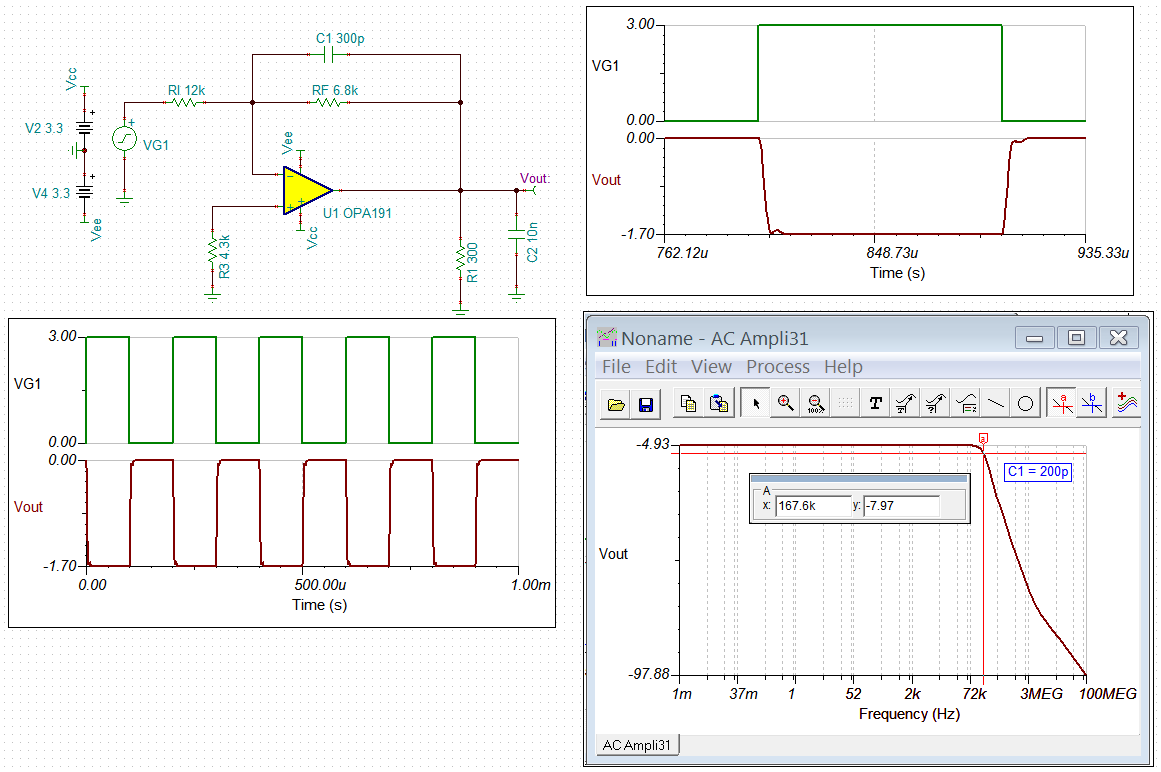

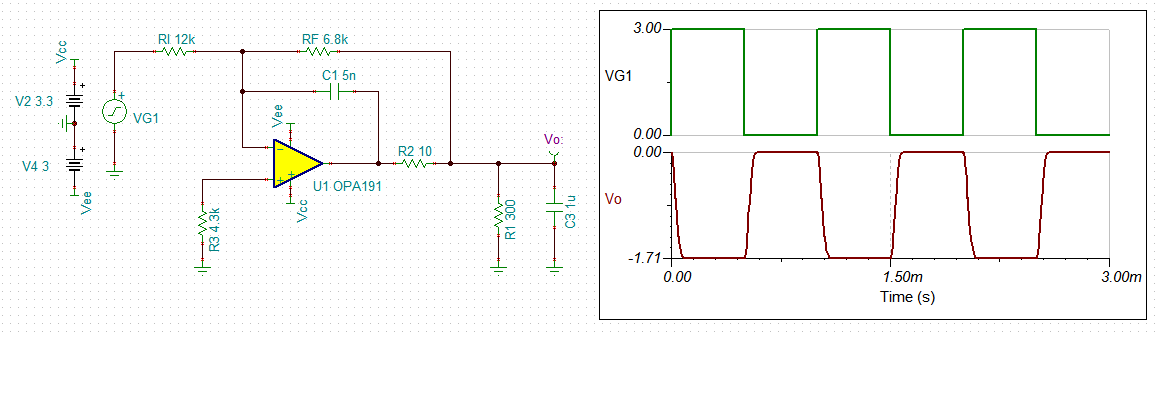

I have a precision (0.04%) 3V reference and need to create a precision -1.7V rail from it. Note, this is for AVSS of the TI ADS131E08 ADC. I've decided to use an inverting opamp with precision resistors in the feedback. My issue is that I would really like to have decoupling caps, 0.1uF, on the AVSS pins. I'm thinking about using the OPA189. However, there is a curve showing overshoot with load capacitance. I know opamps can have issues driving capacitive loads. I'm not using the amplifier to drive "signals" but rather a DC conversion. Do I have to worry about this overshoot curve? I can't add series resistor prior to the decoupling because I can't handle any voltage drop on the -1.7V rail. Any other suggestions? Are there opamps that don't have capacitive load restrictions? Thanks!