Hello!

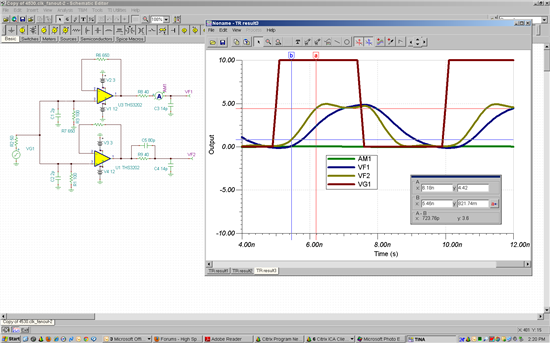

We have one high speed clock source upto 200MHZ. Our plan is to fan out single CLOCK to 2 with high speed analog opamps.

The clock distribution devices are ruled as we need the clk oputput to follow the levels of the input hence the need for OPAMPS. Can you please reccomend some high speed OPAMPS that I can use to fan out my one 200MHZ clock to 2?

The levels we are looking at is 0V-5V.

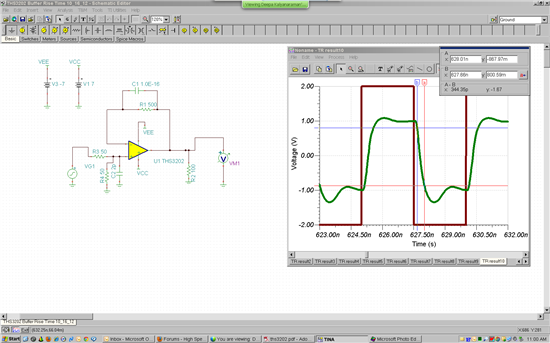

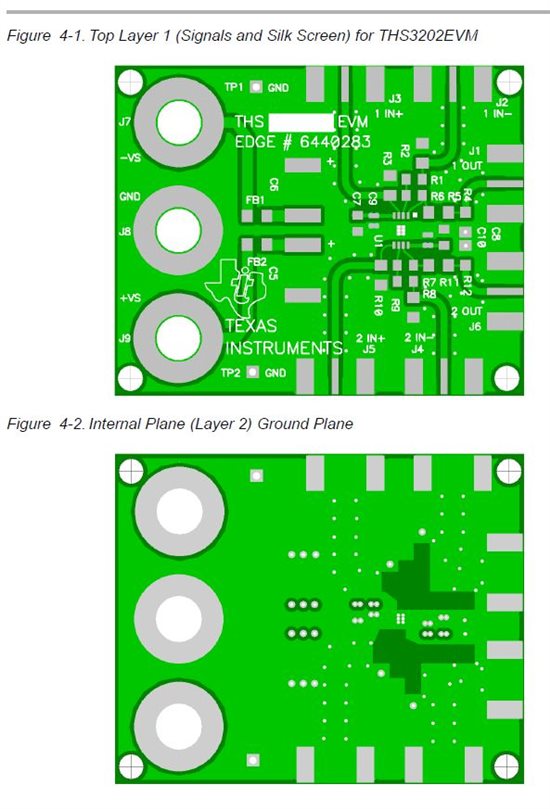

I have mocked up some simulation models using TH3202 with +/-7.5V supply and for 200MHZ clock input at the output I observe a rise time of 1nS.... (assuming no parasitics) with input parasitics of 2pF the signal integrity is lost with high rise time.

Arjun