Hi,

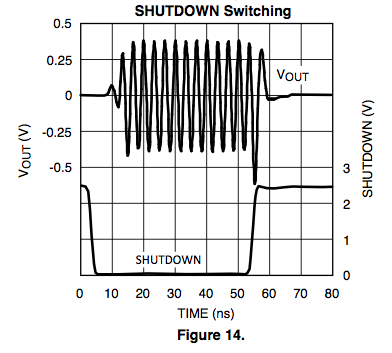

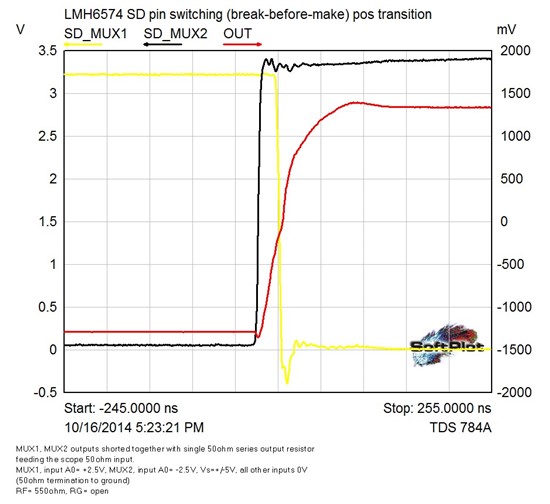

I am using LMH6574 high-speed video mux in mux expansion mode. I use the shutdown line (SD) to select the mux chips. When I disable mux1 and enable mux2, I see a long (~500ns) exponential settling to the desired output voltage. Details follow.

Inputs to the mux

To test the mux, I feed DC voltages separated by 0.1V into the mux inputs. So the inputs to Mux1 are: 0.1, 0.2, 0.3, 0.4V, and the inputs to Mux2 are 0.5, 0.6, 0.7, 0.8V. These voltages come from a AA battery driving a resistive divider (16x 10 ohm resistors in series). At present, Mux3 and Mux4 are de-powered (they are disconnected from the supply voltages).

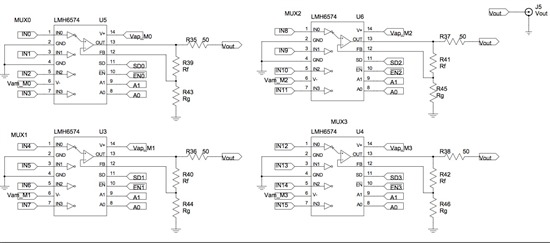

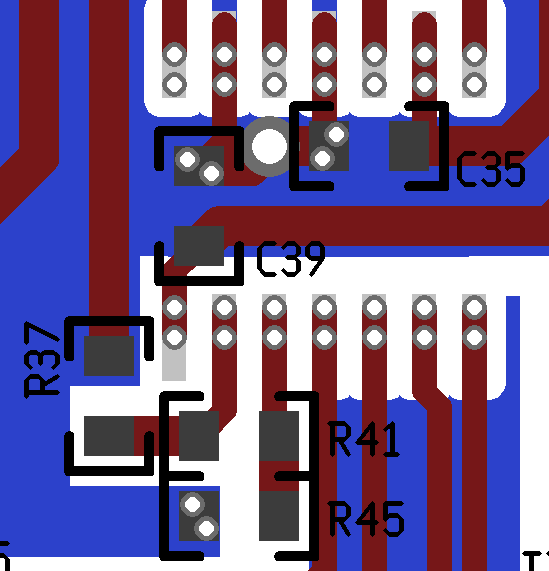

About the board, and project goals

The circuit is implemented as surface mount on a pcb, with 4 mux chips forming a 16:1 mux. I select the mux chips by using the shutdown (SD) line. I do not use the ~EN line. The mux output will eventually be digitized by a 12-bit ADC. Signals of interest are 0-2V, so bit noise is ~0.5 mV. Short-term goal is to digitize at 16MHz (to get 1 MHz sampling of each of the 16 mux input lines), with long-term goal of 32MHz digitization of a 32:1 mux. So I want settling times of <60ns, with <30ns as the long-term goal.

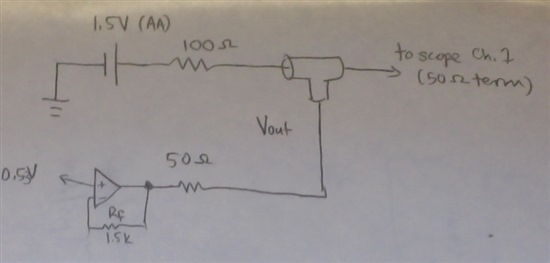

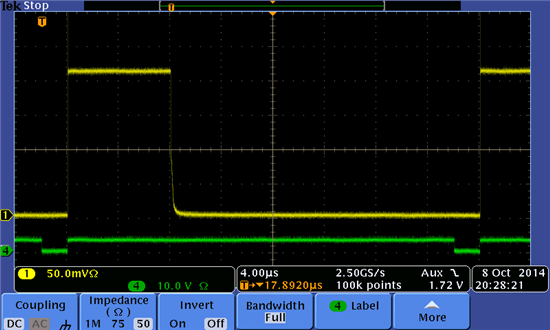

The mux gain is set to ~unity (as suggested in Fig. 29 of LMH6574 datasheet, I use: Rf = 1.5k and Rg is omitted, not accounting for loading by inactive muxes for now). The mux outputs are series-terminated in 50 ohms, and then read by a coax connected to the scope with 50-ohm termination (see Schematic below). So there is a 2:1 attenuation between mux input and scope measurement (measured Vout values are 0.05, 0.1, 0.15, 0.2V when mux1 is active, and 0.25, 0.3, 0.35, 0.4V when mux2 is active).

The problem

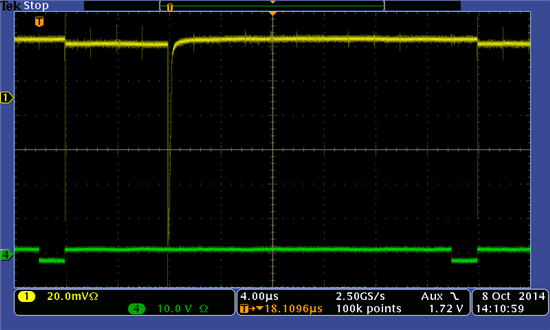

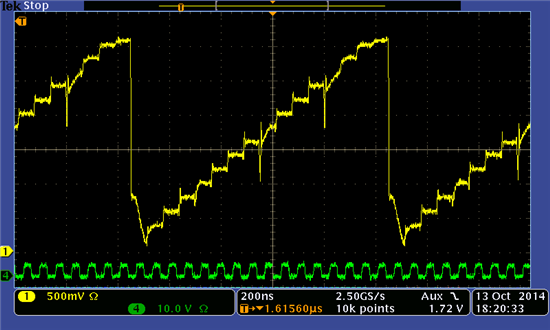

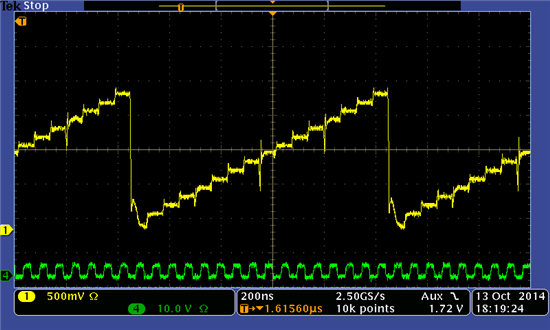

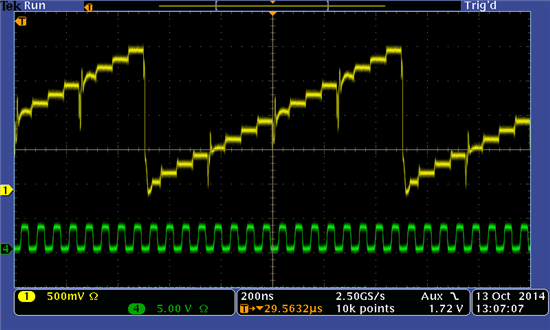

With two muxes powered, Vout shows a long (~500ns) exponential ramp following the transition from the first chip to the second (see Figure 1 below). No such ramp is seen on address changes within a chip, or at the selection of the first chip.

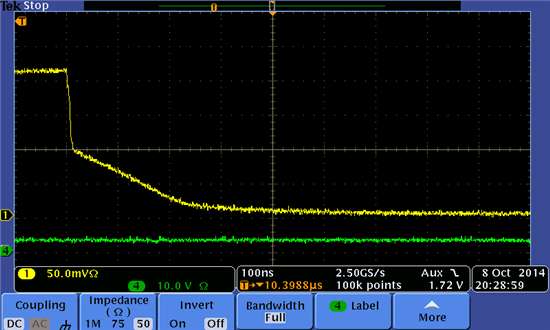

I have probed various places on the board, and do not see this waveform structure on the analog or digital grounds, or on the addressing lines (A0, A1), or on the SD line, or at the mux inputs. But I do see it on the output of the inactive mux (in this case Mux1) -- See Figure 2 below.

It appears that the inactive mux is driving Vout. I don't understand why that would be. Any help greatly appreciated.

Many thanks,

James

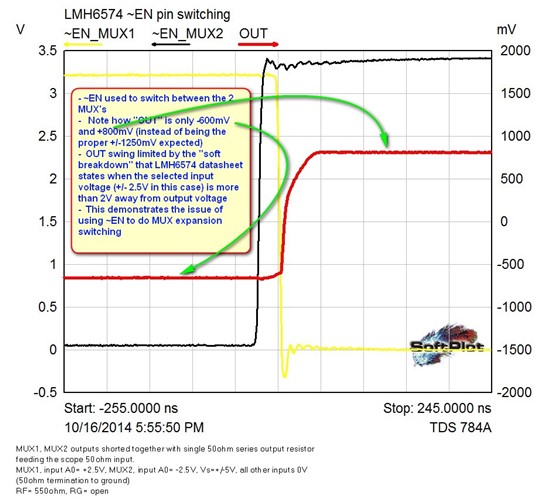

ps: I know from the data sheet that SD (not ~EN) should be used for mux expansion to prevent soft breakdown (when voltage between mux input and output exceed 2V). So I don't think soft-breakdown is to blame here since (1) as recommended I'm using SD (not ~EN), and (2) there is << 2 V between Vout and unused mux input (and we only see this exponential ramp immediately after the SD transition.

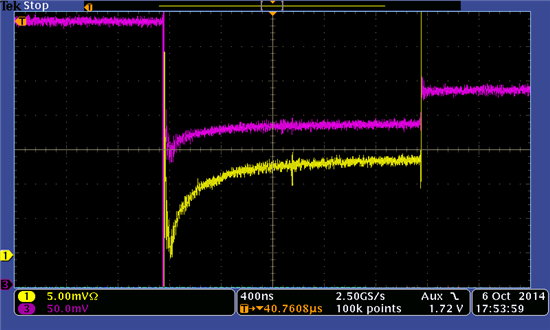

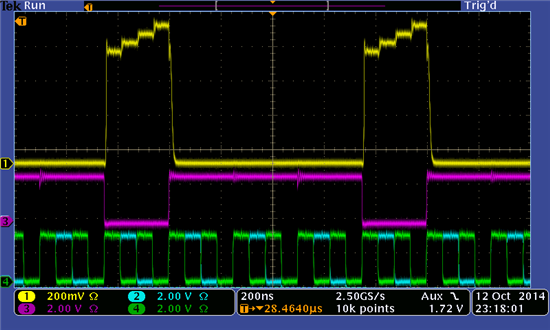

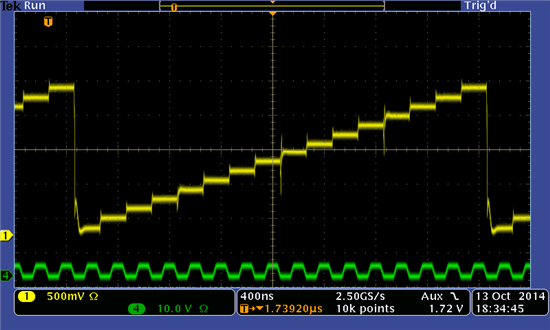

Figure 1

Yellow = Vout of mux pair, after the 50-ohm series termination of both mux chips. Notice exponential settling at the 5th step (the first step of Mux2). The Vout signal is transported from pcb to scope via 50-ohm BNC cable. Scope is terminated in 50 Ohms.

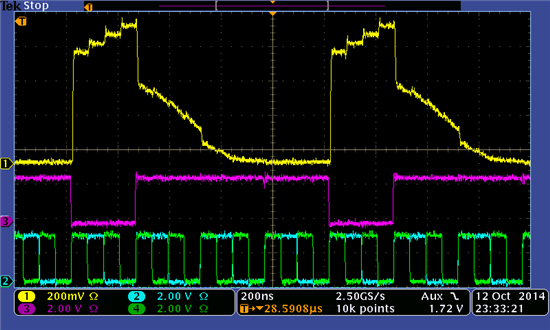

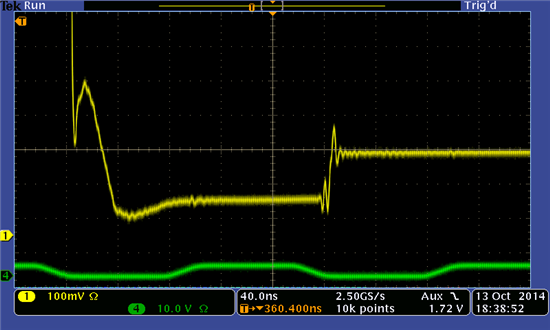

Figure 2

Yellow = Vout of mux (after 50 ohm series termination) seen via coax to scope terminated in 50 ohms.

Pink = output of the disabled mux (mux1, pin 13), probed between the mux and 50ohm series termination.

Mux Schematic: