Hi Team,

Please advise me proposing a solution for a HD Video A/D conversion.

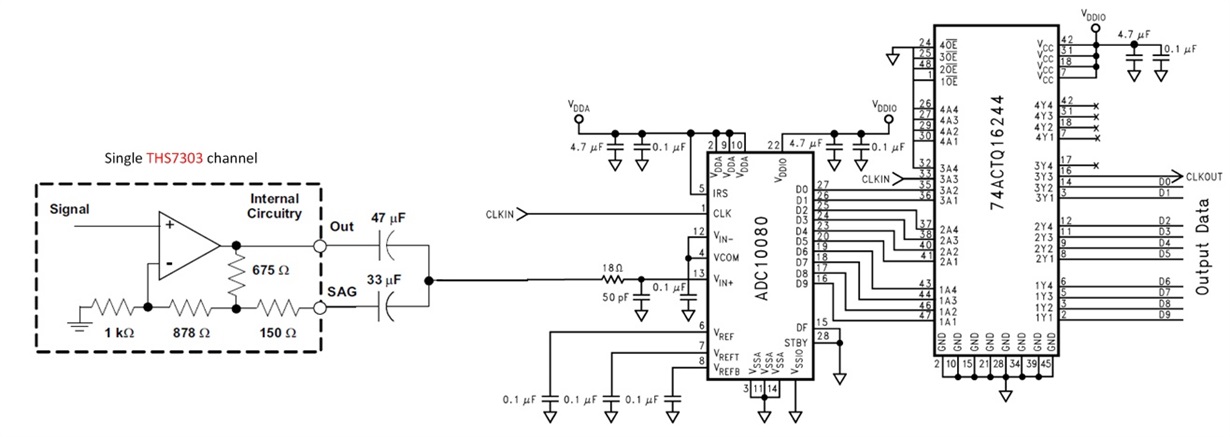

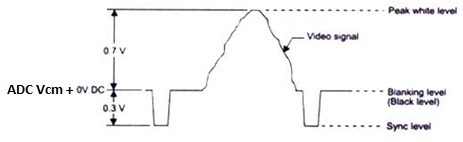

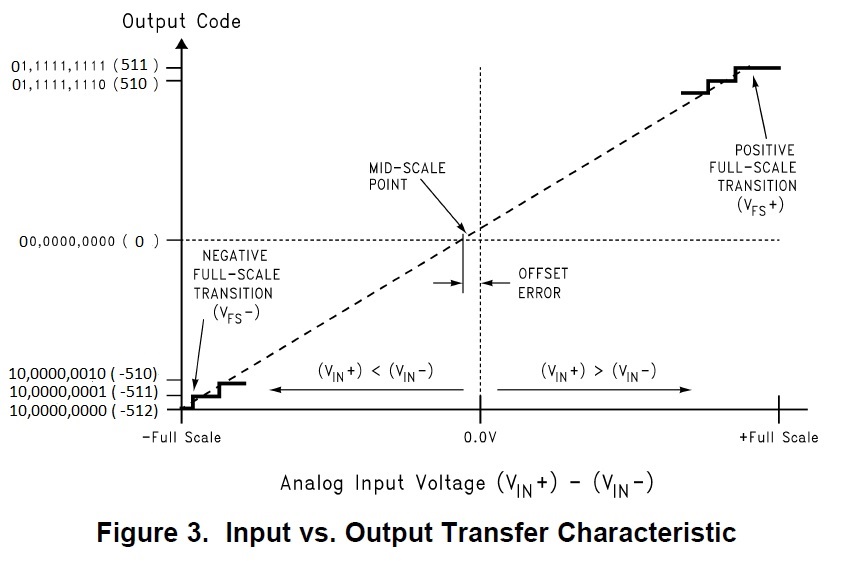

In order to fully utilize the ADC10080 dynamic range, it is necessary to make coincide pedestal level (Back porch level) of the HD analog video Y input to VrefB of ADC10080, and Pb, Pr to VCom of ADC10080 respectively.

Can you provide us an example schematic which implement this request?

I think THS7353 has on-chip DC-Restore circuit. I am wondering if this can be used to implement this function.

Best Regards,

Kawai