Hello all,

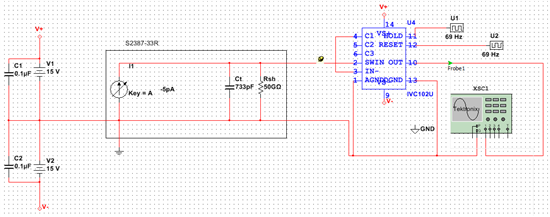

I am working in a photodetector amplifier design in order to measure currents from around 1pA to 10pA. I want to use the IVC102U as a good solution to improve the SNR.

I am simulating using the multisim models. I checked and the PSpice model is exactly the same that you provide in the webpage.

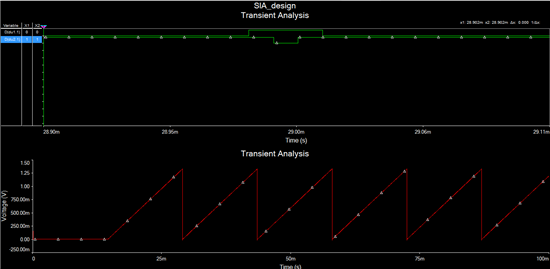

I decided to use the SWITCHED-INPUT MEASUREMENT TECNIQUE as described in the datasheet. The results look correct a priori. However, I am using a variable DC current in the input and the output is completely independent of that value. It is always a positive-ramp at Vo!!!!

I've tried different configurations, components. Thus, I am wondering if I am missunderstanding something, if the model in Multisim is incorrect or if this configuration is not suitable for this application.

PS. I attach the schematic and output plots!!!