Other Parts Discussed in Thread: OP07

Hi,

one of my customer is testing TLV07 to measure the DC bus current in the boost stage of the solar inverter system.

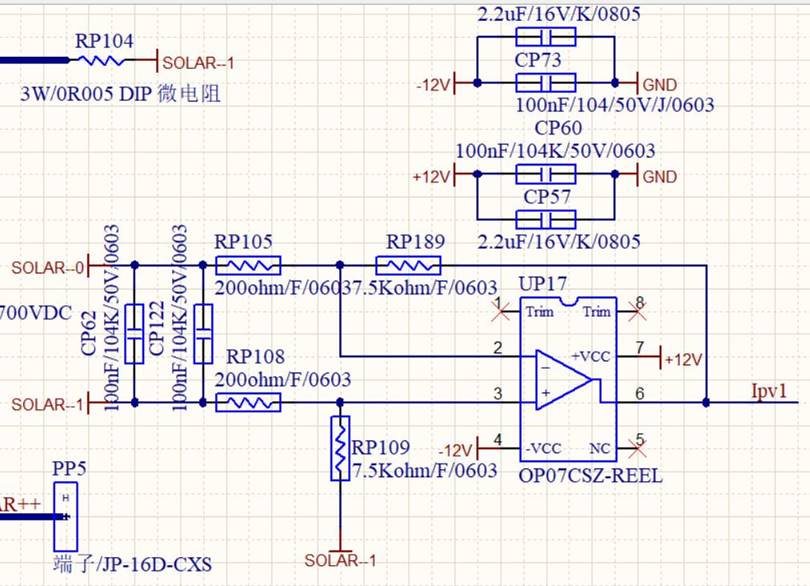

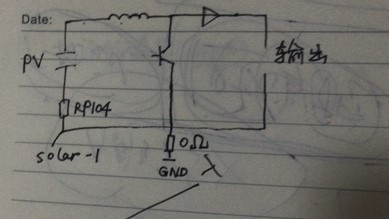

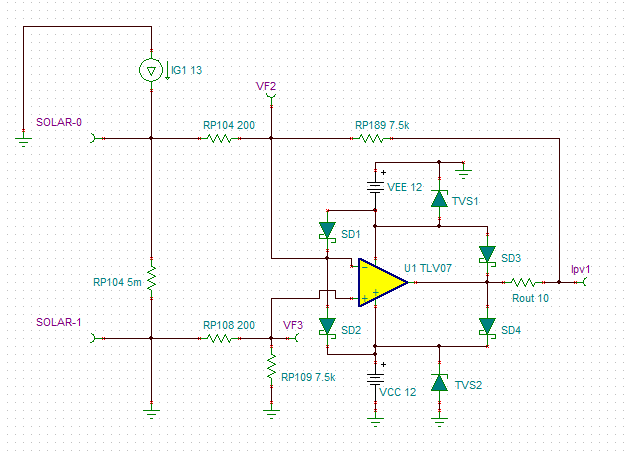

The schematic is as below. Ipv1 is connected to TL074. TL074 forms a voltage follower, and the TL074's output is connected to the ADC pin of C2000.

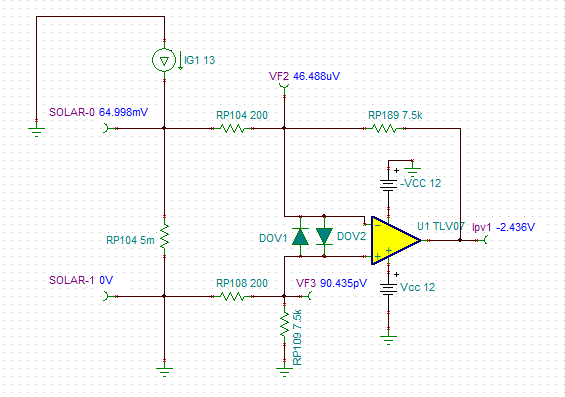

It can work well during normal temperature.

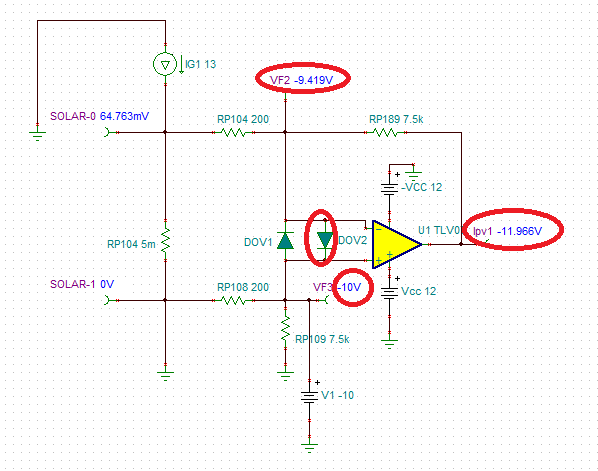

But at 70-80C, Ipv1 will be -12V, TLV07 pin 2 voltage is 0V, pin 3 voltage is -10V.

At this time the boost will be turned down and their should be no current flowing through the shunt resistor RP104.

After cooling down the board, this phenomenon still exists.

After power cycle, the phenomenon disappear.

The failure rate is 4.1%.

Could you please provide any idea?