Hi all,

We have a design using a TMS570LS3137 processor with a TPS65381-Q1 PSU chip.

The design is working, but there is audible noise from the PSU circuitry, which gets louder with increased load.

Investigation of the SDN6 switching waveform shows an extra pulse which we can't explain.

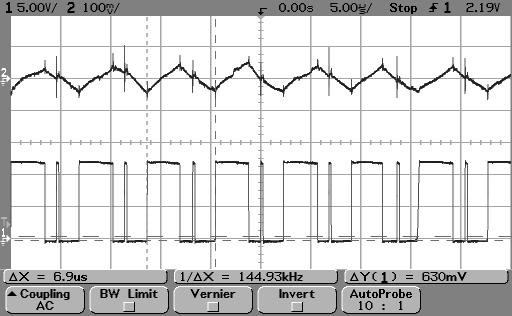

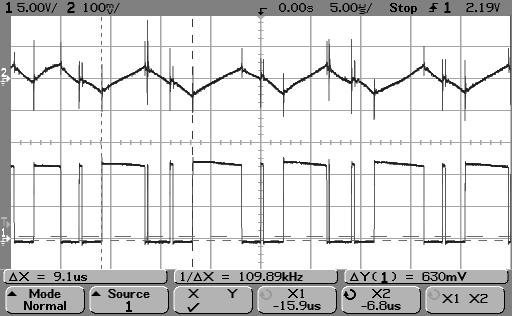

These traces were captured under the following conditions: VBat = 12V, load applied directly to VDD6 using load box, processor held in reset. Channel 1 shows the ripple on VDD6, channel 2 shows the switching of SDN6.

With 100mA load on VDD6:

With 1A load on VDD6:

With 12V in and 6V out, the duty cycle should be 50%, which it is, apart from that extra pulse in the middle of each off period.

I found similar graphs in two other threads on these forums, here and here, but neither of them actually addressed the issue.

is anybody able to explain why that extra pulse is there, and what we need to do to remove it?

Regards,

Graeme