Hi,

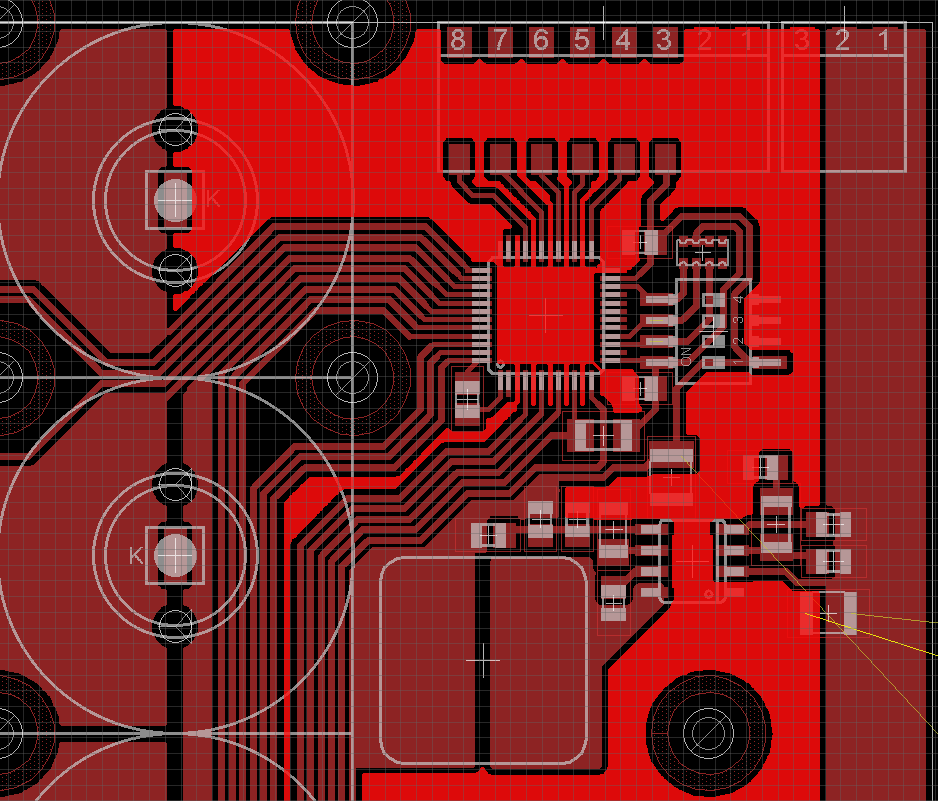

On the TPS92661 package there are GND pin between each control io pin.

On the EVM each gnd pin is routed to an external connector

Can i route control IO pin without GND between them ?

(i assume that gnd pin is for thermal consideration)

(My board was a mcpcb mounting on heatsink)

Tanks