Hi Support,

Let me raise a few questions about SM320F28335-EP.

1.

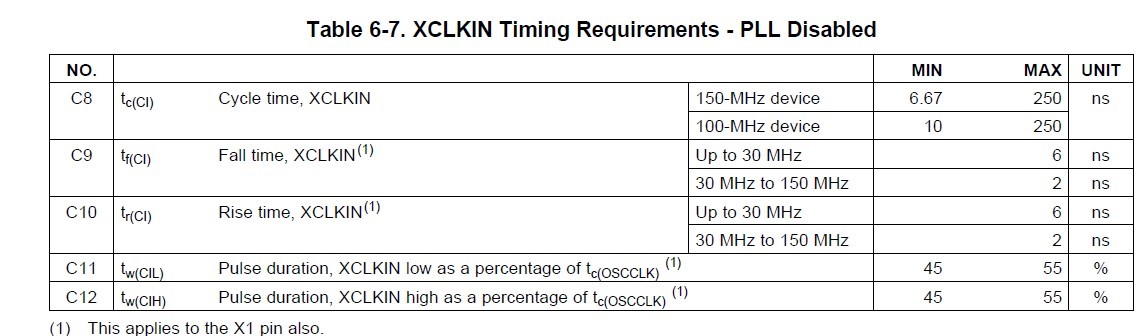

The DSP device accepts input clock from an external oscillator via XCLKIN pin.

May ask you if the external clock runs through a signal conditioning circuit even when PLL bypass mode is selected?

2.

I can’t seem to locate worst case values for internal pulls on numerous pins, a good example being boot mode selection pins XA15- XA12. Need to calculate values of external pull-down resistors opposing internal pull-ups as no recommendation was found.

3. I can’t seem to find a package drawing for PTP version. The following link does not seem to help.

http://www.ti.com/product/TMS320F28335/datasheet/mechanical-packaging-and-orderable-information?keyMatch=package drawing delfino&tisearch=Search-EN-Everything

Do you think you could send a hint?

Many thanks in advance,

regards,

Alberto