Other Parts Discussed in Thread: SN74LV595A, SN74HC595B

Hi,

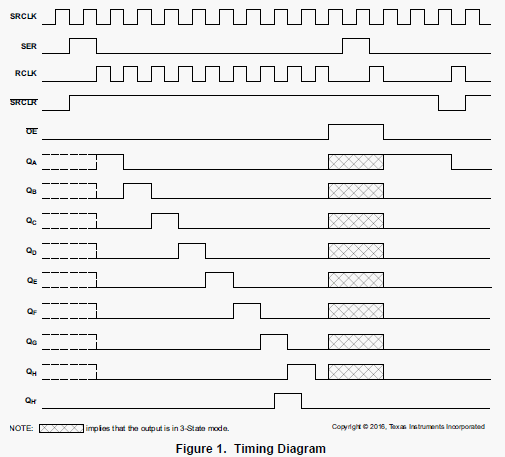

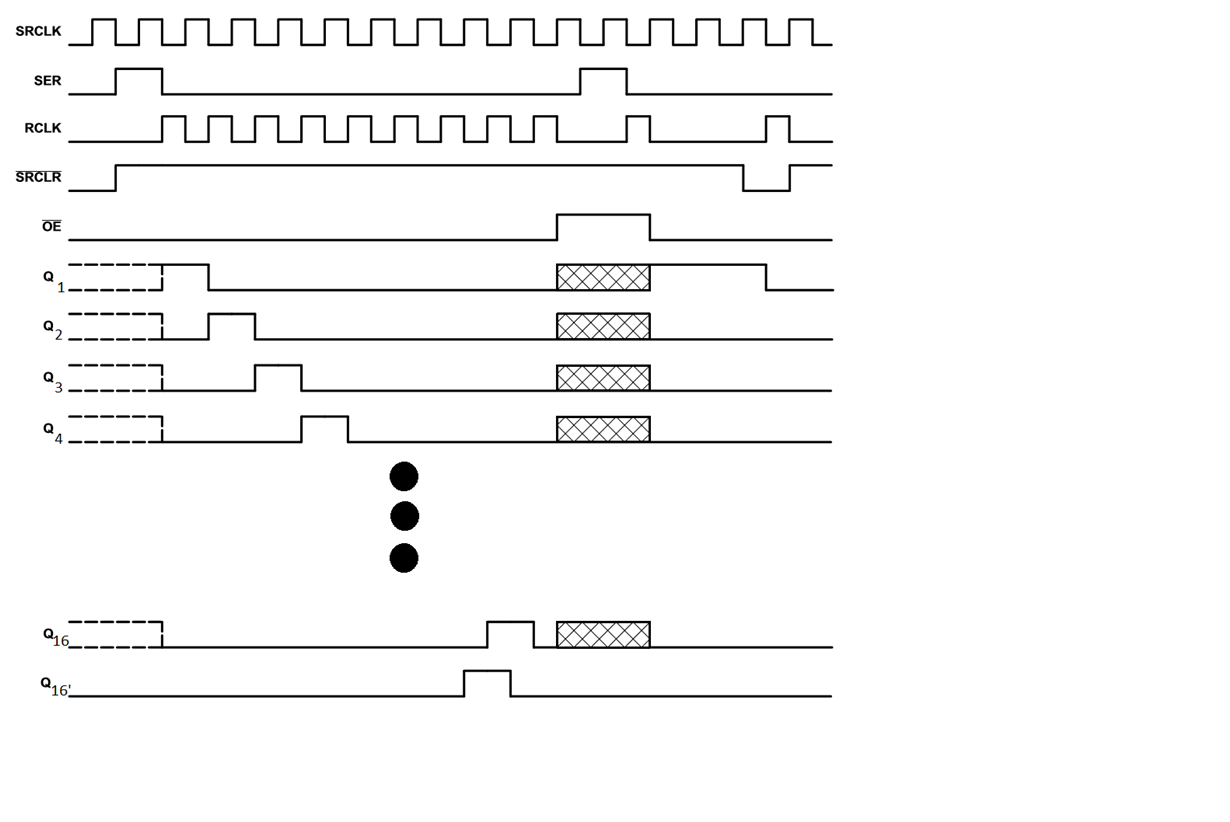

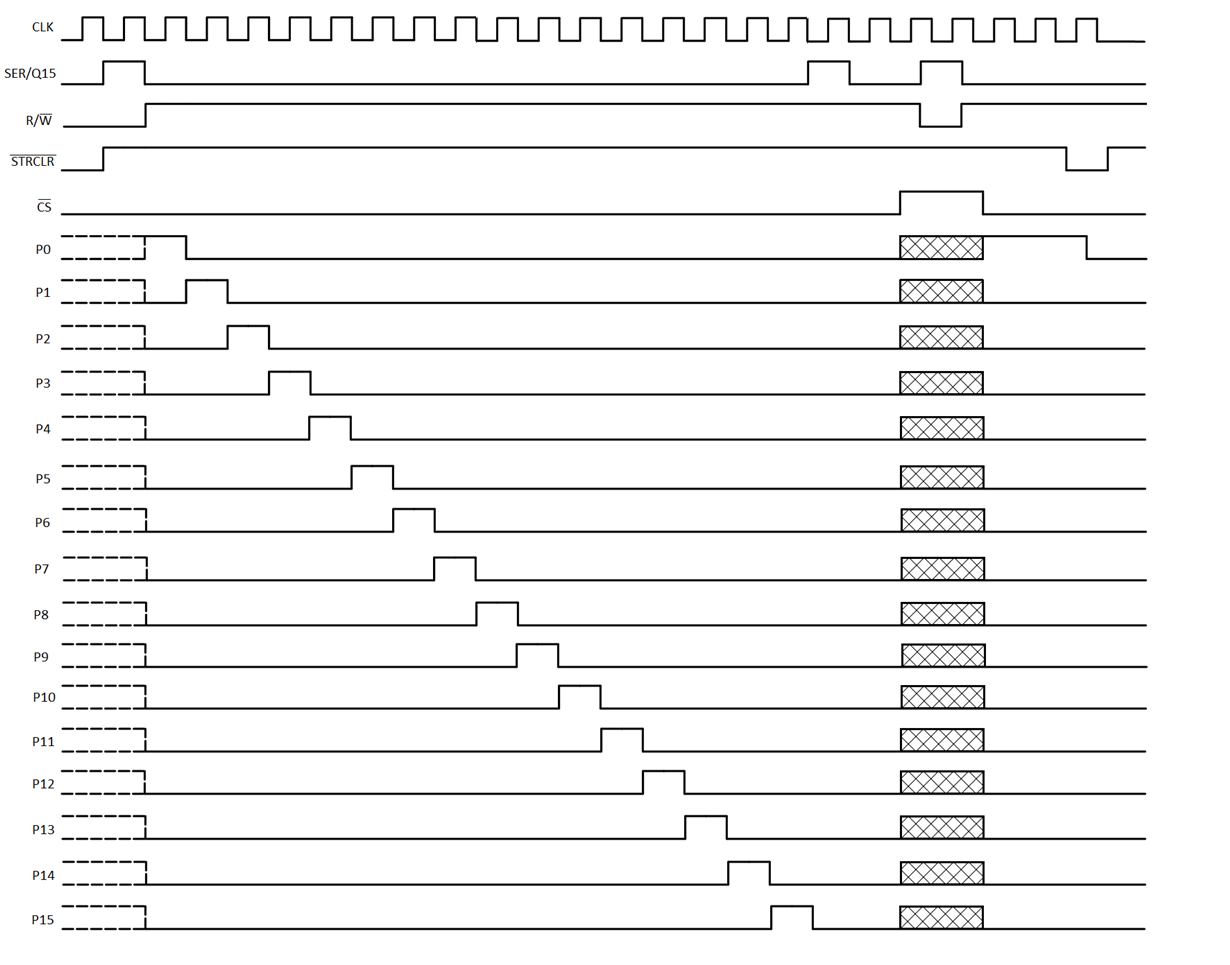

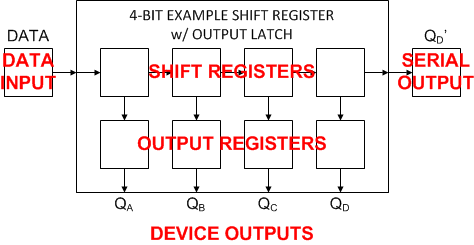

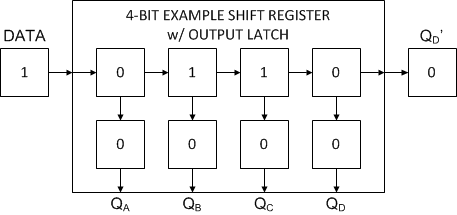

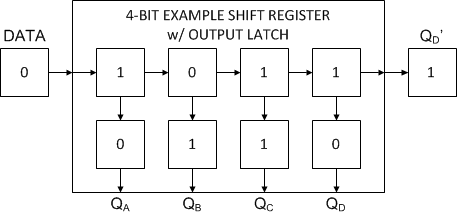

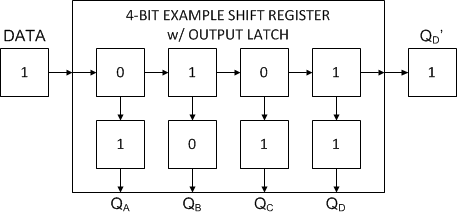

Do we have a timing diagram of SN54LS673 as we have for SN74LV595A as below? Customer needs a similar part as SN74LV595A, but the shift needs to be 16-bit. Is SN54LS673 a correct fit? THanks!

Antony