Other Parts Discussed in Thread: TMS570LS3137

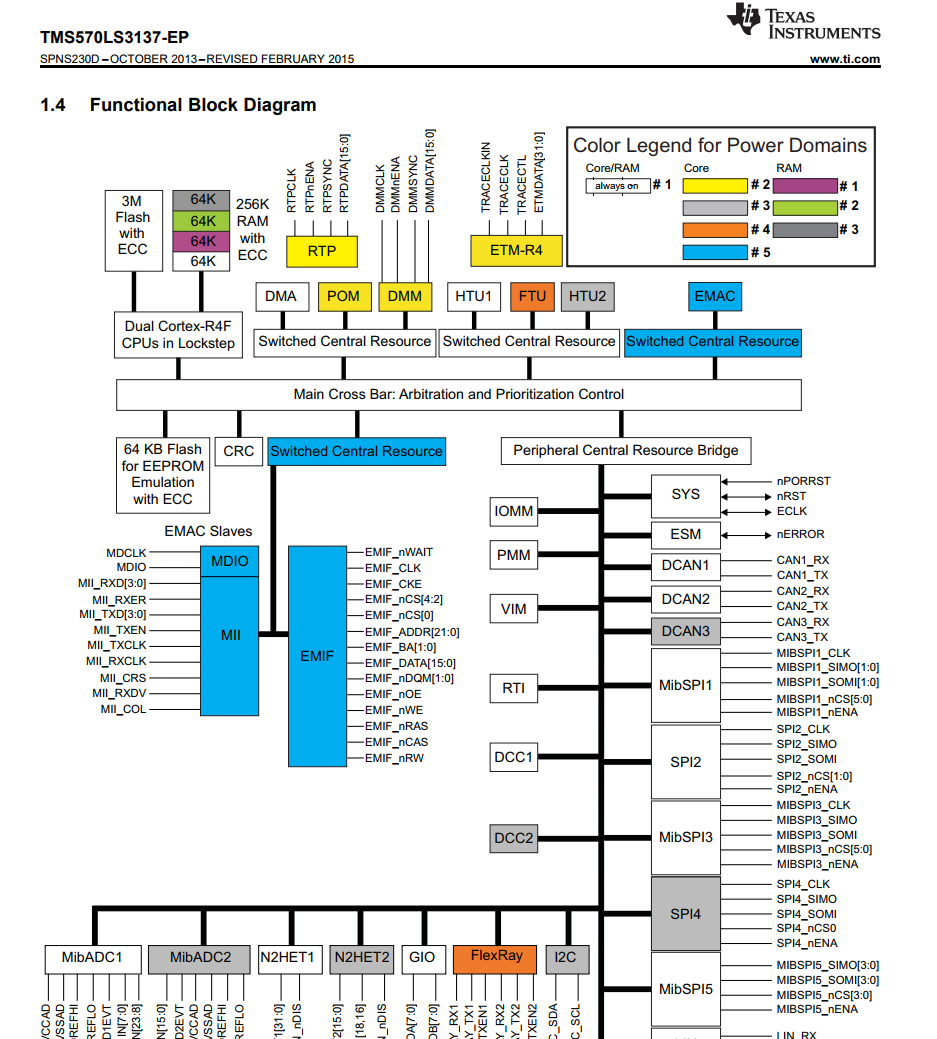

I would like to use the TMS570LS3137 in a flight control computer, and my question is about the bus labeled "Main Cross Bar: Arbitration and Prioritization Control" in the functional block diagram of the datasheet, and the bus/data lines that go through it: does it contain error checking on every data transfer?

My problem is that I need to be able to guarantee that in the event of a hardware failure (transistor burns out due to cosmic rays or similar), the system that will incorporate these processors will not actuate the flight control system's control surfaces. If a processor had a hardware fault, it would be detected by the dual cores operating in lockstep being unable to resolve the difference in outputs, or if the memory failed the ECC should catch that, but what about data transfers between them? If bit 9 of that bus burned out for some reason, is the hardware capable of detecting that an incorrect data transmission occurred across the interface?