Other Parts Discussed in Thread: ADC08D1520

Hello,

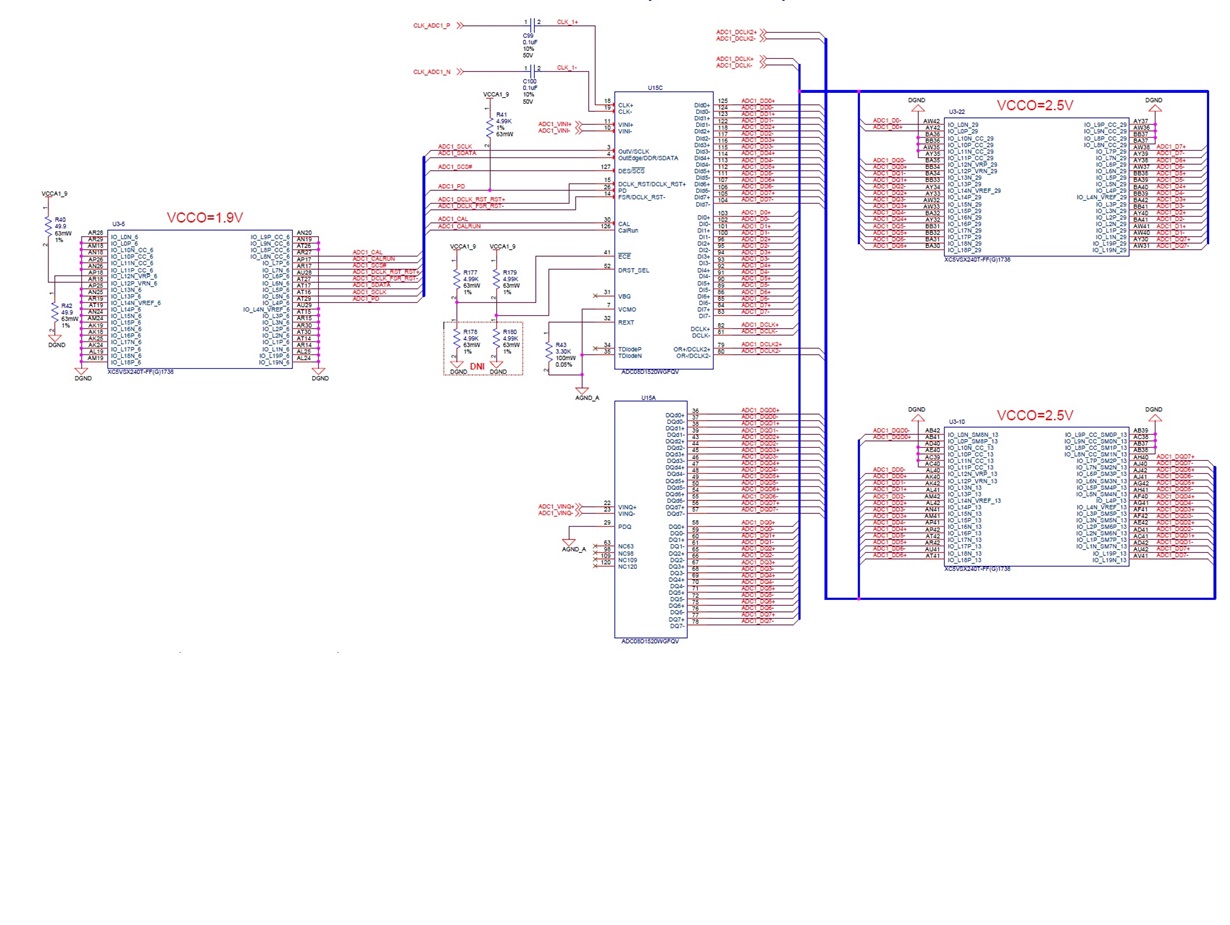

We are trying to use ADC08D1520 in dual channel mode and attached is the schematics for the ADC interface. We would like to sample the data at 250 Msps/channel. Right now, we are feeding in 250MHz clock as input clock to the ADC (CLK+/-). Is it right input frequency ? What would be output clock frequency from ADC (DCLK+/-, DCLK2+/-) ?

Following is our configuration sequence:

x"001" & x"1" & x"92FF"; --Header & Reg Address & Reg Data(ConfigReg)

x"001" & x"9" & x"27FF"; --Header & Reg Address & Reg Data(ExtConfigReg)

x"001" & x"2" & x"007F"; --Header & Reg Address & Reg Data(IoffsetReg)

x"001" & x"A" & x"007F"; --Header & Reg Address & Reg Data(QoffsetReg)

x"001" & x"3" & x"F07F"; --Header & Reg Address & Reg Data(IfullscaleReg)

x"001" & x"B" & x"F07F"; --Header & Reg Address & Reg Data(QfullscaleReg)

x"001" & x"0" & x"FFFF"; --Header & Reg Address & Reg Data(CalibReg)

Can you please help us with the configuration sequence for the above mentioned datarate?

Please let us know if you have any questions or concerns.

Thanks in advance

MK