Hi,

I would like you to confirm about below.

* According to datasheet, there is following figure.

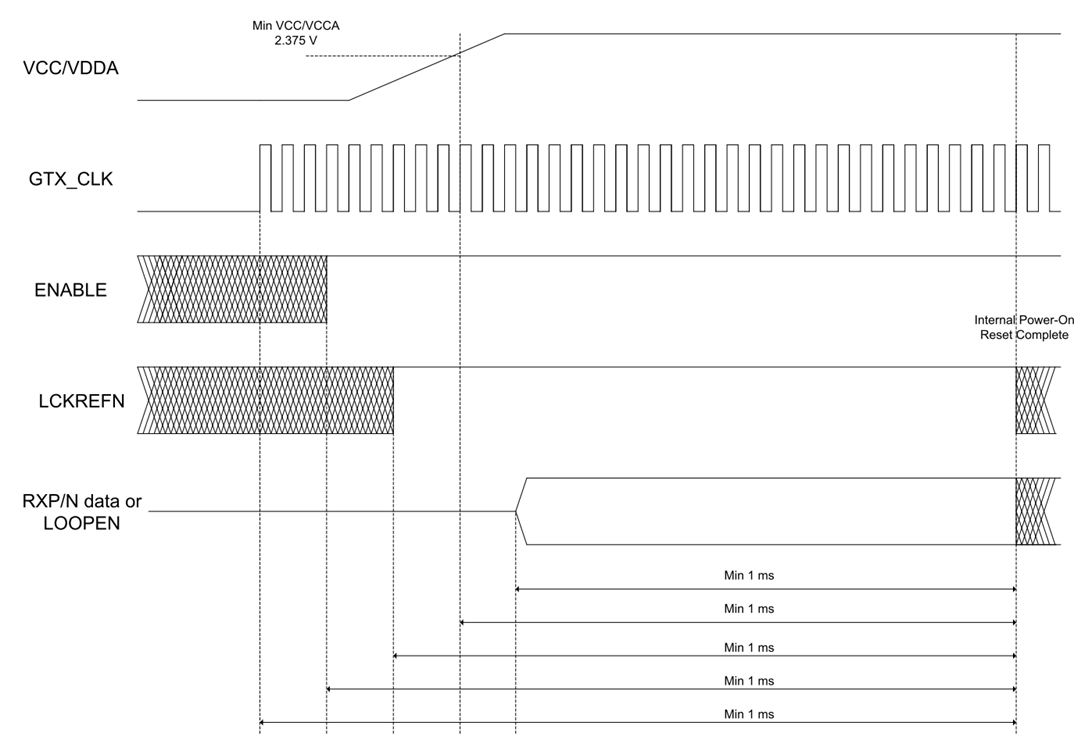

Figure 12. Power-On/Reset Timing Diagram

According to this figure, GTX_CLK should be ramp up first, and after that "ENABLE, LCKREFN" should be ramp up.

Finally, Power should be ramp up.

However, there is no description about duration b/w each signals.(Ex Period b/w "GTX_CLK and ENABLE" etc)

The question is

1. Is my understanding about required sequence which is described below correct ?

"GTX_CLK should be ramp up first, and after that "ENABLE, LCKREFN" should be ramp up. Finally, Power should be ramp up."

2. If above sequence is correct, is there any requirement about duration b/w following each signals ?

2-1. GTX_CLK to ENABLE

2-2. ENABLE to LCKREFN (I understood that this is not mandatory.)

2-3. LCKREFN to Vcc/VDDA

Thanks in advance,