Hi everyone,

I am working on 14-bit High Speed Serial LVDS ADC data (DDR) capture using ADS5294 EVM as my ADC and Zynq (ZC-7020) as my FPGA. Let me explain my requirements and problem to you guys.

I have developed hardware and software part I am able to send and receive simple bits pattern form ADC and receive it on my FPGA. Shifted version mostly i.e if I send 11111110000000 I my receive 00111111100000 or any other version of this. But when I send a signal I am not able to receive it correctly neither the shifted nor the correct signal. Like If I send RAMP (generated internally in ADC board) overall shape of received signal is like RAMP but some bits are missed or skipped.

Scheme I have followed to design Hardware for capturing.

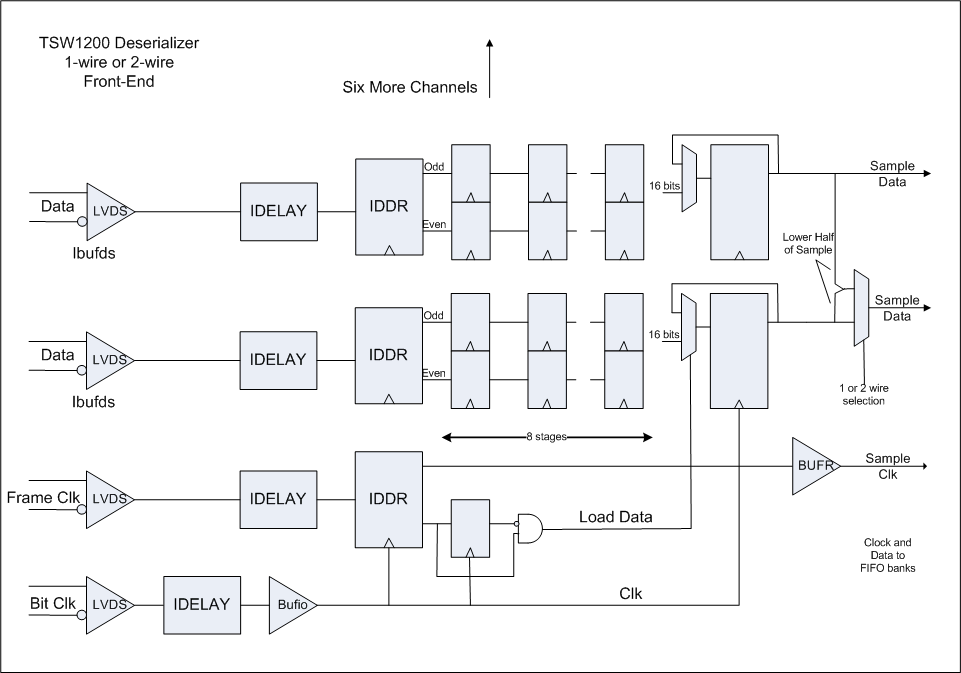

I am following this guide for designing:

I have made the exact figure 3-1. then I have combined DDR output to make a sample of 14 bits.

Now the problems I am facing:

- In this guide on page number 10 Figure 3-1. it is shown that BUFIO should be used after IDELAY to forward Bit clock to IDDR. but when I use BUFIO I receive error during routing. Error: "[DRC 23-20] Rule violation (RTSTAT-1) Unrouted net - 1 net(s) are unrouted. The problem bus(es) and/or net(s) are design_1_i/iddr2_ip_0/inst/cBufferedIO." And Is it necessary to use BUFIO here or not?

- And what can be the problem for not receiving the RAMP correctly.

Regards