Tool/software: Linux

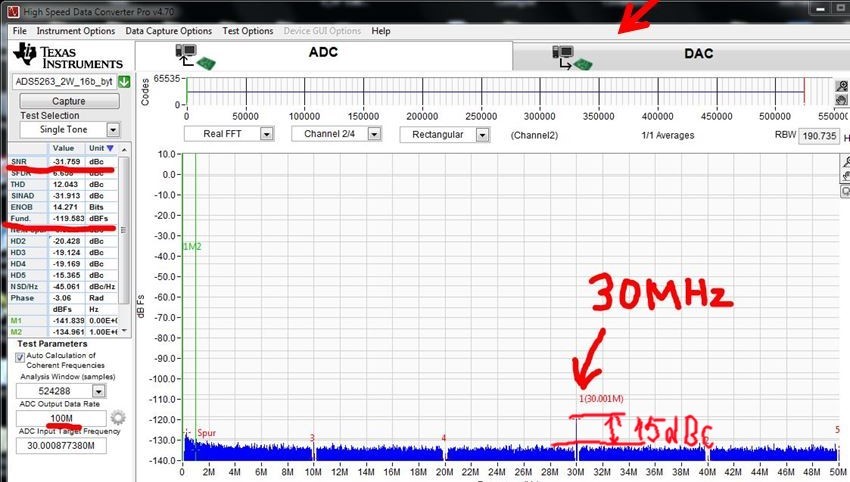

I working with ads5263. In dokumentation i see SNR = 84.1 dBFS for 15 MHz input signal with 100 MSPS clock signal. Teoretically, in BW (bandwidth) = 6 Hz i must have noise floor -137 dBFS. FS = 16 dBm. I analyze the noise floor in the BW = 6 Hz in the absence of an input signal. In may case i have -125 dBF in BW = 6 Hz.

Theoretical calculation: Noise Floor = FS - SNR - 10*Lg(fs:(2*BW)).

where:

FS - full scale signal (for ads5263 FS = 16 dBm);

SNR - signal to noise ratio (for ads5263 SNR = 84.1 dBFS);

BW - the band in which we work (6 Hz);

fs - sampling frequency.

So! The result of theoretical calculation is -137 dBFS.

Real result (result obtained in practice) is -125 dBFS.

Why the result obtained in practice does not coincide with the theory?

Perhaps I misunderstand the documentation or my calculation is incorrect.

Help my please understand these problem.