Hi,

the last days I tried to get a BLDC motor working. The circuit is derived from a former version, which works fine. So there is no generic problem with it. However, I needed to replace the power stage with the compact DRV8312 stage.

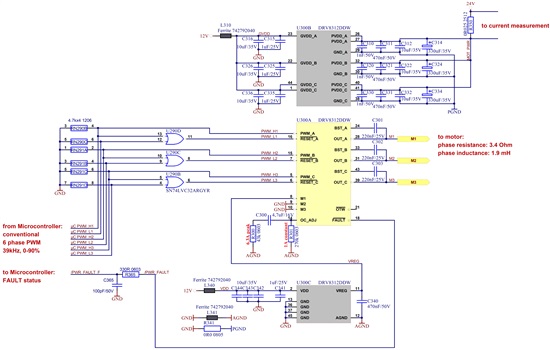

This is, how the stage looks like:

(Please click picture or refer to the attaced PDF for better wiev.)

The motor runs at 24V. So this node powers PVDD_x. There is a cascade of descent decoupling for each phase and the voltage has very low noise. All grounds and supplies are separated in their respective place and connected to system ground an power via 0R resistors and ferrites.

The "or"-solution comes straight from the datasheet. The only strange thing I did is to modify the OC adjustment. I need much power while speeding up the motor. So I set the peak limit to 6.3A (43kOhm). A capacitor limits the time of this peak current. The DC current is set to 1A (270kOhm). As this value is a little high, I also tried 200k.

The motor has a phase resistance of 3.4Ohm and its inductance is 1.9mH per coil.

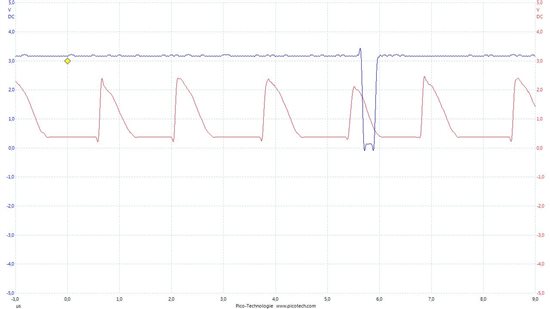

Seems like this circuit could be no problem at all. However, it does not work as expected. Please have a look on the input an output signals:

Please note, that the output was sampled with a 10x probe.

The microcontroller sends perfect signals at 38kHz (90%) to the DVR8312 PWM_A. PWM_B is low and Reset_B is high, so lowside should provide a ground path. However, OUT_A just goes into "Bootstrap Capacitor Under Voltage Protection", I think. The current through the motor is rather low, just a few Milliamps. The voltage at the bootstrap pins peaks up to 33V, which should be perfectly ok.

Anyone out there, who has an idea, what's going wrong here?

Every hint is much appreciated!

Thanks to everyone, having a look on this!

Ralf