Hi Folks,

We are using the DRV110 to drive Solenoid coil.

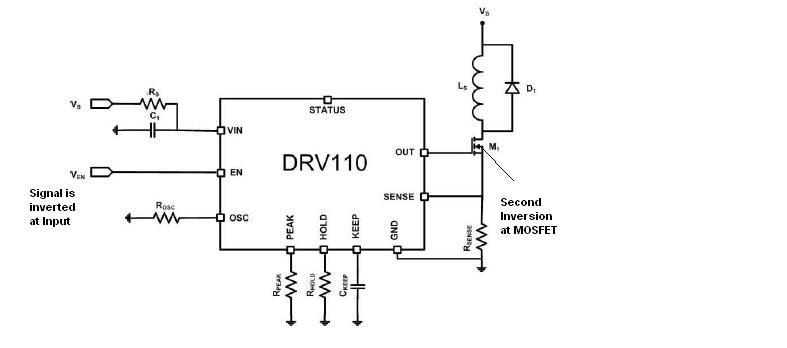

The requirement is that the Input and Output waveforms to be in-phase with each other. In order to achieve that we are inverting the input to DRV110 and other inversion will be there in the MOSFET side. Please refer the below Circuit for reference.

Since we are inverting the Input Signal, the Logic is completely inverted i.e to Drive the Solenoid HIGH, the Input has to be "LOW" and Vice versa.

DRV110 Input and Output are in phase. But we require the Trigger Input and MOSFET Output to be in phase. To achieve that we are inverting the Input Signal. Since we are inverting the Input Trigger Signal, the Logic is completely inverted i.e to Drive the Solenoid HIGH, the Input has to be "LOW" and Vice versa

Please provide us suitable solution to resolve this issue.

Thanks,

Srijan