Dear e2e-community,

I am using the DRV8301-69M-Kit with Motorware version V1.01.00.16. I developed an application based on project lab04. In this application I want to assign three pwm duty cycles manually. For this purpose I write the values

Tabc->value[0] = _IQ(dutyCycle0);

Tabc->value[1] = _IQ(dutyCycle1);

Tabc->value[2] = _IQ(dutyCycle2);

This procedure works fine for a wide range of duty cycles. However, there are scenarios when it does not work as intended. Let me explain one scenario:

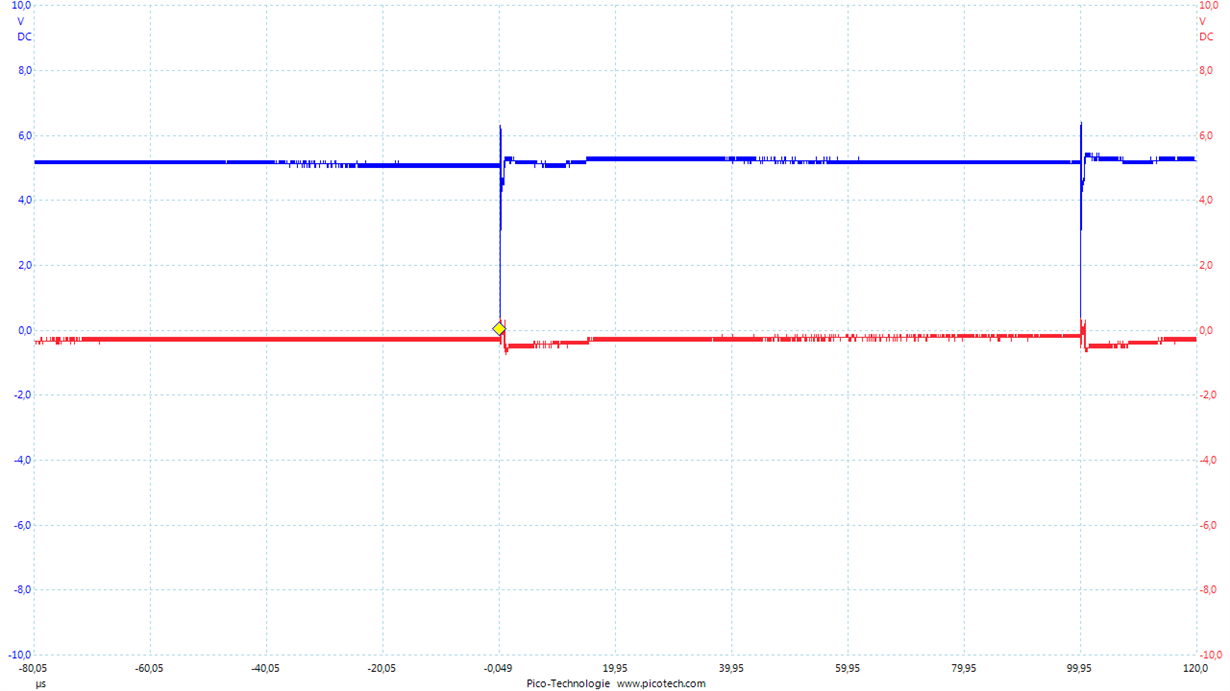

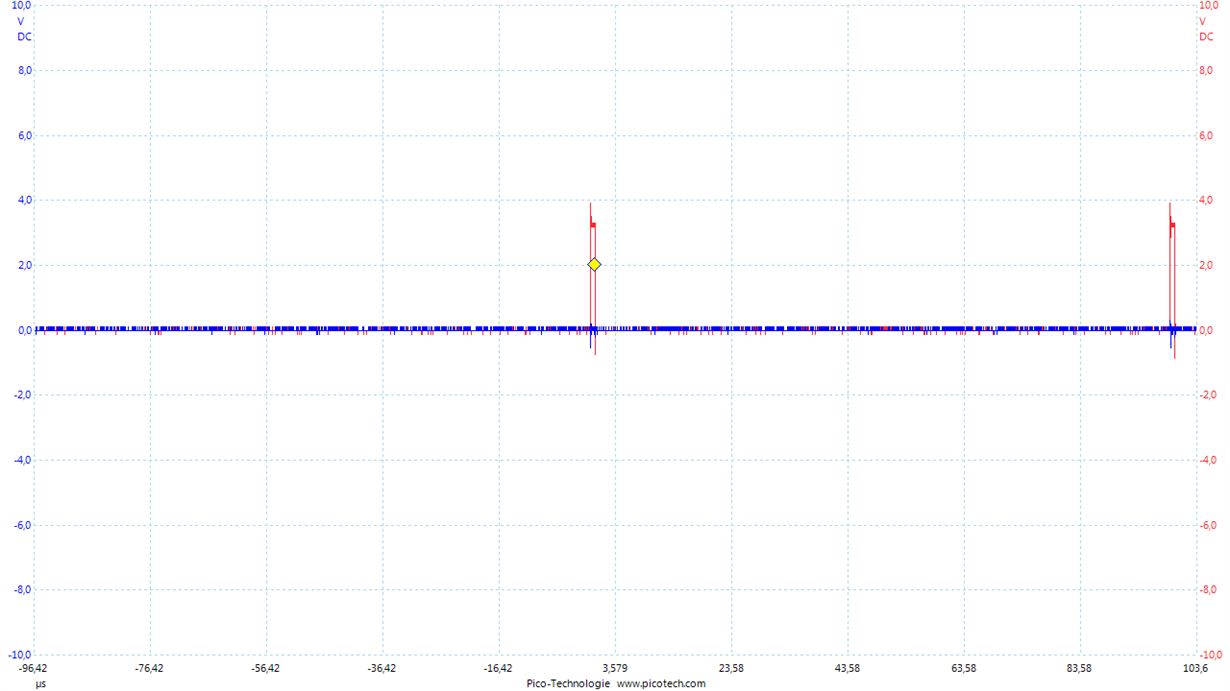

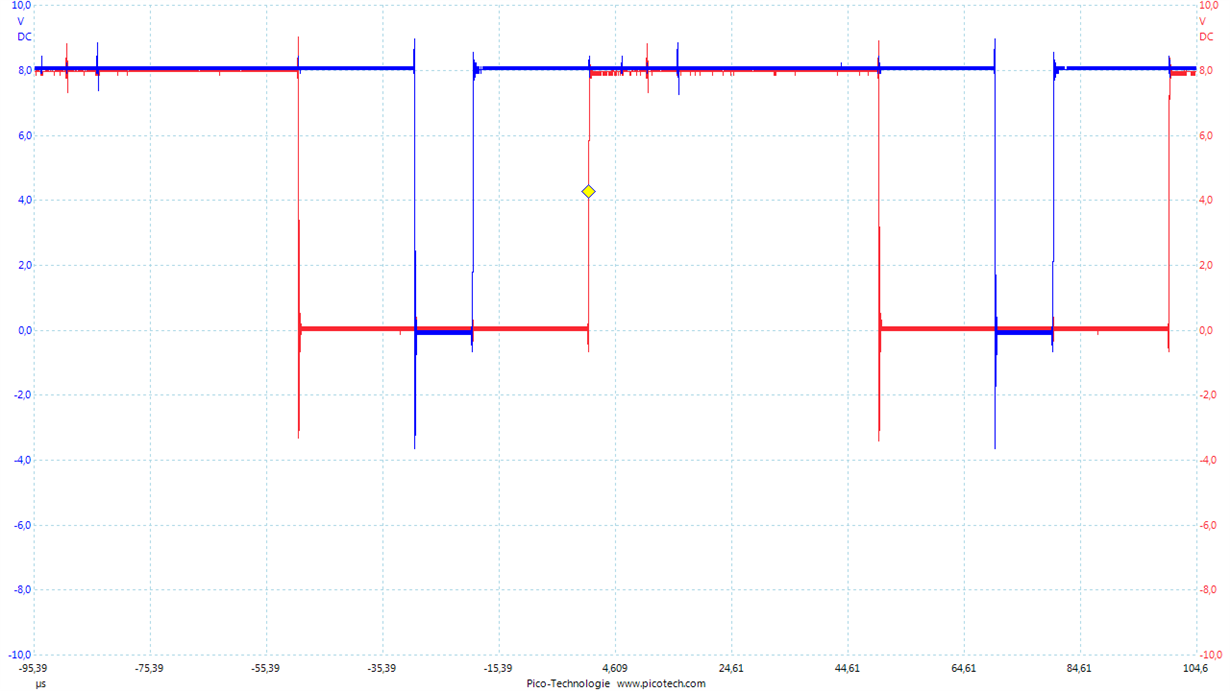

If I assign the following values by the debugger

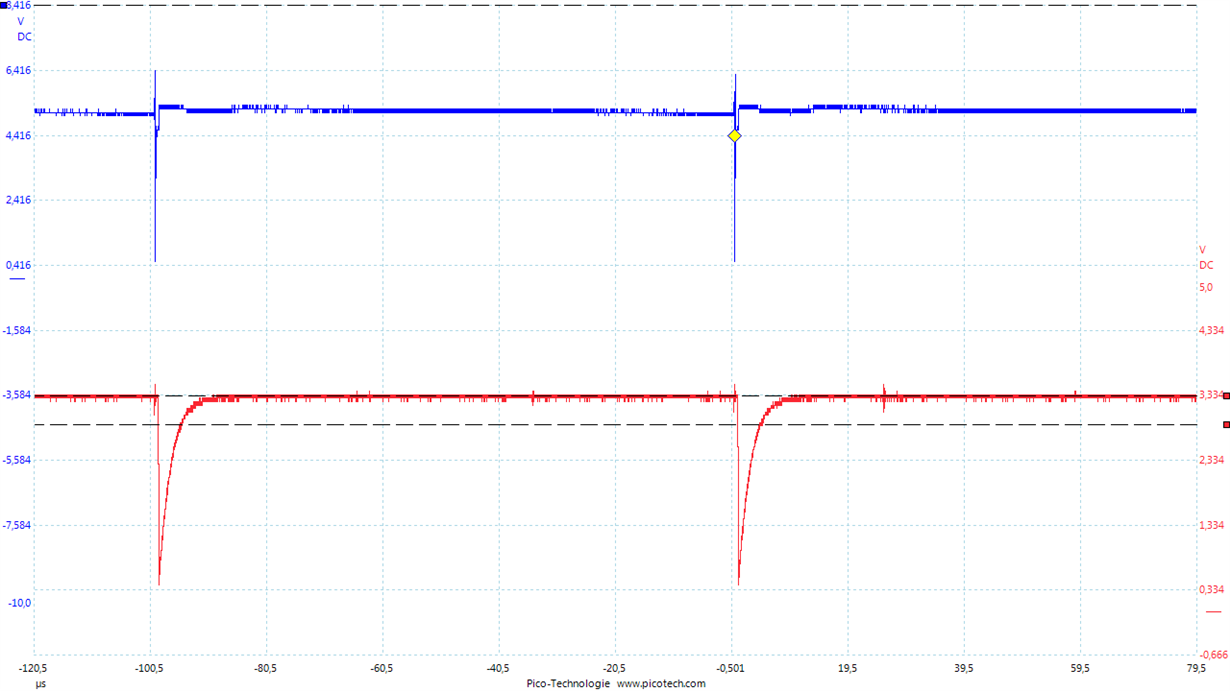

dutyCycle1 = 0.0 (red line)

dutyCycle2 = 0.4, (blue line)

and measure the output potential of the corresponding half bridges, the behaviour is correct and as expected:

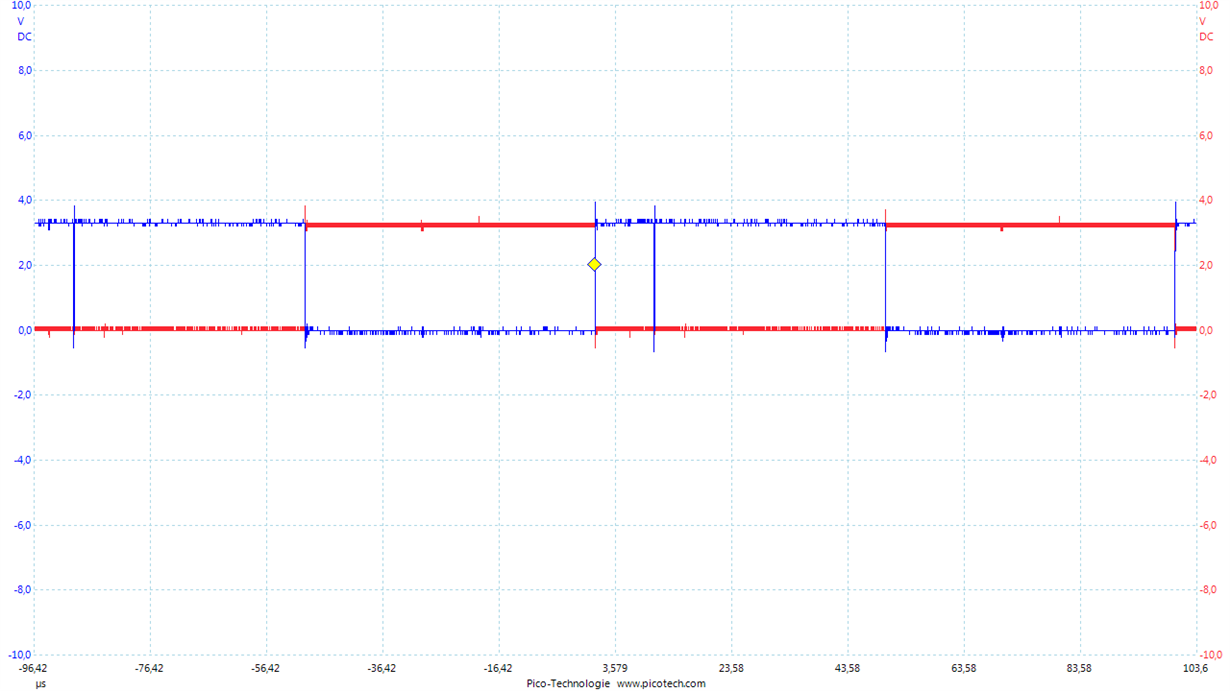

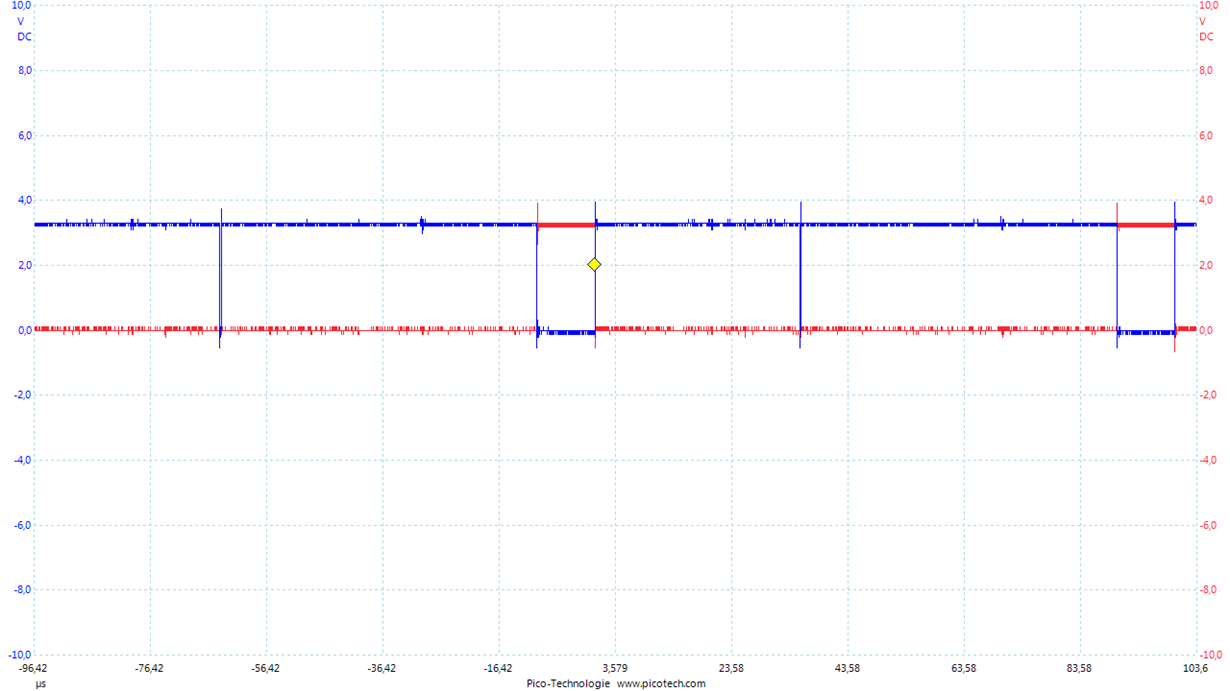

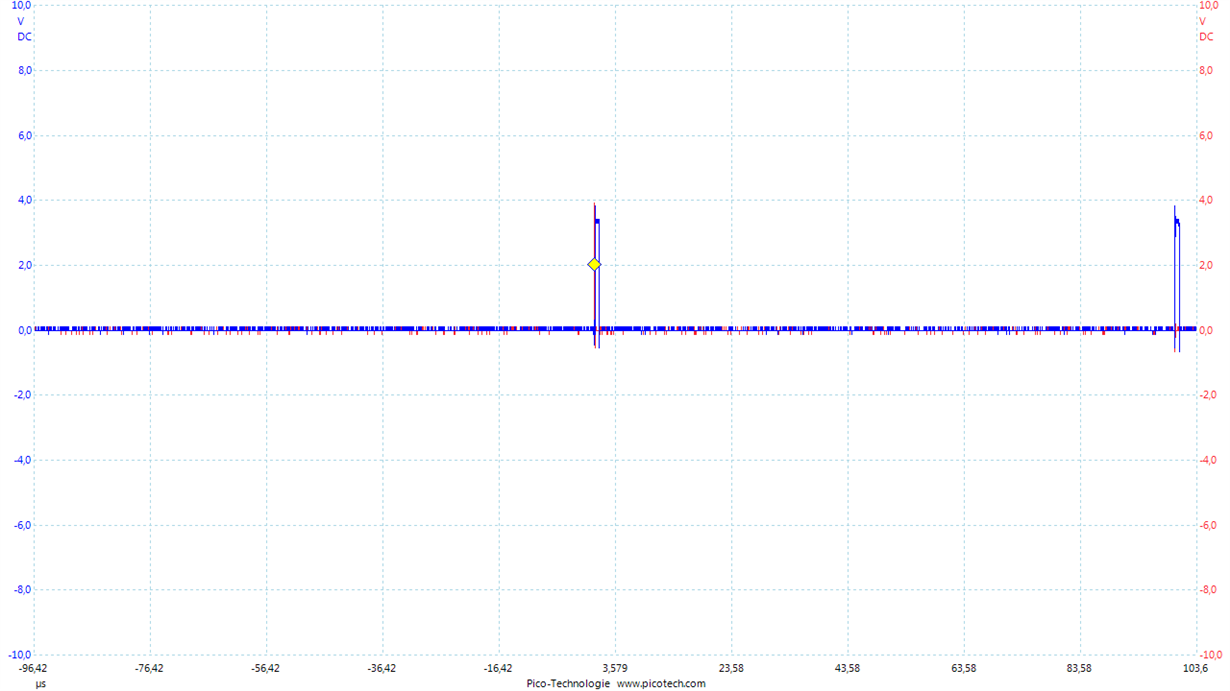

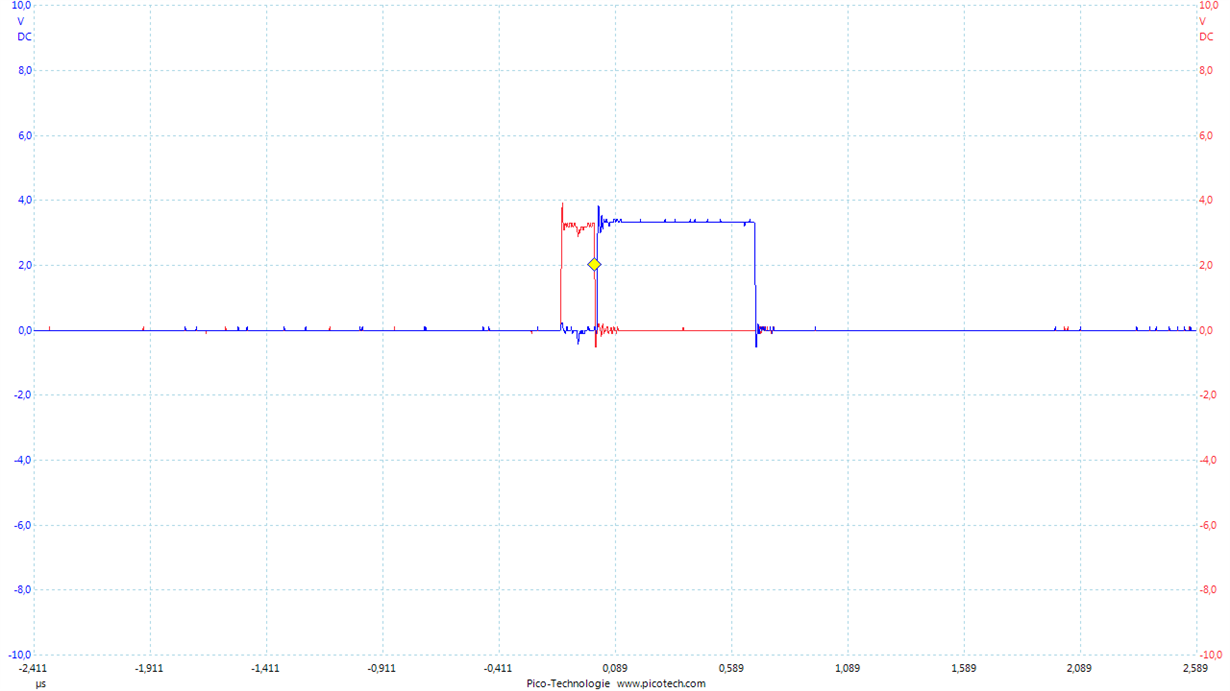

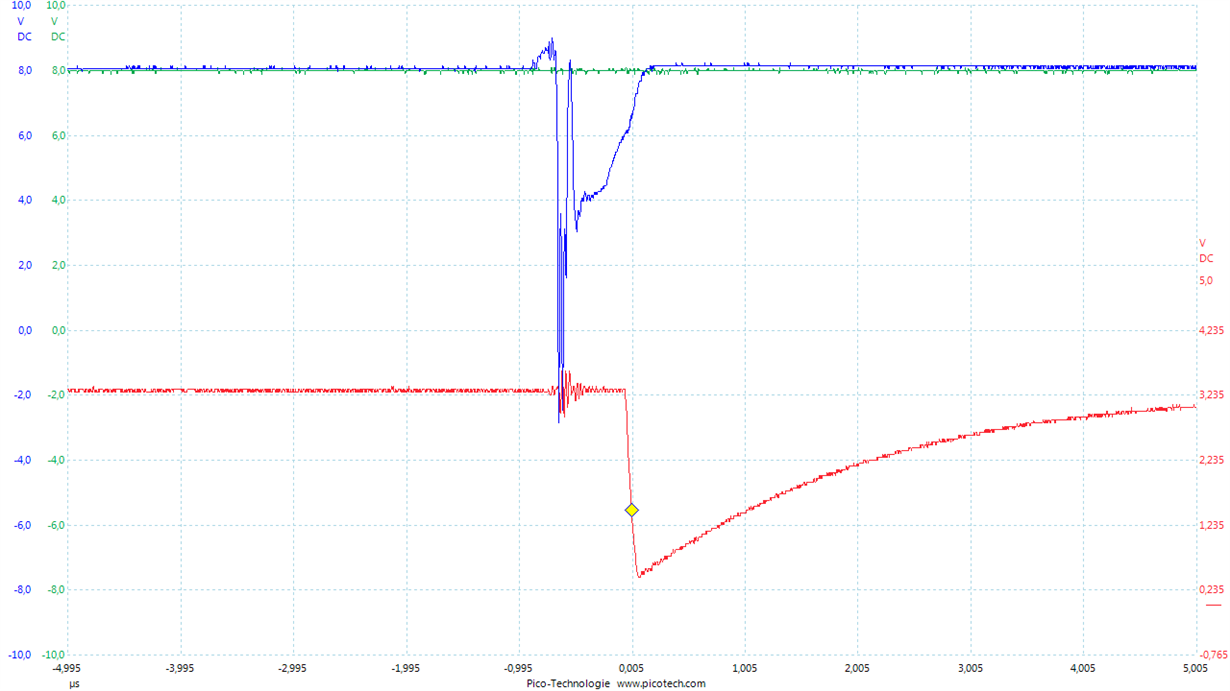

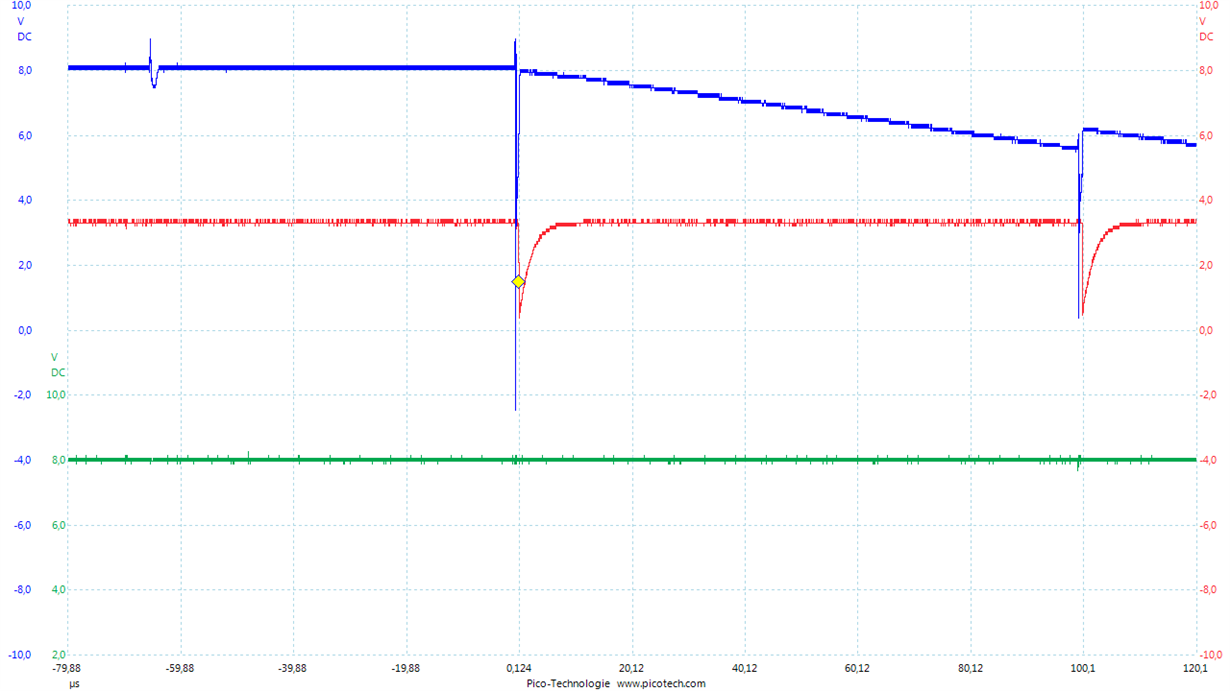

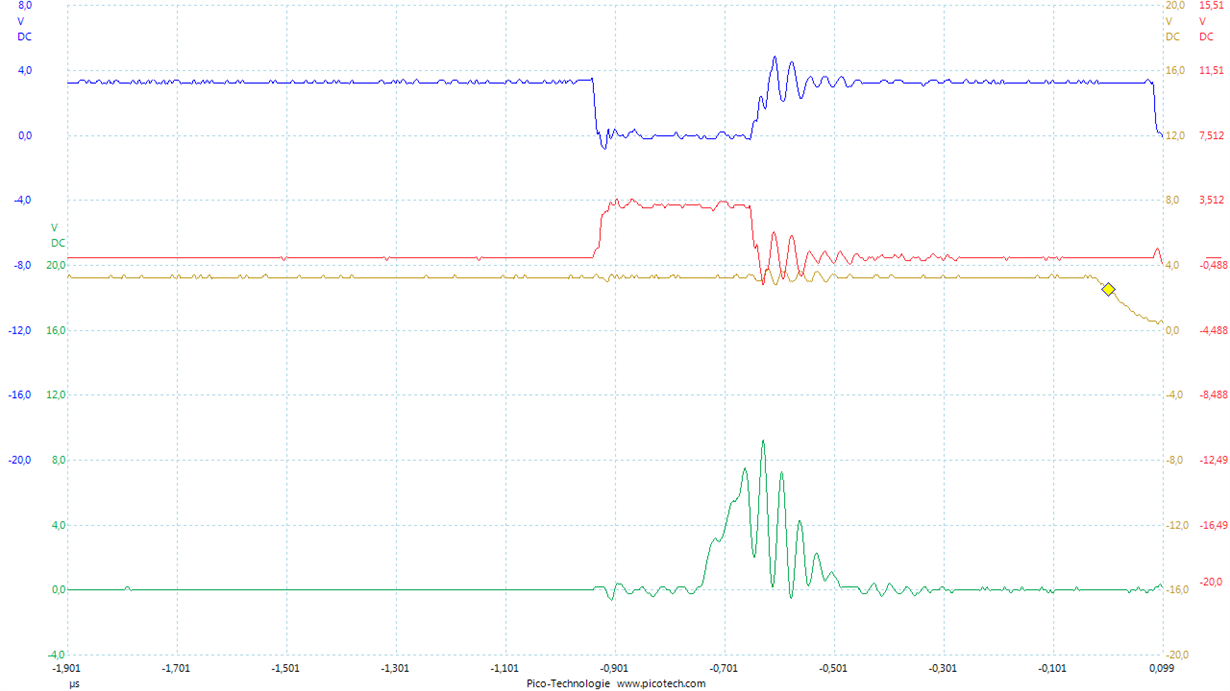

However, if the value dutyCycle2 is changed to

dutyCycle2 = 0.497

I observe an erroneous behaviour (output voltage of half bridge 1 is permanently low and the output of half bridge 2 is permanently high):

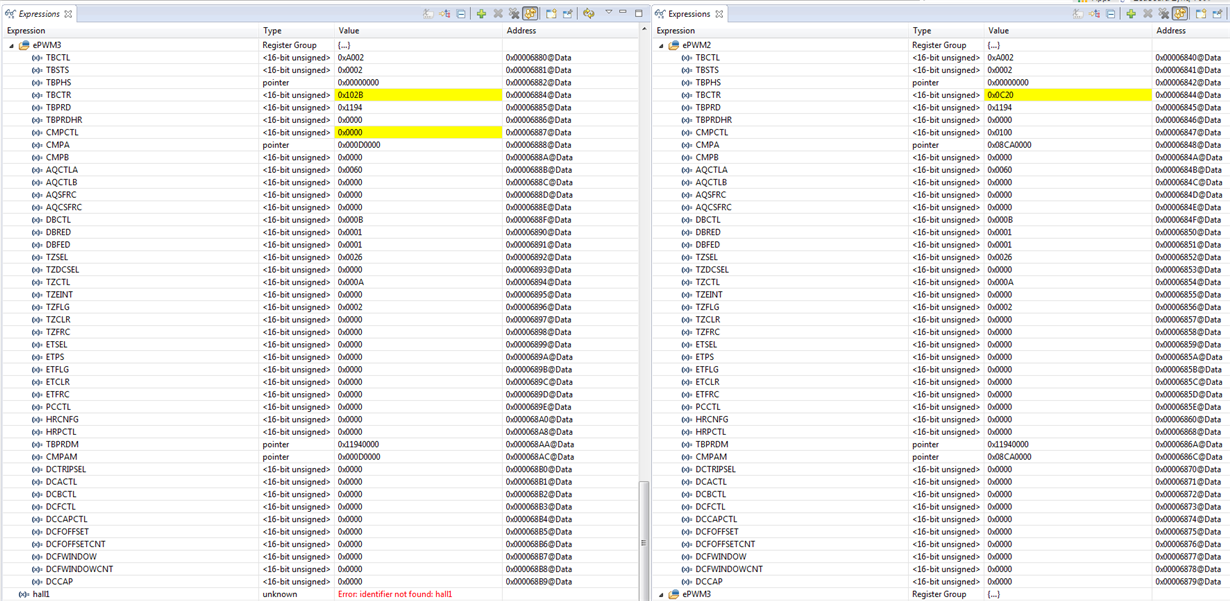

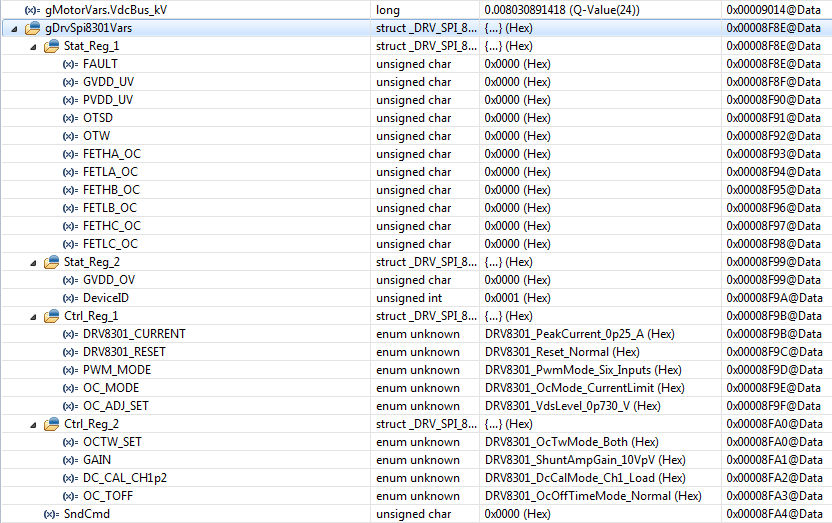

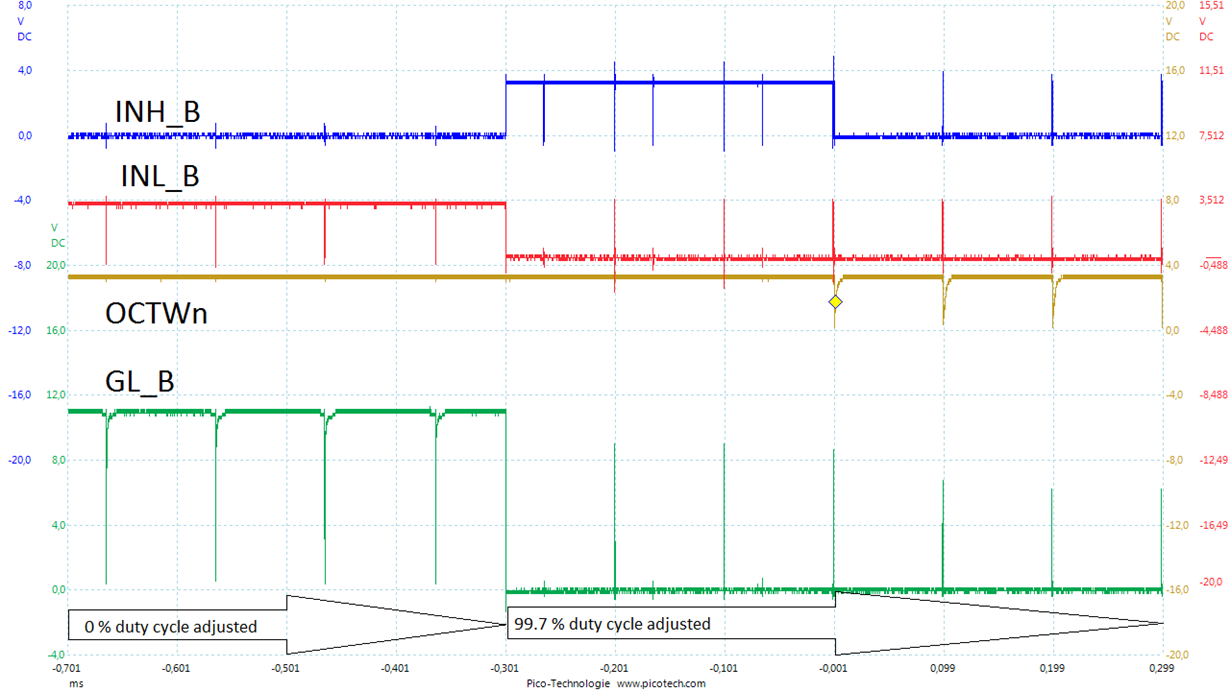

Please find the content of the ePWM registers (ePWM2 corresponds to half bridge 1 and ePWM3 corresponds to half bridge 2) below:

Why does the duty cycle assigned to half bridge 2 affect the (measured) duty cycle of half bridge 1?

Kind regards,

Oliver