Other Parts Discussed in Thread: TINA-TI

I have a similar problem as in earlier post on this forum: "DRV120 ROSC resistor change" (e2e.ti.com/support/applications/motor_drivers/f/38/t/529326 ), Unfortunately the discussion turns private in the end so there is no solution available...

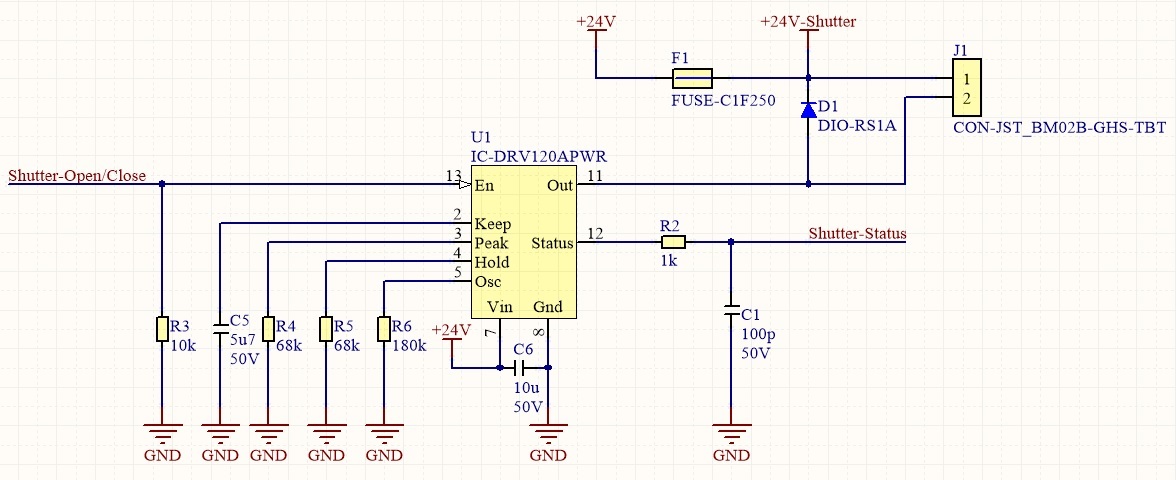

Anyway, I'm driving a 24V 100mH solenoid that requires 170mA start current and 85mA hold current with DRV120 but I can't get it working so that it wouldn't sound very annoying. I have tried multiple different resistor values for all the peak, hold and osc settings without getting it work properly. Sometimes the PWM turns very unstable and sometimes it's a lot lower than it is supposed to be. For example with 180k Rosc the frequency should be according to datasheet over 22kHz but it actually is when measured 10,5kHz (Other settings Rhold 68k and Rpeak 68k).

Any idea what is causing this?