I am having problems determining the external values for a DRV110 application.

I am trying to control a DC solenoid for a valve. The solenoid is rated for 7 watts @ 24V. Measuring the coil with a meter indicates approximately 87 ohms.

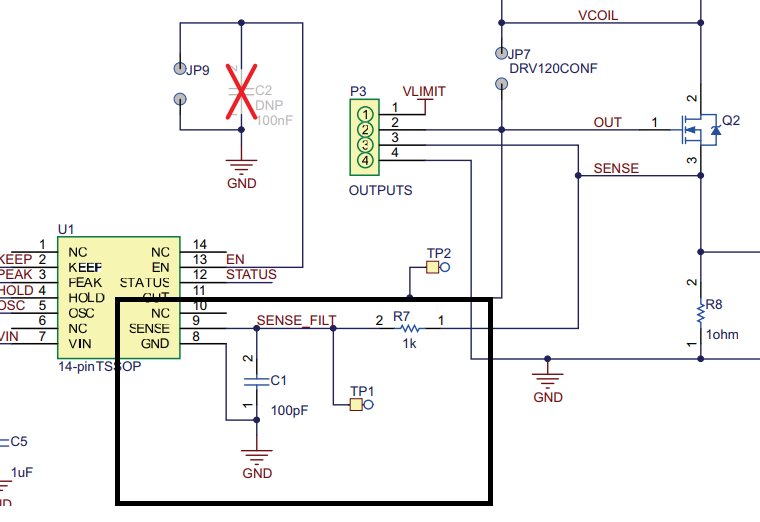

I am using a 1 ohm sense resistor and powering device from the same +24V supply which drives the solenoid. I am using the same FET as used in your reference design, STD1NK60, in a DPAK.

My first issue is with determining the series resistor for the supply voltage to the DRV110. I currently have a 1K resistor, however, I see ripple on the VIN pin of the device when the device is in the hold mode. Is this ok?

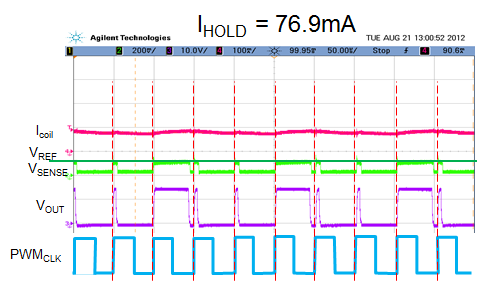

For testing purposes, I went with the default values of ipeak and ihold by using 0 ohm resistors at rpeak and rhold. When I enable the device, I here the solenoid engage, and the DRV110 switches over to the hold mode. The solenoid remains engaged, but if I look at the gate of the FET, I see a somewhat erratic waveform. I would of expected to see a waveform with a well define duty cycle, but I do not. The duty cycle is constantly changing with no apparent pattern. Is this normal?

I read in some other threads that there is a spreadsheet available for helping determine the proper values for this device. How do I obtain this spreadsheet.

Thank you, Jim