I am trying to SPI communicate to DRV8703-Q1 and I use following arduino SPI code:

void testSpi()

{

usleep(10);

// SPI WRITE

vspi->beginTransaction(SPISettings(spiClk, MSBFIRST, SPI_MODE0));

//byte stuff = 0b11001100;

//hspi->transfer(stuff);

digitalWrite(SS1, LOW);

toTransfer = 0b11001100 << 8;

toTransfer |= 0b11001100 ;

vspi->transfer16(toTransfer);

digitalWrite(SS1, HIGH);

vspi->endTransaction();

usleep(10);

}

I dont get any reply from device.

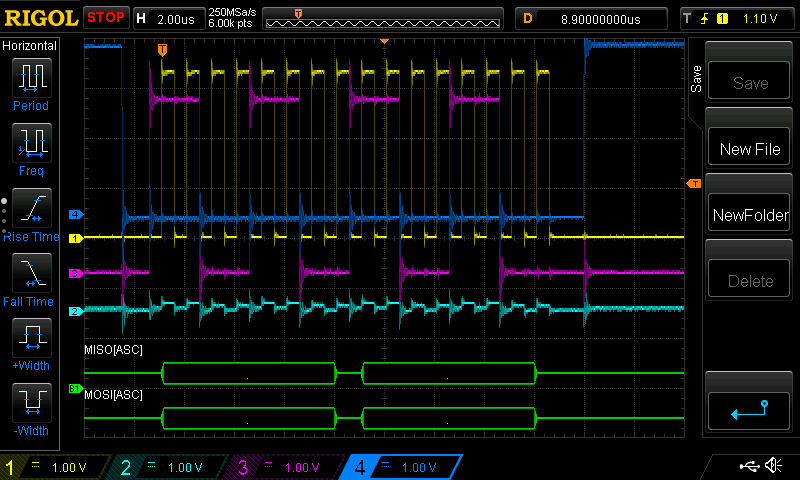

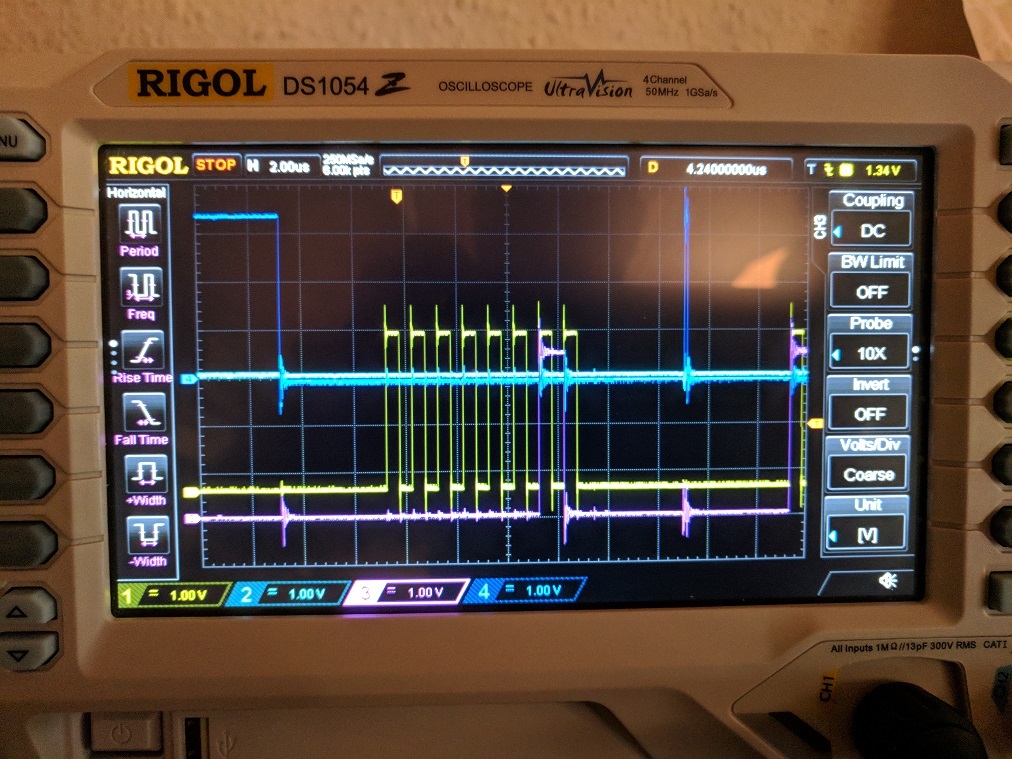

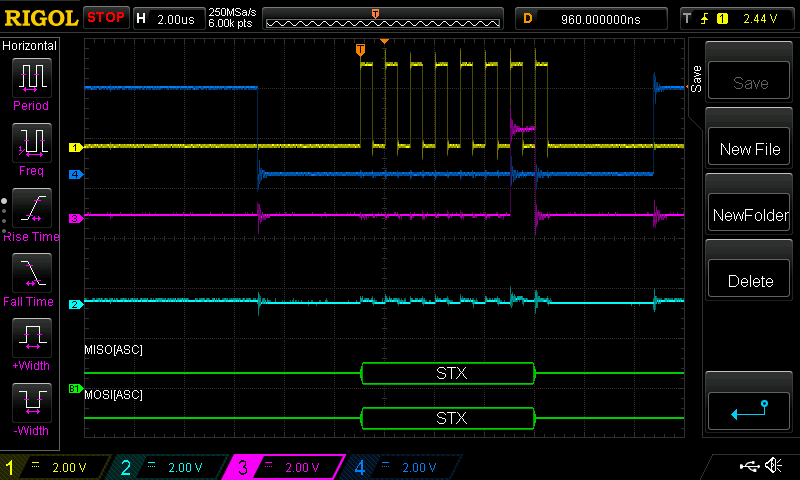

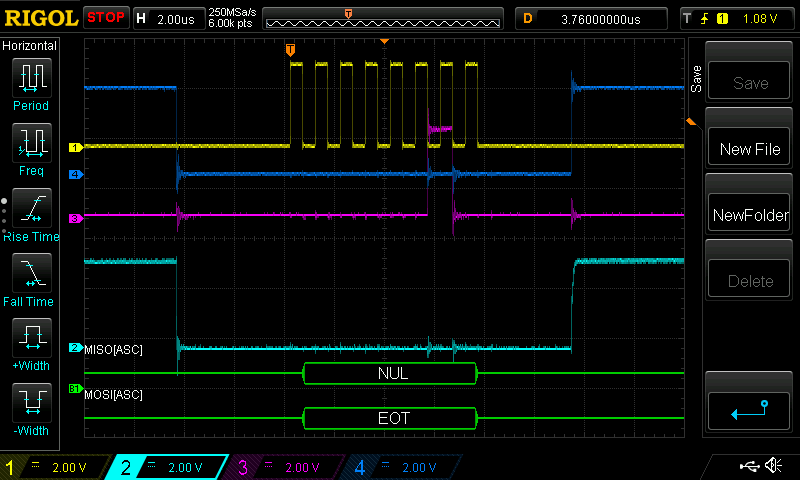

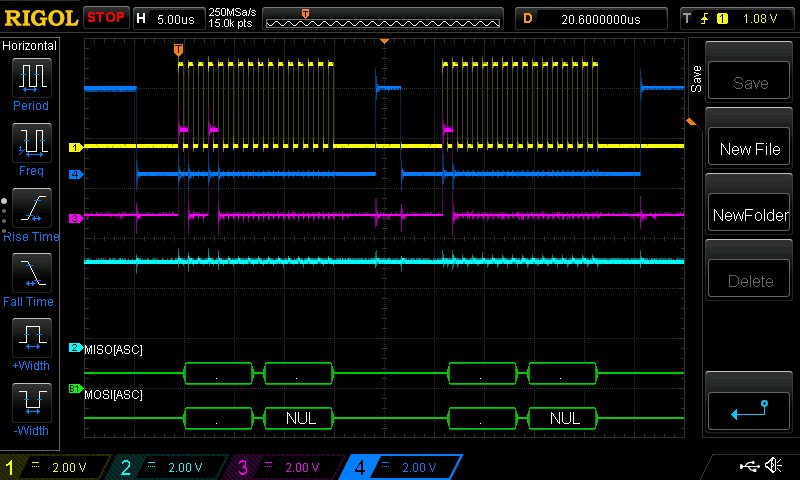

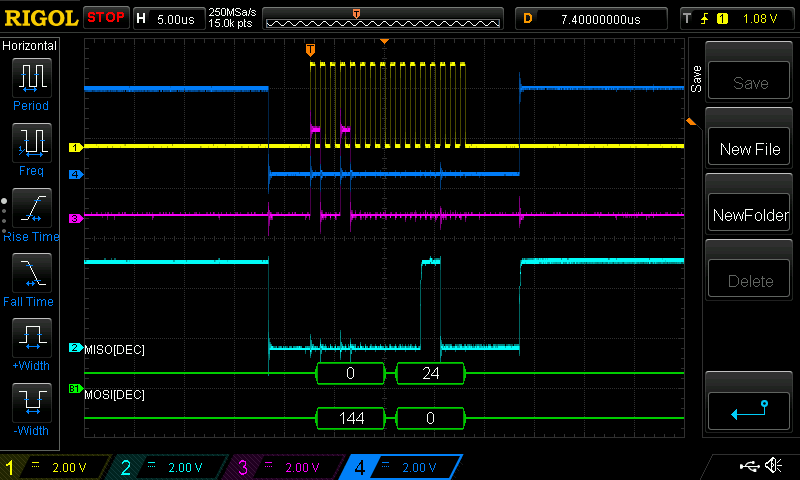

Picture of SPI Communication is attached -

channel1 - yellow : CLK

channel2 - light blue: SS (Slave select)

channel3 - pink: MOSI

channel4 - dark blue: MISO

Wht could be the problem? Any idea how to troubleshoot further?

regards